Kurs_Rab

.pdf

10

димо осуществлять с двойной точностью, что существенно снижает быстродействие.

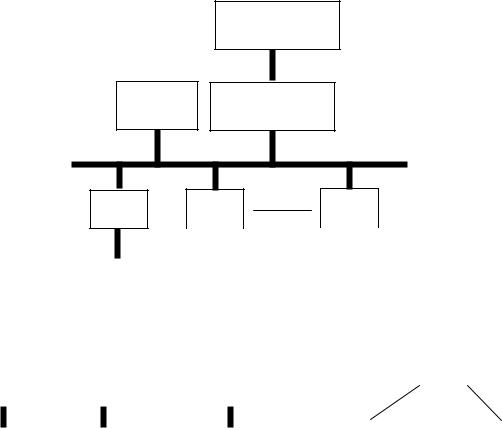

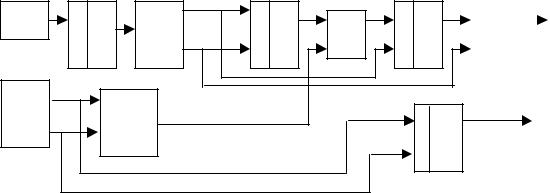

В развитых системах автоматизации технологических процессов различают несколько уровней управления. В зависимости от распределения задач управление электроприводами может осуществляться с помощью одной микроЭВМ (рис.1,а.) через устройства сопряжения (УС). Типичным примером является УЧПУ, в которых контурная обработка осуществляется с помощью двух или трех следящих приводов.

ЭВМ верхнего уровня

Микро- |

Интерфейс |

|

ЭВМ |

||

связи |

||

|

УС1 |

УС2 |

УСn |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Привод 1 |

|

Привод 2 |

|

|

|

|

Привод n |

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

а |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

Микро ЭВМ |

|

|

|

|

|

|

|

|

|

|

|

|

|

Микро ЭВМ |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

МК 1 |

|

|

|

|

|

|

|

|

МКn |

|

||||

|

МК 1 |

|

|

|

МК 2 |

|

|

|

|

|

|

|

МК n |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

УС 1 |

|

|

|

УС 2 |

|

|

|

|

|

|

|

УС n |

|

|

|

УС1 |

|

|

|

|

|

|

|

|

УСn |

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Привод 1 |

|

|

Привод 2 |

|

|

|

Привод n |

|

Привод 1 |

|

|

|

|

|

|

Привод n |

|

||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

в |

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

б |

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

Рис.1. Варианты структур систем автоматизации технологических процессов

Решение более сложных задач в реальном масштабе времени достигается за счет распараллеливания вычислительного процесса. При иерархическом принципе управления задачи нижнего уровня (управления электроприводами) решаются с использованием микроконтроллеров МК (рис.1,б,в). В случае удаленных приводов связь микроЭВМ с МК целесообразно осуществлять через последовательный радиальный интерфейс (рис.1,в).

11

Современные микроконтроллеры могут быть объединены в мультипроцессорную систему с помощью последовательного синхронного интерфейса (SCI) или 8-битного полнодуплексного host-интерфейса.

Для разработки программ реализации алгоритмов используются, как правило, кросс-средства. Отсутствие средств отладки приводит к повышенным требованиям к квалификации разработчика. Один из используемых выходов из этой ситуации основан на разработке эмуляторов и симуляторов, т.е. разработке программного обеспечения, позволяющего производить отладку программ, включая обращения к внутреннему и внешнему пространству памяти МК на персональном компьютере. Более мощные средства отладки содержат отладочные модули, содержащие МК или совместимый по системе команд процессор, память и каналы связи с компьютером. Программное обеспечение в этом случае содержит дополнительные средства: загрузчик и отладчик.

3.1.Принципы построения микропроцессорных систем управления электроприводом. Любые специализированные микропроцессорные системы, предназначенные для локального управления, называют микроконтроллерами (МК). На начальном этапе разработки целесообразно определить основную архитектуру и распределить задачи управления между программными и аппаратными средствами МК. Особенностью цифровых систем управления является обработка и преобразование информации в реальном времени, поэтому особое значение приобретают вопросы разработки развитого интерфейса, связывающего объект управления с вычислительным ядром МК.

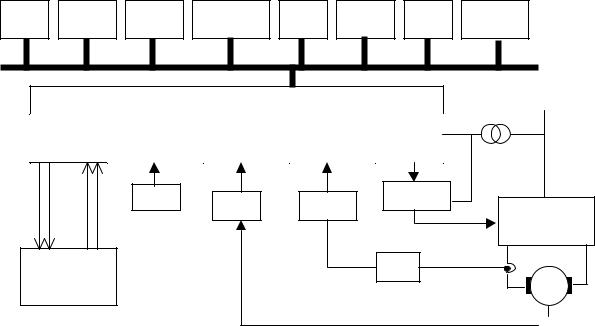

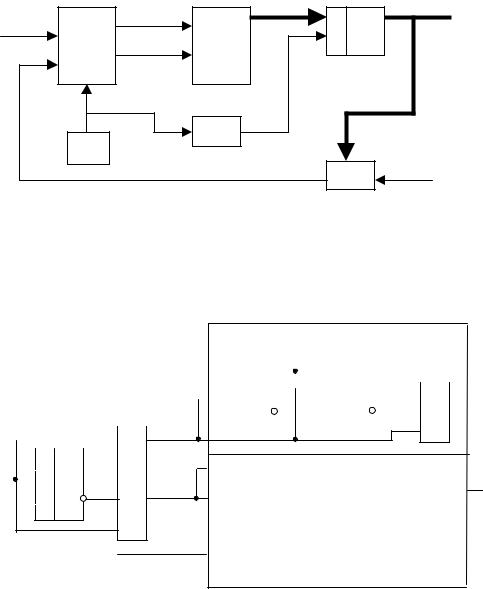

На рис.2 показан один из возможных вариантов структуры микроконтроллера для регулирования скорости двигателя постоянного тока. В МК, как и в любой микропроцессорной системе, можно выделить две части.

Первая часть представляет собой общесистемные блоки: центральный процессор (ЦП), постоянно запоминающее устройство (ПЗУ), оперативно запоминающее устройство (ОЗУ), системный таймер, пульт оператора, последовательный интерфейс.

Во вторую часть входят специализированные интерфейсные модули, с помощью которых осуществляется сопряжение контроллера с объектом управления. Система управления электроприводом двухконтурная с датчиком тока (ДТ) и импульсным датчиком скорости (ИД). Формирование обратных связей осуществляется с помощью аналого-цифрового преобразователя АЦП и преобразователя частота-код ПЧК. Управление тиристорным преобразователем (ТП) осуществляется с помощью цифровой или аналоговой системы импульсно-фазного управления (СИФУ). Для решения задач электроавтоматики используется блок ввода-вывода дискретных сигналов (БВВДИ). Пульт управления (ПУ) в МК представляет собой простейшую клавиатуру и алфавитно-цифровой индикатор, с помощью которого в автономном режиме можно осуществлять отладку и задавать режимы работы.

12

Для расширения вычислительных возможностей в МП систему вводят сопряженный арифметический процессор или аппаратный блок умножения

(БП), например, К1815ВЖ1, К1802ВР2 [7,1].

ЦП ПЗУ ОЗУ Таймер БП ПК |

ПУ ИРПС |

Интерфейс привода |

БВВДИ Задатчика Датчика Датчика СИФУ |

|

||

скорости |

скорости |

тока |

|

|

|

||

ЦЗС |

ПЧК |

СИФУ |

|

|

АЦП |

ТП |

|

|

|

|

|

Электро- |

|

ДT |

|

автоматика |

|

|

|

|

|

|

|

ИД Рис. 2. Структурная схема МК для регулирования скорости электродвигателя

ИД Рис. 2. Структурная схема МК для регулирования скорости электродвигателя

Структура МП системы практически повторяет структуру аналоговой системы управления электроприводом. Основные отличия состоят лишь в дополнительных аналого-цифровых и цифро-аналоговых преобразованиях и в процессе реализации регуляторов скорости и тока. При достаточной вычислительной мощности могут быть использованы другие подходы к принципам построения МП системы, например, токовый контур может быть реализован чисто программным способом в виде прогнозирующей модели (наблюдателя). Это позволяет достаточно просто решить задачи обеспечения необходимой динамики контура тока и токоограничение. Дополнительные преимущества при этом связаны с формированием сигнала обратной связи в области прерывистых токов. Известно, что в данной области целесообразно измерять среднее значение тока [6].

В современных системах управления реализация подобной структуры возможна с использованием более современных компонентов, например, связки микроконтроллера общего применения и специализированного сигнального процессора.

3.2. Интерфейс внешних устройств. Под интерфейсом понимается совокупность программных и аппаратных средств, предназначенных для обмена информацией между ЦП и внешним устройством. Обмен информацией ЦП с внешним устройствами может осуществляется программным способом или по прерыванию. В соответствии с этим различают активные и пассивные источники (приемники) данных.

13

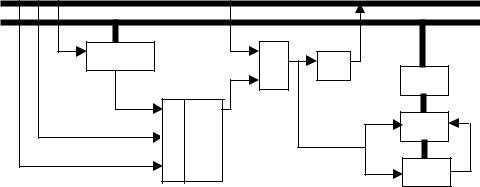

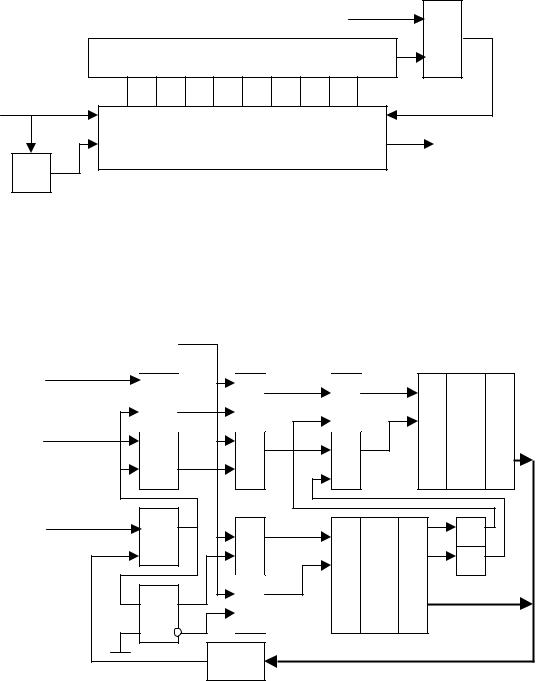

Структура пассивного источника данных показана на рис.3. каждому пассивному устройству отведен конкретный адрес в поле адресов внешних устройств. В цикле ввод:

активное устройство (ЦП) выставляет на шину адреса-данных ШАД код адреса и вырабатывает сигнал ВУ, если адрес относится к внешним устройст-

вам ( 160000 – 177777 );

пассивное устройство с помощью дешифратора адреса ДША распознает один из адресов указанного поля, соответствующий конкретному физическому устройству; после установки адреса на ШАД формируется синхроимпульс адреса (СИА),

по которому производится фиксация выбранного адреса в триггере Т пассивного устройства; ЦП снимает адрес и вырабатывает на шине управления ШУ сигнал ВВОД,

сигнализируя о том, что он готов принять данные от пассивного устройства; при совпадении сигнала ВВОД с единицей в триггере Т выбранного устройства на выходе схемы И формируется сигнал ЧТЕНИЕ, по которому данные буферного регистра БР функционального преобразователя ФП через шинные формирователи ШФ подаются на ШАД;

пассивное устройство, спустя задержку (элемент D), вырабатывает сигнал СИП ( синхроимпульс пассивного устройства ), информирующий процессор о том, что данные находятся на ШАД; ЦП принимает сигнал СИП, принимает данные, снимает сигнал ВВОД;

пассивное устройство снимает сигнал СИП, завершая операцию передачи данных; ЦП снимает сигнал СИА, завершая тем самым цикл ВВОД.

Временные диаграммы показаны в [8]. Цикл ВЫВОД осуществляется практически аналогично и отличается лишь тем, что по сигналу ВЫВОД данные заносятся в БР приемника. Для исключения неоднозначности считывания информации на время сигнала ВВОД целесообразно блокировать сигнал запись данных (Зп.) в буферный регистр функционального преобразователя.

ШУ |

|

|

|

|

ША |

|

Чт. |

СИП |

|

ДША |

И |

|||

|

D |

|||

ВУ |

|

|

||

|

|

|

ШФ |

|

D |

T |

|

Зп. |

|

СИА |

|

БР |

||

C |

|

|

||

|

|

|

||

Сброс |

|

|

|

|

R |

|

|

ФП |

|

|

|

|

||

Рис. 3. Структура пассивного источника данных |

||||

Рассмотренные принципы построения и используемая терминология наиболее подходит к процессорам серии 1801ВМ1,1801ВМ2. Разработка сис-

14

темы на современной элементной базе может быть ориентирована или на специализированные МК, специально разработанные для управления электроприводами, или на совокупности 8- разрядных и специализированных МК.

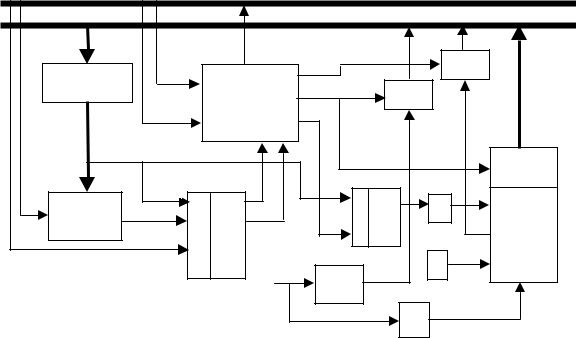

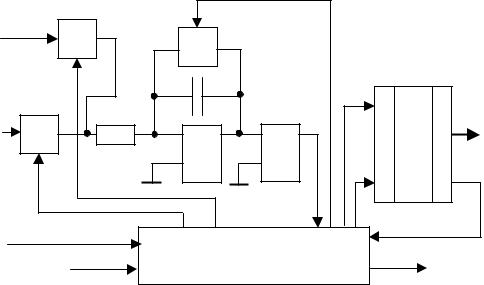

Организация интерфейса аналого-цифрового преобразователя АЦП поразрядного уравновешивания показана на рис. 4. Цикл работы АЦП начинается с приходом сигнала Запуск, а его завершение ¾ сигналом Готовность. Для обмена информацией интерфейс АЦП должен содержать регистр состояния РС и регистр данных РД. При использовании АЦП типа К572ПА1 регистр данных и буферные вентили являются внутренними элементами, обеспечивающими возможность работы с шиной без промежуточных элементов. Для минимизации схемы, в данном случае, целесообразно использовать однонаправленные шинные усилители (приемник, передатчик) типа К155ЛН6, К555ИП2. При переходе шинных формирователей ШФ в третье состояние за счет нагрузочных резисторов на линии шины создается сигнал, соответствующий логической 1, который будет принят ЦП как 0. Следовательно, по шине можно передавать только один разряд, например 7-й, соответствующий биту Готовность. Информация по шине, как правило, передается низким уровнем напряжения с двойной инверсией в канале передачи от ЦП к приемнику (источнику).

ШУ |

|

|

|

|

|

|

|

|

ШАД |

|

|

|

|

|

|

|

|

|

Приемники |

Ввод |

|

Дешифратор |

Чт.1 |

|

|

ШФ |

|

|

Чт.2 |

|

|

|

|||

|

|

|

|

строба |

ШФ |

|

|

|

|

|

|

|

запись\чтение |

|

|

|

|

|

|

Вывод |

|

Зп.1 |

|

|

|

|

|

|

АД00 |

|

|

|

|

|

Передат- |

|

АД02-12 |

|

|

|

|

|

|

|

|

|

|

|

|

РС |

|

чики |

|

|

|

АД01 |

|

|

|

|

|

|

ВУ |

|

D0 |

|

|

D T |

|

|

|

Селектор |

|

РА |

|

Ф |

Запуск |

|||

|

|

|

||||||

|

адреса |

|

D1 |

|

|

C |

|

|

|

|

СИА |

|

|

|

|

Готов |

|

|

|

C |

|

|

|

|

||

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

Ux |

|

ДА15 |

Г |

АЦП |

|

|

|

|

НО |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

В |

|

|

|

Рис. 4. Интерфейс АЦП поразрядного уравновешивания |

|||||||

Спомощью селектора адреса выделяется группа адресов, относящихся

кблоку или интерфейсу привода. При этом последовательность адресов будет отличаться только младшими разрядами, фиксируемыми в регистре адреса РА. Информационным разрядом, позволяющим выделить два адреса из группы, например, РС – 167640 и РД – 167642, является разряд АД01. Признак ВУ эквивалентен 3-м старшим разрядам адреса внешних устройств. Разряд АД00 используется совместно с сигналом БАЙТ при необходимости об-

15

работки байтовой информации. Полный цикл обращения к АЦП содержит: запись в 0-разряд РС ( триггер Т ) признака Пуск, по которому через формирователь импульсов Ф осуществляется запуск АЦП; опрос разряда Готовность РС ( выхода Готов АЦП ); ввод данных с АЦП; сброс признака Пуск.

В соответствии с данным циклом с помощью дешифратора строба по сигналам Вывод, Ввод последовательно формируются сигналы Зп.1, Чт.1, Чт.2 и Зп.1. Возможна и другая организация интерфейса, например с принудительной установкой триггера Т в нулевое состояние по сигналу Готовность АЦП. В этом случае нет необходимости в повторной установке 0– разряда РС. На вход АЦП с помощью выпрямителя В подается модуль входного напряжения Ux, а его знак формируется с помощью нуль органа НО. Более детально согласование входных напряжений и организация АЦП К572ПА1 рассмотрены в [8,9]. Организация интерфейса контроллера внешних устройств подробно рассмотрены в [5].

3.3. Аналого-цифровые преобразователи.В цифровых системах управ-

ления широко используют преобразования код-аналог и аналог-код [6, 11]. Преобразователи частоты в код ПЧК, используемые для измерения частоты вращения электродвигателя, известны двух типов: ПЧК, основанные на подсчете числа импульсов входной частоты Fвх за фиксированное время Т и ПЧК, основанные на измерении периода Твх = 1\Fвх.

ПЧК первого типа [6, 11], называемые преобразователями с непосредственным отсчетом частоты (рис. 5), вырабатывают код:

Nвых = n × T × Fдв = n × N × Fдв / FT , |

|

|

где n – число импульсов, вырабатываемых |

за один оборот |

двигателя; |

Fдв = ω / 2π частота вращения двигателя. |

|

|

Интервал измерения T = N / FT , где N – |

число импульсов, |

формируют |

с помощью счетчика С1, на вход которого поступают импульсы с частотой FT от генератора тактовых импульсов ГТИ.

ГТИ |

С |

Дш |

S T1 |

С |

С2 |

|

|

С1 |

|

И |

|

|

|

|

R |

R |

|

ИД |

|

ИЛИ |

|

|

|

|

|

|

|

S T2 |

|

|

|

|

|

|

|

|

|

|

|

|

R |

D |

БР |

|

Nвых |

С |

|

|

|

|

|

||

|

|

|

|

|

|

|

|

Признак

напр. движ.

Рис.5. ПЧК с непосредственным отсчетом частоты

С помощью дешифратора ДШ формируются сигналы Начало цикла и Конец цикла, интервал времени между которыми равен периоду Т. В начале цикла осуществляется сброс счетчика С2 в нулевое состояние и установка

16

триггера Т1 в единичное состояние. На вход С2 через элемент И начинают поступать импульсы от частотного датчика скорости. Счет импульсов прекращается в момент формирования сигнала Конец цикла. При этом осуществляется установка Т1 в исходное состояние и перезапись содержимого счетчика С2 в буферный регистр БР. Признак направления движения, соответствующий знаковому разряду выходного числа Nвых , формируется с помощью

триггера Т2. Импульсный (частотный) датчик скорости ИД формирует в зависимости от направления вращения импульсы только по одному из каналов. Серийные фотоэлектрические импульсы датчика содержат также синхроканал, по которому вырабатывается один импульс на оборот.

При построении ПЧК второго типа [6, 11] счетчик С2 заполняется импульсами высокой частоты FT на протяжении k периодов Fвх так, что за-

фиксированный буферным регистром код

Nвых = 2πkFT /(ωn)

обратнопропорционален измеряемой частоте вращения. Для нахождения величины пропорциональной частоте вращения необходима операция деления или обработка данных с помощью ПЗУ, в котором зашита гиперболическая зависимость. Разрешающая способность данного преобразователя увеличивается на низких частотах. Однако при вычислении Nвых приходится опери-

ровать с большим числом разрядов. Поэтому может оказаться целесообразным введение нескольких диапазонов измерения, каждому из которых соответствуют свои значения k и FT . Ввод диапазонов или переход от одного

способа измерения к другому может быть осуществлен под управлением ЭВМ. В качестве интерфейсных БИС для реализации рассмотренных преобразователей могут быть использованы программно-управляемые таймеры типа К580ВИ53.

Технологические погрешности ИД и сопряжения его с двигателем приводят к неравномерности следования импульсов, что вызывает эффект, равносильный пульсациям напряжения тахогенератора. Уменьшение данной погрешности может быть достигнуто за счет усреднения показания ПЧК на нескольких интервалах измерения. В работе [6] описан интеграционный ПЧК, принцип действия которого основан на реализации рекуррентных соотношений, описывающих работу дискретного интегратора с параметрической обратной связью. Так же описаны некоторые недостатки приведенной схемы ПЧК. Структурная схема ПЧК такого типа показана на рис. 6. ПЧК содержит блок управления, реализованный на основе генератора импульсов ГИ и делителя частоты ДЧ, с помощью которого формируется шаг квантования, равный периоду сигналу перезаписи информации в буферный регистр БР. Для разделения импульсных последовательностей, поступающих на входы реверсивного счетчика РС, используется блок синхронизации БС. Регулируемый делитель частоты РДЧ, включенный в цепь обратной связи интегратора РС, выполняет функции умножителя сигналов. Процесс уравновешивания входной частоты Fвх частотой обратной связи Fд на k -м интервале времени мо-

жет быть описан следующим образом:

17

N[k ] = N[k -1] + ÑN[k -1] = N[k -1] + T (Fвх - FT N[k -1]) ,

где период T = K / FЭТ определяется коэффициентом деления K делителя частоты ДЧ и эталонной частотой ГИ, а частота на выходе РДЧ равна

Fд = FT N[k -1] .

Дискретный интегратор может быть реализован на базе реверсивного счетчика типа К155ИЕ7, в качестве регулируемого делителя частоты можно использовать счетчик К155ИЕ8.

|

Fв |

+1 РС |

|

D |

БР |

N |

|

БР |

|

С |

|

||

|

|

|

|

|||

|

|

-1 |

|

|

|

|

. |

|

FЭ |

|

|

|

|

|

ДЧ |

Зап |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

ГИ |

|

|

|

|

|

|

|

Fд |

РЧД |

Fт |

|

|

|

|

|

|

||

|

Рис.6. Функциональная схема итерационного ПЧК |

|

||||

Принципиальная схема блока синхронизации показана на рис. 7. Она содержит распределитель импульсных последовательностей (элементы D0, D1) и два канала выделения переднего фронта импульсовFвх и Fд.

|

|

|

|

|

|

|

|

|

|

|

|

|

Канал 1 |

||||

Fвх |

|

|

|

|

D |

Т |

|

|

J |

Т |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

С |

D3 |

|

|

C |

D4 |

|

|

& |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

K |

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

D5 |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

F |

|

|

|

& |

|||||

|

|

|

|

|

|||||

ЭТ |

|

Т |

|

|

D2 |

||||

|

C |

|

|||||||

|

|

|

|

||||||

|

|

|

|

|

|

||||

|

|

|

|

|

|

||||

&

D1

D2

Fд

Канал 2

Рис. 7. Схема блока синхронизации

С помощью D-триггера осуществляется привязка (синхронизация) входных импульсов, а с помощью JK-триггера и трехвходового элемента И – выделение единичного импульса по переднему фронту входного импульса.

К наиболее распространенным ПНК, используемых в цифровых электроприводах, относятся преобразователи поразрядного управления, следящие и интегрирующие. Большинство схем ПНК поразрядного уравновешивания построено на базе регистров последовательного приближения РПП типа

18

К155ИР17. Запуск ПНК поразрядного уравновешивания (рис. 8) осуществляется сигналом Пуск, который устанавливает 1 в старшем разряде РПП и нули в остальных разрядах. Импульсные последовательности генератора ГИ разделяются на две фазы. На первой фазе производится анализ входного напряжения. Компаратор К сравнивает напряжение Ux с весом текущего разряда и свое решение 1 или 0 передает на вход D1 РПП. Если решение 0, разряд устанавливается в 0. В противном случае разряд устанавливается в 1. Во второй фазе 1 записывается в следующий разряд и ЦАП выдает вес следующего разряда с учетом предыдущего. Таким образом поразрядные решения компаратора в виде последовательностей 1 и 0 накапливаются на выходах РПП. После анализа всех разрядов на выходе РПП формируется сигнал Конец преобразования.

|

|

|

Ux |

K |

|

|

|

|

|

Цифро– аналоговый преобразователь |

|

|||

Пуск |

|

|

|

|

S |

Регистр последовательных |

Конец |

||

С |

приближений |

QCC |

||

|

|

|

|

преобразований |

ГИ |

|

|

|

|

Рис. 8. Функциональная схема ПНК поразрядного уравновешивания |

||||

Следящие ПНК относятся к классу наиболее быстродействующих пре- |

||||

образователей [9]. Для уменьшения времени преобразования следящие ПНК |

||||

строят по схеме двухступенчатого отсчета [6]. В ПНК (рис. 9) используется |

||||

счетчик грубого отсчета СТ1 и счетчик СТ2 для точного. |

||||

|

FТ |

|

|

|

+Uэ/2 |

|

|

|

|

|

СУ |

& |

1 |

+1 CT1 |

-Uэ/2 |

А3 |

|

|

- 1 |

|

СУ |

& |

1 |

|

|

А4 |

|

|

|

Ux |

|

|

|

Э1 |

UЦАП |

А1 |

& |

+1 CT2 Р+ |

|

|

Р- |

Э2 |

||

|

|

|

- 1 |

|

|

|

|

|

|

|

СУ |

& |

|

|

|

|

|

|

|

|

А2 |

|

|

|

|

|

ЦАП |

|

|

|

Рис. 9. Схема двухступенчатого следящего ПНК |

|||

19

Входное напряжение сумматора А1 равно разности Ux и Uцап. Эта разность поступает на устройство сравнения СУ, выполненных на компараторах А2, А3 и А4. Вес младшего разряда счетчика грубого отсчета СТ1 составляет Uэ/2 при равенстве разрядов каналов грубого и точного отсчетов. При резком изменении Ux срабатывает компаратор А3 или А4 и уравновешивание входного напряжения осуществляется за счет двух каналов. При медленном изменении Ux работает только один канал точного отсчета. Для исключения наложения импульсов в канале грубого отсчета используются элементы задержки Э1, Э2. Измерение площади или интеграла от мгновенной величины за определенный промежуток времени можно выполнить с помощью АЦП любого типа. Один из наиболее распространенных вариантов преобразователя такого типа показан на рис. 10.

В данном преобразователе [6] полный цикл содержит два такта интегрирования. Первый такт начинается в момент прихода сигнала Пуск. При этом ключ К1 открывается и на вход генератора, собранного на операционном усилителе А1, подается напряжение Ux. Одновременно на вход счетчика СТ начинают поступать импульсы Fт. Процесс заряда продолжается до определенного переполнения счетчика СТ. В момент времени Т = 2n/Fт на интеграторе накопится напряжение

Uи = UxT/Tи,

где Ти – постоянная времени интегратора.

Импульс переполнения вызывает переключение входных цепей интегратора. На его вход через ключ К2 подают эталонное напряжение Uз с полярностью противоположной Ux. Выходное напряжение интегратора начинает изменятся. При этом счетчик СТ, пройдя через нулевое состояние, продолжает счет импульсов.

Ux |

К1 |

К3 |

|

|

|

|

|

||

|

|

|

|

|

|

|

|

C |

|

|

|

R |

С |

СТ |

К2 |

|

|

N |

|

|

-А1 |

НО |

|

|

Uэ |

|

|

||

|

|

+ |

R |

P |

|

|

|

||

Пуск |

|

Устройство управления |

|

|

|

|

|

||

Fт |

|

|

|

Готов |

Рис. 10.Функциональная схема АЦП двойного интегрирования

В конце второго такта напряжение интегратора станет равное нулю, срабатывает устройство сравнения СУ, прекращая счет импульсов. При этом счетчик накапливает число N = T2 Fт, где длительность второго такта равна длительности разряда конденсатора интегратора Т2 = UиTи/Uэ, откуда