- •С.М.Сухман, а.В.Бернов, б.В.Шевкопляс Компоненты телекоммуникационных систем Анализ инженерных решений

- •Isbn 5-7256-0316-4

- •Isbn 5-7256-0316-4 зао ЗелаксПлюс, 2002

- •Предисловие

- •Взаимодействие устройств типа dte/dce

- •Устройства типа dte и dce: сложности терминологии

- •Логический и физический уровни представления сигналов

- •Основные сигналы интерфейса rs-232

- •О сигнале ri

- •Сигналы TxD, clk, TxC, RxD, RxC

- •Взаимодействие устройств в асинхронном режиме

- •Взаимодействие устройств в синхронном режиме

- •Сравнение методов попутной и встречной синхронизации

- •Когда полезно проинвертировать синхросигнал

- •Пары сигналов dtr – dsr и dtr – dcd

- •Сигналы rts и cts

- •Прямое назначение . . .

- •. . . И альтернативное

- •Программное управление потоком данных

- •Трехпроводный вариант интерфейса rs-232

- •Электрические уровни сигналов rs-232

- •Взаимодействие одноименных устройств в асинхронном режиме

- •Варианты сопряжения двух устройств типа dte

- •Пример сопряжения двух устройств типа dce

- •Схемы взаимодействия устройств типа dte и dce в синхронном режиме: типовые решения

- •Вводные замечания

- •Системы с внутренней синхронизацией

- •Системы с внешней синхронизацией

- •Использование модема как устройства типа dte

- •Cистема с двумя последовательно включенными каналами связи

- •Схемы взаимодействия устройств типа dte и dce в синхронном режиме: нестандартные решения

- •Асинхронно-синхронная передача данных между устройствами типа dte и dce

- •Синхронный обмен данными с передачей кадровых меток

- •Повышение быстродействия и расширение функциональных возможностей системы с попутной синхронизацией

- •Объект модернизации – схема передачи пары сигналов TxD – clk

- •Удвоение скорости передачи данных с использованием для их приема положительного и отрицательного фронтов сигнала clk

- •Удвоение скорости передачи данных заменой сигнала clk сигналом разграничения одноименных битов

- •Расширение функциональных возможностей системы с разграничением одноименных битов

- •Создание дополнительного канала связи

- •Использование дополнительного канала связи для разграничения кадров

- •Аппаратное управление потоком данных с использованием пачек сигналов ТхС

- •Цифровая коррекция фазы сигнала от удаленного синхрогенератора

- •Выравнивание фаз передаваемого и принимаемого синхросигналов

- •Передача синхросигнала против течения потока данных

- •Взаимодействие удаленных устройств с непосредственной односторонней передачей синхросигнала по каналу связи

- •Синхронизация передачи данных между удаленными устройствами

- •Вводные замечания

- •Основная задача и ее универсальное решение

- •Проявления проскальзываний синхронизации для разных типов данных или технологий их передачи

- •Источники обновляемой синхронизации

- •Генераторы сигналов высокой точности и стабильности

- •Фазовые помехи

- •Адаптивный фильтр для подавления джиттера – вандера

- •Синхронизация дуплексных каналов

- •Зацикливание синхросигналов

- •Автоматическое предотвращение зацикливания синхросигналов

- •Синхронизация кольцевых структур

- •Отказоустойчивая система синхронизации сети с кольцевой топологией

- •Синхронизация передачи данных: распознавание и обработка кадров или иных структурных единиц

- •Передача полезных данных вместо избыточных битов синхронизации кадра

- •Частичное восстановление кадра при обнаружении проскальзывания

- •Битовые проскальзывания

- •Структура кадра, применяемого в системе мобильной связи gsm

- •Как по возможности сохранить кадр

- •Упрощение системы синхронизации формирователя hdsl-кадров

- •Минимизация длины флага

- •Традиционное решение с использованием многоразрядного флага

- •Использование одноразрядного флага для обозначения начала кадра

- •Вхождение в синхронизацию

- •Потеря и восстановление синхронизации

- •Использование раздробленного флага начала кадра

- •Применение неуникального флагового кода

- •Построение кросс-корреляционной матрицы для распознавания раздробленного флага

- •Поиск флага в потоке данных, передаваемых по волоконно-оптической линии связи

- •Поиск начала асинхронного сообщения

- •Обнаружение и исправление ошибок синхронизации при передаче непрерывного асинхронного потока данных

- •Распознавание межбайтовых границ в непрерывном синхронном потоке данных

- •Объединение удаленных сегментов сети Ethernet 10 BaseT

- •Структура сети Ethernet 10 BaseT

- •Как построить мост

- •Обмен кадрами через мост

- •Транспортная сеть

- •Преобразование кадра при его передаче между сегментами сети

- •Синхронизация передачи данных: способы кодирования

- •Основные способы кодирования цифровой информации для ее передачи по последовательным каналам связи

- •Структура последовательного канала связи

- •Униполярный код nrz

- •Биполярный код nrz

- •Код “Манчестер-II”

- •Код ami

- •Коды bnzs, hdb3

- •Трехуровневое кодирование сигнала с гарантированным изменением уровней между соседними битовыми интервалами

- •Способ кодирования сигнала для уменьшения излучаемых помех при его передаче по линии

- •Передача данных с использованием скремблера – дескремблера

- •Генераторы псевдослучайных битовых последовательностей

- •Скремблер – дескремблер с неизолированными генераторами псевдослучайных битовых последовательностей

- •Скремблер – дескремблер с изолированными генераторами псевдослучайных битовых последовательностей

- •Скремблер – дескремблер с неизолированными генераторами – улучшенный вариант

- •Синхронизация изолированных генераторов скремблера – дескремблера

- •Выделение синхросигнала и данных из канала связи

- •Одноконтурная и двухконтурные схемы выделения синхросигнала

- •Шифратор и дешифратор кода “Манчестер-II”

- •Вводные замечания

- •Схемы шифратора и дешифратора

- •Распознавание ячеек атм в битовом и байтовом потоках данных

- •Структура ячейки

- •Использование кода crc в процессе распознавания границ ячеек

- •Формирование заголовка ячейки передатчиком

- •Проверка правильности заголовка ячейки приемником

- •Поиск заголовка в непрерывном битовом потоке данных

- •Поиск заголовка в непрерывном байтовом потоке данных

- •Размещение ячейки внутри кадра

- •Логические соотношения для перехода от битового потока данных к байтовому

- •Мозаика решений

- •Сопряжение разноскоростных компонентовсинхронных систем без использования буфера типа fifo

- •Одноканальная система

- •Система с мультиплексированием каналов

- •Устранение проскальзываний синхронизации при передаче речевых сигналов

- •Идея использования периодов “тишины”

- •Прохождение сигнала по тракту микрофон – динамик

- •Детектор тишины

- •Поведение системы в экстремальных ситуациях

- •Идея устранения проскальзываний с помощью цап – ацп

- •Самообучающийся генератор синхросигналов

- •Усовершенствование измерителей длины кабельных линий передачи данных

- •Объект модернизации – рефлектометр

- •Измеритель длины кабельной линии передачи данных – первый вариант

- •Измеритель длины кабельной линии передачи данных – второй вариант

- •Литература

- •Оглавление

Проверка правильности заголовка ячейки приемником

Мы сейчас рассматриваем ситуацию, при которой в приемник поступают пять байтов, из которых пятый – код CRC, построенный на основе обработки первого – четвертого. Приемник решает такую задачу: действительно ли пятый байт представляет собой правильный код CRC, т.е. соответствует ли он контрольной сумме предшествующих четырех байтов?

Вернемся к рис.7.18 и рассмотрим его нижнюю часть. Делимое содержит в младшем байте код 00000111, который соответствует коду CRC, вычисленному передатчиком. Деление “лесенкой” на десяти ступенях дает те же результаты, что и ранее, но на одиннадцатой ступени получаем нулевой остаток. Это свидетельствует о том, что контрольная сумма правильная (что и требовалось проверить).

В правой части рис.7.19 показан ряд состояний кольцевого сдвигового регистра (см. рис.7.17) приемника при проверке правильности кода CRC. Отличия от группы состояний аналогичного регистра передатчика наблюдаются в тактах 38 – 40. В частности, в контрольном, сороковом такте имеем нулевое содержимое регистра, что подтверждает правильность приема заголовка.

Отметим, что нулевые коды получены также в тактах 1 – 4, 31; но в нашем примере заранее известно, что эти такты промежуточные, поэтому моменты получения промежуточных нулевых кодов не являются для нас значимыми событиями. Иное дело – в “реальной жизни”, когда такие события не должны оставаться незамеченными.

Поиск заголовка в непрерывном битовом потоке данных

Рассмотренный ранее способ проверки правильности кода CRC с помощью схемы, приведенной на рис.7.17, применим лишь в идеальной “статической” ситуации, когда заранее известно, что начальное состояние сдвигового регистра – нулевое, а в первом такте (n = 1) в регистр заносится старший бит заголовка.

Реальная ситуация динамична, в том смысле, что в поле зрения приемника находится бегущая строка из 40 битов. В каждом такте содержимое строки смещается на один бит. Поэтому в каждом такте нужно успеть проверить правильность пятого байта – предположительно кода CRC. Если применить рассмотренную ранее методику, то нужно в начале каждого такта установить кольцевой сдвиговый регистр в нуль, а оставшийся тактовый интервал разбить на 40 микротактов для выполнения процедуры, показанной в правой части рис.7.19. Но такое решение слишком “прямолинейно”, чтобы быть эффективным.

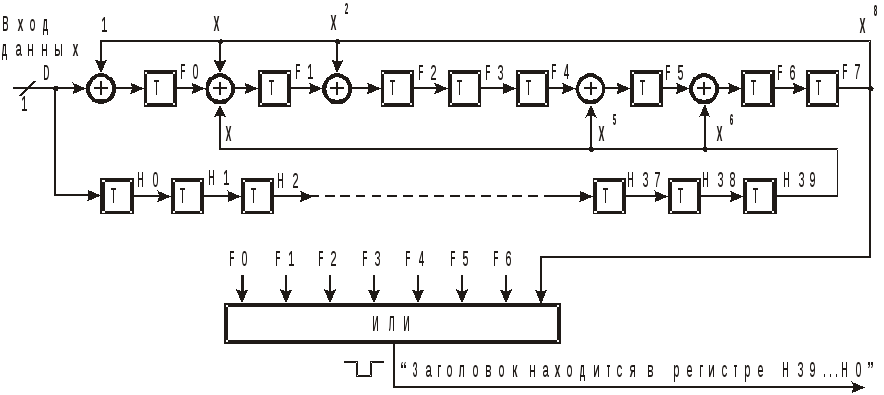

Рассмотрим решение, предложенное в [23] (рис.7.20). Здесь проверка очередного 40-разрядного кода выполняется за один такт в конвейерном режиме. Новый бит, вводимый в бегущую строку, обычным образом учитывается в новой контрольной сумме; но одновременно с этим новая контрольная сумма корректируется из-за того, что один бит “вытолкнут” за пределы бегущей строки, и схема должна уничтожить его былой вклад в контрольную сумму. Теперь всё по порядку.

Рис.7.117. Схема распознавания ячейки в непрерывном потоке битов. Цепи синхронизации триггеров не показаны

Сравнивая схемы, показанные на рис.7.17 и 7.20, можно заметить, что последняя представляет собой расширение первой. Кольцевой сдвиговый регистр содержит дополнительные цепи коррекции результата. Введен 40-разрядный сдвиговый регистр для хранения бегущей строки, в которой ожидается появление заголовка ячейки (точнее, кода с правильной контрольной суммой, претендующего на то, чтобы именоваться заголовком). Элемент ИЛИ регистрирует появление нулевого кода в кольцевом сдвиговом регистре. Все D-триггеры Т синхронизируются общим тактовым сигналом.

Состояние F7(n + 1) . . . F0(n + 1) кольцевого сдвигового регистра в такте n + 1 определяется состоянием F7(n) . . . F0(n) этого регистра в предыдущем такте n, состоянием разряда Н39(n) в такте n, а также новым значением входного бита данных D(n+1) и может быть выражено следующими соотношениями:

Процесс распознавания заголовка ячейки поясняется рис.7.21.

Предположим, что в некоторый момент t бегущая строка (регистр Н39 – Н0) содержит код L(t). Примем пока “на веру”, что в этот же момент в кольцевом сдвиговом регистре присутствует результат 40-тактной проверки кода L(t) по приведенной ранее методике. Этот результат (код 10110010, выделенный на рисунке серым фоном) отличен от нулевого, что находится в согласии с тем, что пятый байт кода L(t) не является контрольной суммой (CRC) четырех предыдущих байтов.

В момент t + 1 в бегущей строке фиксируется код L(t + 1). Этот код мы уже рассматривали в предыдущем примере. Он содержит правильную контрольную сумму (CRC), равную 00000111. Из рисунка следует, что простой ввод в кольцевой сдвиговый регистр очередного бита, т.е. простой (без поправки) переход от кода L(t) к коду L(t + 1) приводит к результату, равному 01100010. Этот результат нельзя считать правильным, так как при правильной контрольной сумме результат должен быть нулевым. Таким образом, если не учитывать поправку, то операцию можно выполнить быстро, за один такт, но, к сожалению, неправильно.

В чем же тут дело? Проблема состоит в том, что результат, равный 01100010, получен при обработке не 40-, а 41-разрядного числа, в котором старший разряд принадлежит коду L(t), а остальные – коду L(t + 1). Иными словами, в полученном результате неоправданно учитывается вклад в контрольную сумму исчезнувшего бита, отброшенного за пределы бегущей строки. Нужно уничтожить этот вклад. Но каков он?

Рис.7.118. Конвейерная обработка бегущей строки на примере анализа перекрывающихся кодов L(t) и L(t + 1) с неправильной и правильной контрольными суммами

Чтобы ответить на этот вопрос, отметим, что отброшенный разряд отображает число 240 = 1000...0 (сорок нулей после единицы). Если “разделить” (например, “лесенкой”) это число на наш делитель (100000111), то получим в остатке искомый вклад исчезнувшего бита. Он равен 01100010 (соответствующий образующий полином: Х6 + Х5 + Х). Остается вычесть этот мешающий вклад (поправку) из результата обработки 41-разрядного числа. Как отмечалось, “деление” выполняется довольно своеобразно, и операция вычитания заменяется поразрядным суммированием чисел по модулю два.

Такое суммирование выполняется на заключительном этапе процедуры, показанной на рис.7.21. Конечный результат совпадает с ожидаемым (нулевым). Как следует из схемы, приведенной на рис.7.20, введение поправки совмещено во времени с вводом очередного бита данных D, поэтому проверка кода в бегущей строке выполняется за один такт. Если бит, покинувший бегущую строку, нулевой, то поправка не нужна.

Таким образом, если в такте j проверка содержимого бегущей строки выполнена правильно, то и в следующем такте j + 1 гарантируется правильность результата (ошибками передачи пренебрегаем). Отсюда можно заключить, что схема (рис.7.20) обеспечивает непрерывное слежение за содержимым бегущей строки, причем каждый 40-разрядный код анализируется за один такт. Конечно, для начального заполнения “конвейера” нужно потратить 40 тактов после предварительной установки всех триггеров Т в нулевое состояние.

После установления надежной синхронизации приемника с передатчиком (на уровне установления границ ячеек) приемник использует код СRC для коррекции одиночных ошибок в заголовке. Это возможно, в частности, благодаря тому, что к моменту обнаружения ошибки заголовок хранится в регистре Н39 – Н0, поэтому можно проинвертировать ошибочный бит, т.е. исправить его (цепи коррекции одиночных ошибок в заголовке ячейки на рисунке не показаны).