- •С.М.Сухман, а.В.Бернов, б.В.Шевкопляс Компоненты телекоммуникационных систем Анализ инженерных решений

- •Isbn 5-7256-0316-4

- •Isbn 5-7256-0316-4 зао ЗелаксПлюс, 2002

- •Предисловие

- •Взаимодействие устройств типа dte/dce

- •Устройства типа dte и dce: сложности терминологии

- •Логический и физический уровни представления сигналов

- •Основные сигналы интерфейса rs-232

- •О сигнале ri

- •Сигналы TxD, clk, TxC, RxD, RxC

- •Взаимодействие устройств в асинхронном режиме

- •Взаимодействие устройств в синхронном режиме

- •Сравнение методов попутной и встречной синхронизации

- •Когда полезно проинвертировать синхросигнал

- •Пары сигналов dtr – dsr и dtr – dcd

- •Сигналы rts и cts

- •Прямое назначение . . .

- •. . . И альтернативное

- •Программное управление потоком данных

- •Трехпроводный вариант интерфейса rs-232

- •Электрические уровни сигналов rs-232

- •Взаимодействие одноименных устройств в асинхронном режиме

- •Варианты сопряжения двух устройств типа dte

- •Пример сопряжения двух устройств типа dce

- •Схемы взаимодействия устройств типа dte и dce в синхронном режиме: типовые решения

- •Вводные замечания

- •Системы с внутренней синхронизацией

- •Системы с внешней синхронизацией

- •Использование модема как устройства типа dte

- •Cистема с двумя последовательно включенными каналами связи

- •Схемы взаимодействия устройств типа dte и dce в синхронном режиме: нестандартные решения

- •Асинхронно-синхронная передача данных между устройствами типа dte и dce

- •Синхронный обмен данными с передачей кадровых меток

- •Повышение быстродействия и расширение функциональных возможностей системы с попутной синхронизацией

- •Объект модернизации – схема передачи пары сигналов TxD – clk

- •Удвоение скорости передачи данных с использованием для их приема положительного и отрицательного фронтов сигнала clk

- •Удвоение скорости передачи данных заменой сигнала clk сигналом разграничения одноименных битов

- •Расширение функциональных возможностей системы с разграничением одноименных битов

- •Создание дополнительного канала связи

- •Использование дополнительного канала связи для разграничения кадров

- •Аппаратное управление потоком данных с использованием пачек сигналов ТхС

- •Цифровая коррекция фазы сигнала от удаленного синхрогенератора

- •Выравнивание фаз передаваемого и принимаемого синхросигналов

- •Передача синхросигнала против течения потока данных

- •Взаимодействие удаленных устройств с непосредственной односторонней передачей синхросигнала по каналу связи

- •Синхронизация передачи данных между удаленными устройствами

- •Вводные замечания

- •Основная задача и ее универсальное решение

- •Проявления проскальзываний синхронизации для разных типов данных или технологий их передачи

- •Источники обновляемой синхронизации

- •Генераторы сигналов высокой точности и стабильности

- •Фазовые помехи

- •Адаптивный фильтр для подавления джиттера – вандера

- •Синхронизация дуплексных каналов

- •Зацикливание синхросигналов

- •Автоматическое предотвращение зацикливания синхросигналов

- •Синхронизация кольцевых структур

- •Отказоустойчивая система синхронизации сети с кольцевой топологией

- •Синхронизация передачи данных: распознавание и обработка кадров или иных структурных единиц

- •Передача полезных данных вместо избыточных битов синхронизации кадра

- •Частичное восстановление кадра при обнаружении проскальзывания

- •Битовые проскальзывания

- •Структура кадра, применяемого в системе мобильной связи gsm

- •Как по возможности сохранить кадр

- •Упрощение системы синхронизации формирователя hdsl-кадров

- •Минимизация длины флага

- •Традиционное решение с использованием многоразрядного флага

- •Использование одноразрядного флага для обозначения начала кадра

- •Вхождение в синхронизацию

- •Потеря и восстановление синхронизации

- •Использование раздробленного флага начала кадра

- •Применение неуникального флагового кода

- •Построение кросс-корреляционной матрицы для распознавания раздробленного флага

- •Поиск флага в потоке данных, передаваемых по волоконно-оптической линии связи

- •Поиск начала асинхронного сообщения

- •Обнаружение и исправление ошибок синхронизации при передаче непрерывного асинхронного потока данных

- •Распознавание межбайтовых границ в непрерывном синхронном потоке данных

- •Объединение удаленных сегментов сети Ethernet 10 BaseT

- •Структура сети Ethernet 10 BaseT

- •Как построить мост

- •Обмен кадрами через мост

- •Транспортная сеть

- •Преобразование кадра при его передаче между сегментами сети

- •Синхронизация передачи данных: способы кодирования

- •Основные способы кодирования цифровой информации для ее передачи по последовательным каналам связи

- •Структура последовательного канала связи

- •Униполярный код nrz

- •Биполярный код nrz

- •Код “Манчестер-II”

- •Код ami

- •Коды bnzs, hdb3

- •Трехуровневое кодирование сигнала с гарантированным изменением уровней между соседними битовыми интервалами

- •Способ кодирования сигнала для уменьшения излучаемых помех при его передаче по линии

- •Передача данных с использованием скремблера – дескремблера

- •Генераторы псевдослучайных битовых последовательностей

- •Скремблер – дескремблер с неизолированными генераторами псевдослучайных битовых последовательностей

- •Скремблер – дескремблер с изолированными генераторами псевдослучайных битовых последовательностей

- •Скремблер – дескремблер с неизолированными генераторами – улучшенный вариант

- •Синхронизация изолированных генераторов скремблера – дескремблера

- •Выделение синхросигнала и данных из канала связи

- •Одноконтурная и двухконтурные схемы выделения синхросигнала

- •Шифратор и дешифратор кода “Манчестер-II”

- •Вводные замечания

- •Схемы шифратора и дешифратора

- •Распознавание ячеек атм в битовом и байтовом потоках данных

- •Структура ячейки

- •Использование кода crc в процессе распознавания границ ячеек

- •Формирование заголовка ячейки передатчиком

- •Проверка правильности заголовка ячейки приемником

- •Поиск заголовка в непрерывном битовом потоке данных

- •Поиск заголовка в непрерывном байтовом потоке данных

- •Размещение ячейки внутри кадра

- •Логические соотношения для перехода от битового потока данных к байтовому

- •Мозаика решений

- •Сопряжение разноскоростных компонентовсинхронных систем без использования буфера типа fifo

- •Одноканальная система

- •Система с мультиплексированием каналов

- •Устранение проскальзываний синхронизации при передаче речевых сигналов

- •Идея использования периодов “тишины”

- •Прохождение сигнала по тракту микрофон – динамик

- •Детектор тишины

- •Поведение системы в экстремальных ситуациях

- •Идея устранения проскальзываний с помощью цап – ацп

- •Самообучающийся генератор синхросигналов

- •Усовершенствование измерителей длины кабельных линий передачи данных

- •Объект модернизации – рефлектометр

- •Измеритель длины кабельной линии передачи данных – первый вариант

- •Измеритель длины кабельной линии передачи данных – второй вариант

- •Литература

- •Оглавление

Частичное восстановление кадра при обнаружении проскальзывания

Битовые проскальзывания

Как уже отмечалось, проскальзывание – это искажение данных при их передаче между двумя устройствами, каждое из которых имеет индивидуальный источник синхронизации. Причем искажение это не простое – оно связано с внедрением лишнего или потерей одного из имеющихся битов.

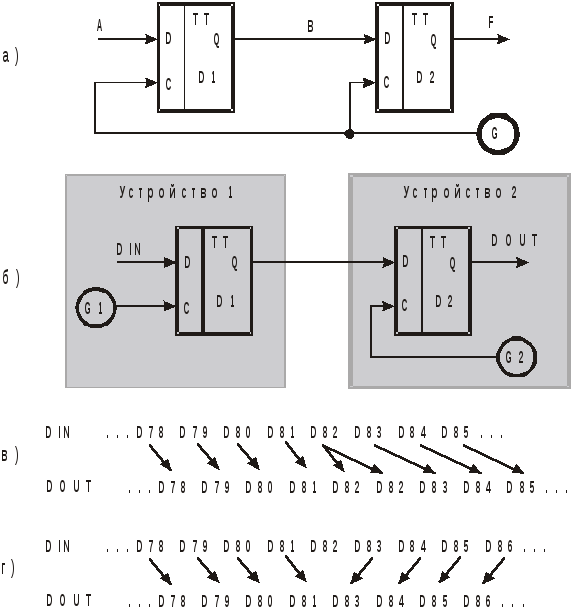

Для устранения проскальзываний используется буферная память типа FIFO – своего рода сглаживающий резервуар, включенный между устройствами; данные втекают и вытекают из него с почти равными скоростями. Проскальзывания возникают при переполнении или опустошении буфера, что, по сути, эквивалентно его отсутствию. Чтобы выявить природу искажений, рассмотрим модель передачи данных между устройствами 1 и 2 в отсутствие буфера (рис.5.5, б – г).

Модель построена на основе сдвигового регистра. Классический сдвиговый регистр (рис.5.5, а) содержит ряд последовательно включенных D-триггеров (в нашем примере – два триггера) с общей цепью синхронизации от генератора импульсов G. По положительному фронту синхроимпульса сигнал с выхода В триггера D1 переписывается на выход F триггера D2. Одновременно в триггер D1 принимается бит

Рис.5.58. Двухразрядный сдвиговый регистр (а) и неудачные попытки его использования для передачи данных между устройствами 1 и 2 (б – г)

данных с входа А. Отрицательный фронт синхроимпульса не изменяет состояния сигналов в точках В и F. При поступлении следующего положительного фронта импульса процесс повторяется и т.д.

Совершенно иная картина наблюдается в том случае, когда триггеры D1 и D2 синхронизируются от независимых генераторов G1 и G2 с одинаковыми номинальными частотами (рис.5.5, б). Сколь бы близкими не были эти частоты, всегда существует дрейф взаимного фазового сдвига между синхросигналами. В некоторые моменты, повторяющиеся, например, с периодом 10 с, фазовый сдвиг равен нулю; в промежутках между ними он увеличивается в ту или иную сторону в зависимости от соотношения частот генераторов. В критические моменты, которые повторяются с тем же периодом, происходит дублирование либо потеря бита, передаваемого по цепочке триггеров.

Предположим, что частота генератора G2 чуть превышает частоту генератора G1. Тогда выходной поток данных DOUT будет чуть более интенсивным, чем входной поток DIN. В нашем примере через каждые 10 с к выходному потоку будет добавляться один лишний бит, так как за это время генератор G2 успел опередить генератор G1 на один синхроимпульс. Откуда возьмется дополнительный бит? Не иначе как с выхода триггера D1, но тогда этот бит будет повторять уже переданный ранее. (Это логический подход к анализу происхождения лишнего бита, но к тем же результатам приводит и чисто схемотехнический подход.)

Данная ситуация поясняется рис.5.5, в. Первоначально входная последовательность данных соответствует выходной (нумерация битов условная). Но в некоторый промежуток времени, как показано на рисунке двумя расходящимися стрелками, бит D82 успевает дважды подряд записаться в выходной триггер, а далее соответствие временно сохраняется.

При обратном соотношении частот генераторов “предложение превышает спрос”, и поэтому в каждом цикле фазовых гонок неизбежно теряется один бит из входного потока (рис.5.5, г, бит D82).