- •С.М.Сухман, а.В.Бернов, б.В.Шевкопляс Компоненты телекоммуникационных систем Анализ инженерных решений

- •Isbn 5-7256-0316-4

- •Isbn 5-7256-0316-4 зао ЗелаксПлюс, 2002

- •Предисловие

- •Взаимодействие устройств типа dte/dce

- •Устройства типа dte и dce: сложности терминологии

- •Логический и физический уровни представления сигналов

- •Основные сигналы интерфейса rs-232

- •О сигнале ri

- •Сигналы TxD, clk, TxC, RxD, RxC

- •Взаимодействие устройств в асинхронном режиме

- •Взаимодействие устройств в синхронном режиме

- •Сравнение методов попутной и встречной синхронизации

- •Когда полезно проинвертировать синхросигнал

- •Пары сигналов dtr – dsr и dtr – dcd

- •Сигналы rts и cts

- •Прямое назначение . . .

- •. . . И альтернативное

- •Программное управление потоком данных

- •Трехпроводный вариант интерфейса rs-232

- •Электрические уровни сигналов rs-232

- •Взаимодействие одноименных устройств в асинхронном режиме

- •Варианты сопряжения двух устройств типа dte

- •Пример сопряжения двух устройств типа dce

- •Схемы взаимодействия устройств типа dte и dce в синхронном режиме: типовые решения

- •Вводные замечания

- •Системы с внутренней синхронизацией

- •Системы с внешней синхронизацией

- •Использование модема как устройства типа dte

- •Cистема с двумя последовательно включенными каналами связи

- •Схемы взаимодействия устройств типа dte и dce в синхронном режиме: нестандартные решения

- •Асинхронно-синхронная передача данных между устройствами типа dte и dce

- •Синхронный обмен данными с передачей кадровых меток

- •Повышение быстродействия и расширение функциональных возможностей системы с попутной синхронизацией

- •Объект модернизации – схема передачи пары сигналов TxD – clk

- •Удвоение скорости передачи данных с использованием для их приема положительного и отрицательного фронтов сигнала clk

- •Удвоение скорости передачи данных заменой сигнала clk сигналом разграничения одноименных битов

- •Расширение функциональных возможностей системы с разграничением одноименных битов

- •Создание дополнительного канала связи

- •Использование дополнительного канала связи для разграничения кадров

- •Аппаратное управление потоком данных с использованием пачек сигналов ТхС

- •Цифровая коррекция фазы сигнала от удаленного синхрогенератора

- •Выравнивание фаз передаваемого и принимаемого синхросигналов

- •Передача синхросигнала против течения потока данных

- •Взаимодействие удаленных устройств с непосредственной односторонней передачей синхросигнала по каналу связи

- •Синхронизация передачи данных между удаленными устройствами

- •Вводные замечания

- •Основная задача и ее универсальное решение

- •Проявления проскальзываний синхронизации для разных типов данных или технологий их передачи

- •Источники обновляемой синхронизации

- •Генераторы сигналов высокой точности и стабильности

- •Фазовые помехи

- •Адаптивный фильтр для подавления джиттера – вандера

- •Синхронизация дуплексных каналов

- •Зацикливание синхросигналов

- •Автоматическое предотвращение зацикливания синхросигналов

- •Синхронизация кольцевых структур

- •Отказоустойчивая система синхронизации сети с кольцевой топологией

- •Синхронизация передачи данных: распознавание и обработка кадров или иных структурных единиц

- •Передача полезных данных вместо избыточных битов синхронизации кадра

- •Частичное восстановление кадра при обнаружении проскальзывания

- •Битовые проскальзывания

- •Структура кадра, применяемого в системе мобильной связи gsm

- •Как по возможности сохранить кадр

- •Упрощение системы синхронизации формирователя hdsl-кадров

- •Минимизация длины флага

- •Традиционное решение с использованием многоразрядного флага

- •Использование одноразрядного флага для обозначения начала кадра

- •Вхождение в синхронизацию

- •Потеря и восстановление синхронизации

- •Использование раздробленного флага начала кадра

- •Применение неуникального флагового кода

- •Построение кросс-корреляционной матрицы для распознавания раздробленного флага

- •Поиск флага в потоке данных, передаваемых по волоконно-оптической линии связи

- •Поиск начала асинхронного сообщения

- •Обнаружение и исправление ошибок синхронизации при передаче непрерывного асинхронного потока данных

- •Распознавание межбайтовых границ в непрерывном синхронном потоке данных

- •Объединение удаленных сегментов сети Ethernet 10 BaseT

- •Структура сети Ethernet 10 BaseT

- •Как построить мост

- •Обмен кадрами через мост

- •Транспортная сеть

- •Преобразование кадра при его передаче между сегментами сети

- •Синхронизация передачи данных: способы кодирования

- •Основные способы кодирования цифровой информации для ее передачи по последовательным каналам связи

- •Структура последовательного канала связи

- •Униполярный код nrz

- •Биполярный код nrz

- •Код “Манчестер-II”

- •Код ami

- •Коды bnzs, hdb3

- •Трехуровневое кодирование сигнала с гарантированным изменением уровней между соседними битовыми интервалами

- •Способ кодирования сигнала для уменьшения излучаемых помех при его передаче по линии

- •Передача данных с использованием скремблера – дескремблера

- •Генераторы псевдослучайных битовых последовательностей

- •Скремблер – дескремблер с неизолированными генераторами псевдослучайных битовых последовательностей

- •Скремблер – дескремблер с изолированными генераторами псевдослучайных битовых последовательностей

- •Скремблер – дескремблер с неизолированными генераторами – улучшенный вариант

- •Синхронизация изолированных генераторов скремблера – дескремблера

- •Выделение синхросигнала и данных из канала связи

- •Одноконтурная и двухконтурные схемы выделения синхросигнала

- •Шифратор и дешифратор кода “Манчестер-II”

- •Вводные замечания

- •Схемы шифратора и дешифратора

- •Распознавание ячеек атм в битовом и байтовом потоках данных

- •Структура ячейки

- •Использование кода crc в процессе распознавания границ ячеек

- •Формирование заголовка ячейки передатчиком

- •Проверка правильности заголовка ячейки приемником

- •Поиск заголовка в непрерывном битовом потоке данных

- •Поиск заголовка в непрерывном байтовом потоке данных

- •Размещение ячейки внутри кадра

- •Логические соотношения для перехода от битового потока данных к байтовому

- •Мозаика решений

- •Сопряжение разноскоростных компонентовсинхронных систем без использования буфера типа fifo

- •Одноканальная система

- •Система с мультиплексированием каналов

- •Устранение проскальзываний синхронизации при передаче речевых сигналов

- •Идея использования периодов “тишины”

- •Прохождение сигнала по тракту микрофон – динамик

- •Детектор тишины

- •Поведение системы в экстремальных ситуациях

- •Идея устранения проскальзываний с помощью цап – ацп

- •Самообучающийся генератор синхросигналов

- •Усовершенствование измерителей длины кабельных линий передачи данных

- •Объект модернизации – рефлектометр

- •Измеритель длины кабельной линии передачи данных – первый вариант

- •Измеритель длины кабельной линии передачи данных – второй вариант

- •Литература

- •Оглавление

Взаимодействие удаленных устройств с непосредственной односторонней передачей синхросигнала по каналу связи

Ранее (см. рис.2.4 и 3.17) были рассмотрены две схемы получения синхронных и синфазных потоков данных. Первая схема построена на основе эластичной памяти, вторая использует фазовый компаратор и канальную петлю обратной связи. Здесь представлено еще одно, менее универсальное, но, возможно, более экономичное решение той же задачи (рис.3.20) [49]. Его основное отличие от предыдущих состоит в применении трех пар проводов в канале связи. Одна пара используется для передачи синхросигналов, по двум другим транслируются данные.

Рис.3.37. Система с непосредственной передачей синхросигнала по каналу связи: D – элемент задержки; выход TxC устройства DCE 1 не используется

Напомним, в чем заключается задача. Некоторые устройства типа DCE (в нашем примере – устройство DCE 1) генерируют совпадающие синхросигналы RxC и TxC. Сигнал RxC сопровождает данные, выдаваемые из устройства DCE 1. Сигнал ТхС задает временную сетку для принимаемых данных. Источником этих данных является устройство DTE, которое удалено от устройства DCE 1 на значительное расстояние. Поэтому нужно каким-то образом заставить устройство DTE подстроиться так, чтобы передаваемые им данные, подойдя к устройству DCE 1, попали в нужную временную сетку. В данном решении это достигается введением в устройство DCE 3 элемента D регулируемой фазовой задержки синхросигнала. Рассмотрим работу системы.

При передаче данных “слева – направо” они проходят из устройства DCE 1 в устройство DTE по нижней трассе. Синхросигнал от генератора G передается по верхней трассе с такими же физическими параметрами, поэтому он задерживается в той же мере, что и данные. Так что на входах RxD и RxC устройства DTE сигналы находятся в правильных фазовых соотношениях (см. рис.1.9). (В действительности некоторый перекос сигналов, конечно, существует, но при достаточно низкой скорости передачи данных им можно пренебречь.)

Данные выдаются из устройства DTE под управлением сигнала на его входе ТхС (см. рис.1.7). При этом c точки зрения устройства DTE не имеет значения, в каком фазовом соотношении находятся сигналы на его входах TxC и RxC. Изменяя это соотношение, можно перемещать данные на входе устройства DCE 1 относительно синхросетки сигнала с генератора G. В частности, при соответствующей настройке элемента D можно достичь правильного фазового соотношения между сигналами на входе TxD и выходе TxC устройства DCE 1.

Элемент D регулируемой фазовой задержки синхросигнала должен обеспечивать плавный или ступенчатый сдвиг фазы выходного сигнала относительно входного в диапазоне от нуля до 360 градусов. Требуемая фазовая задержка зависит от длин и типов кабелей между устройствами и элементной базы устройств DCE 2 и DCE 3.

П редположим,

что некая фирма-производитель в массовом

порядке поставляет потребителям системы,

показанные на рис.3.20, причем они могут

отличаться только длиной кабеля,

образующего канал связи. Тогда требуемая

фазовая задержка элемента D является

функцией одной переменной – длины этого

кабеля. Вид функции нетрудно получить

расчетным путем или моделированием и

подтвердить экспериментально. Если эти

работы проведены, то фирма-производитель

при изготовлении кабеля определенной

длины может закодировать необходимую

величину фазовой задержки, например в

виде паяных перемычек на соединителе,

как показано на рис.3.21.

редположим,

что некая фирма-производитель в массовом

порядке поставляет потребителям системы,

показанные на рис.3.20, причем они могут

отличаться только длиной кабеля,

образующего канал связи. Тогда требуемая

фазовая задержка элемента D является

функцией одной переменной – длины этого

кабеля. Вид функции нетрудно получить

расчетным путем или моделированием и

подтвердить экспериментально. Если эти

работы проведены, то фирма-производитель

при изготовлении кабеля определенной

длины может закодировать необходимую

величину фазовой задержки, например в

виде паяных перемычек на соединителе,

как показано на рис.3.21.

Рис.3.38. Схема сопряжения устройства DCE 3 с каналом связи

В данном примере соединитель содержит шесть пар контактов для подключения трех витых пар проводов кабеля, по которому передаются синхросигналы и данные. Кроме того, предусмотрены пять пар контактов для задания четырехразрядного кода, определяющего необходимую фазовую задержку синхросигнала. Одна из этих пар предназначена для подключения шины G кабельной розетки к шине нулевого потенциала устройства DCE 3. Остальные контакты розетки могут быть либо соединены, либо не соединены с шиной G с помощью индивидуальных паяных перемычек.

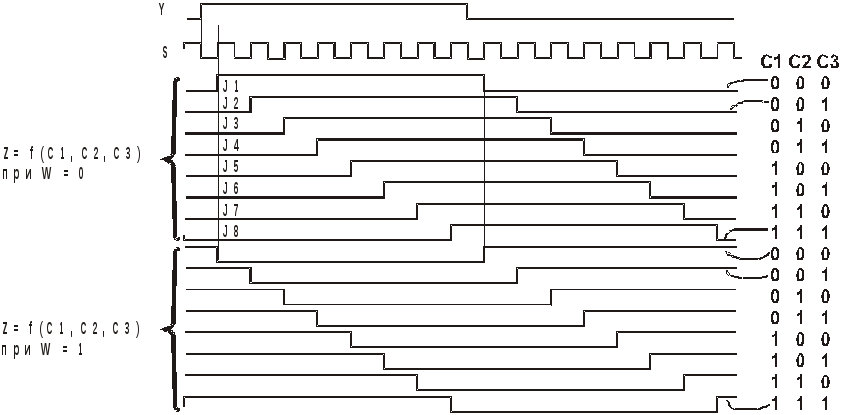

Если перемычка установлена, то на соответствующем управляющем входе элемента задержки присутствует сигнал лог. 0, в противном случае – сигнал лог. 1. Структура элемента задержки представлена на рис.3.22, временные диаграммы преобразования сигналов – на рис.3.23.

Рис.3.39. Структура элемента задержки D

Элемент задержки содержит умножитель частоты, сдвиговый регистр, мультиплексор и логический элемент Исключающее ИЛИ. Частота входного синхросигнала Y умножается на 16 и используется для продвижения информации в сдвиговом регистре.

Рис.3.40. Временные диаграммы работы элемента D фазовой задержки

В зависимости от кода С1 С2 С3 один из выходных сигналов сдвигового регистра транслируется через мультиплексор и логический элемент Исключающее ИЛИ на выход Z. При этом сигнал инвертируется, если W = 1. Таким образом, шаг фазовой задержки составляет 1/16 часть периода входного синхросигнала или 360/16 = 22,5 градуса. Умножитель частоты может быть выполнен по схеме, показанной на рис.3.24.

Рис.3.41. Схема умножителя частоты

Генератор G формирует сигнал S частотой 16F, где F – частота входного сигнала Y. Фазовый компаратор следит за совпадением фронтов входных сигналов. При обнаружении более или менее устойчивого разбаланса фронтов он корректирует напряжение U управления частотой генератора в направлении улучшения совпадения. Поэтому сигнал S привязан по фазе к сигналу Y. В данном примере предполагается, что положительный фронт сигнала Y совпадает с отрицательным фронтом сигнала S (см. рис.3.23).