Ris_DSP / TZOS_red4_ch2_C25_Tablet

.pdf

|

|

|

153 |

LDPK 7h |

;загрузить DP=7 |

||

CNFP |

|

;B0 - как память программ |

|

lab IN |

78h,PA0 |

;ввод одного отсчета x(n) по адресу |

|

LRLK AR1,03FFh |

;3F8h=1111111000 |

||

;max адрес ввода x(n) в блоке В1 |

|||

LARP AR1 |

;инициализация вспомогательного регистра AR1 |

||

MPYK |

0 |

;обнулить Р-рег. умножителя |

|

ZAC |

|

;обнулить АСС |

|

RPTK |

7h |

;повторить следующую команду 8 раз |

|

MACD FF00h,*- |

;умножение/накопление со сдвигом данных в B1 |

||

APAC |

|

;добавить к АСС последнее произведение |

|

SACH |

75h,0 |

;сохранить рез-т по адресу 3F5h=1111110101 |

|

OUT |

75h,PA1 |

;вывод содерж. адреса 3F5h через I/O PA1 |

|

B |

lab,* |

;возврат к вводу нового отсчета x(n) (к IN 78h,PA0) |

|

Каждая выборка x(n) вводится с помощью команды IN через I/O порт PA0 в память данных, начиная с адреса 03FFh (7 страница памяти данных). Коэффициенты расположены в памяти программ, начиная с адреса FF00h. Каждый вычисленный отсчет y(n) отклика фильтра сохраняется в памяти данных командой SACH и выводится из процессора через I/O порт PA1 командой OUT. Далее с помощью команды безусловного перехода B производится возврат к началу программы для ввода следующего отсчета входного сигнала x(n).

Преимущества команды MACD проявляются для N>3. Для цифровых фильтров с более низким порядком, рекомендуется вместо RPTK/MACD использовать пару команд LTD/MPY.

Комбинация команд RPTK/MACD обеспечивает использование минимальной памяти программ и высокое быстродействие при выполнении программы цифровых фильтров.

Программа вычисления базовой операции БПФ по основанию 2 с прореживанием по времени (алгоритм с замещением).

Граф "базовой операции" БПФ по основанию 2 с прореживанием по времени имеет вид:

154

Если входные данные P, Q и коэффициенты W - комплексные: P = PR + jPI , Q = QR + jQI , W = WR + jWI ,

то для определения мнимой и действительной частей X и Y необходимо произвести следующие вычисления:

XR = PR + (QR*WR - QI*WI); XI = PI + (QR*WI + QI*WR); YR = PR - (QR*WR - QI*WI); YI = PI - (QR*WI + QI*WR);

Перед вычислением базовой операции предполагается, что входные данные PR, PI, QR, QI и коэффициенты WR,WI расположены в соответствующих ячейках памяти данных (ЯП). Для исключения возможного переполнения входные отсчеты изначально сдвинуты на один разряд вправо (умножены на 1/2).

*

*Вычисление QR*WR - QI*WI и размещение результата в QR

LT QR |

;загрузить в T-регистр значение из ЯП для QR [T=1/2(QR)] |

MPY WR |

;вычислить (QR*WR) и поместить в P-регистр [P=1/2(QR*WR)] |

LTP QI |

;поместить в ACC содерж. Р-рег. и загрузить в T-регистр |

MPY WI |

;значение из ЯП для QI [ACC=1/2(QR*WR); T=1/2(QI)] |

;вычислить (QI*WI) [P=1/2(QI*WI)] |

|

SPAC |

;вычесть из ACC P-регистр [АСС=1/2(QR*WR-QI*WI)] |

MPY WR |

;вычислить (QI*WR) и поместить в P-регистр [P=1/2(QI*WR)] |

LT QR |

;загрузить в T-регистр значение из ЯП для QR [T=1/2(QI)] |

SACH QR |

;сохранить старшее слово АСС в ЯП для QR [QR = 1/2(QR*WR-QI*WI)] |

*Вычисление QR*WI + QI*WR и размещение результата в QI |

|

PAC |

;поместить в АСС содержимое Р-рег. [ACC=1/2(QI*WR)] |

MPY WI |

;вычислить (QR*WI) и поместить в P-регистр [P=1/2(QR*WI)] |

APAC |

;сложить P-регистр с АСС [ACC=1/2(QR*WI+QI*WR)] |

SACH QI |

;сохранить старшее слово АСС в ЯП для QI [QI = 1/2(QR*WI+QI*WR)] |

* Вычисление XR и YR и размещение результата в PR и QR, соответственно

LAC PR,14 |

;загрузить в АСС значение из ЯП для PR со сдвигом [ACC=1/4(PR)] |

ADD QR,15 |

;прибавить к АСС значение из ЯП для QR со сдвигом |

SACH PR,1 |

;[ACC = 1/4(PR+(QR*WR-QI*WI))] |

;сохранить старшее слово АСС в ЯП для PR со сдвигом |

|

SUBH QR |

;[PR = 1/2(PR+(QR*WR-QI*WI))] |

;вычесть содержимое ЯП для QR из ACC |

155

;[ACC = 1/4(PR-(QR*WR-QI*WI))]

SACH QR,1 ;сохранить старшее слово АСС в ЯП для QR со

;сдвигом [QR = 1/2(PR-(QR*WR-QI*WI))]

* Вычисление XI и YI и размещение результата в PI и QI, соответственно

LAC PI,14 ;загрузить в АСС значение из ЯП для PI со сдвигом [ACC=1/4(PI)]

ADD QI,15 |

;прибавить к АСС значение из ЯП для QI со сдвигом |

SACH PI,1 |

;[ACC = 1/4(PI+(QR*WI+QI*WR))] |

;сохранить старшее слово АСС в ЯП для PI со |

|

SUBH QI |

;сдвигом [PI = 1/2(PI+(QR*WI+QI*WR))] |

;вычесть содержимое ЯП для QI из ACC |

|

SACH QI,1 |

;[ACC = 1/4(PI-(QR*WI+QI*WR))] |

;сохранить старшее слово АСС в ЯП для QI со |

|

|

;сдвигом [QI = 1/2(PI-(QR*WI+QI*WR))] |

Программа занимает 22 машинных цикла. Если длительность машинного цикла процессора составляет 100 нс, то на вычисление базовой операции будет затрачено tБО = 2.2 мкс.

Время вычисления N–точечного БПФ по основанию 2 примерно равно (без учета перестановки входных данных):

tБПФ≈m tБО , где m=N/2 log2N – количество базовых операций необходимых для вычисления N–точечного БПФ.

Ввод 8-ми значений данных через параллельный порт РА0 в RAM процессора, начиная с адр. 0060h, с одновременным реверсом адресов (для 8-точечного БПФ).

LARK AR0,0004h |

;ввод в AR0 константы (0004h – половина |

LRLK AR1,0060h |

;размерности БПФ) |

;загрузить в вспомогательный регистр |

|

LARP AR1 |

;AR3 адрес 0060h (9610) |

;инициализировать вспомогат. рег. AR1 |

|

RPTK 7h |

;ввести данные (8 значений) через I/O |

IN *BR0+,PA0 |

;порт PA0, прибавить AR0 к AR1 с |

;одновременным реверсом адресов |

Перепишем процедуру ввода 8 значений x(n) без использования команды RPTK.

*BR0+ - ВВОД X(0), AR1=0110 0000

|

156 |

|

|

*BR0+ - ВВОД X(1), AR1=0110 0100 |

|

перенос вправо |

|

|

|

|

|

*BR0+ - ВВОД X(2), AR1=0110 0010 |

0110 0100 |

(AR1) |

|

*BR0+ - ВВОД X(3), AR1=0110 0110 |

+ |

|

|

*BR0+ - ВВОД X(4), AR1=0110 0001 |

|

0100 |

(AR0) |

*BR0+ - ВВОД X(5), AR1=0110 0101 |

0110 0010 |

(новое AR1) |

|

*BR0+ - ВВОД X(6), AR1=0110 0011 |

|

|

|

*BR0 - ВВОД X(7), AR1=0110 0111

Расположение данных в RAM после ввода с реверсом бит адресов.

Адрес RAM |

x(n) |

0110 0000 |

x(0) |

0110 0001 |

x(4) |

0110 0010 |

x(2) |

0110 0011 |

x(6) |

0110 0100 |

x(1) |

0110 0101 |

x(5) |

0110 0110 |

x(3) |

0110 0111 |

x(7) |

4.3.18 АППАРАТНОЕ ПРИМЕНЕНИЕ TMS320C25 НАЗНАЧЕНИЕ ВЫВОДОВ

Конструктивно микросхема выполняется в пластмассовом или металлокерамическом корпусе с 68 выводами. Все выводы электрически совместимы с элементами TTL.

Условное графическое обозначение сигнального процессора

TMS320C25 приведено на рис.4.20.

|

|

157 |

|

|

|

|

|

|

|

|

|

Назначение выводов: |

|

|

|

|

|||||

|

A0-A15 - 16-разрядная параллельная шина |

|||||||||

|

адреса. Мультиплексирована с внешними |

|||||||||

|

адресами памяти программ/данных или |

|||||||||

|

ввода/вывода. |

|

|

|

|

|

|

|||

|

D0-D15 - 16-разрядная параллельная шина |

|||||||||

|

данных. |

Мультиплексирована |

с |

внешней |

||||||

|

ROM/RAM или устройствами I/O. |

|

|

|

||||||

|

DS, PS, IS - сигналы выбора области |

|||||||||

|

данных, программ или ввода/вывода. |

|||||||||

|

Активным является низкий уровень сигнала. |

|||||||||

|

READY - вход готовности данных. |

|||||||||

|

Показывает |

что |

внешнее |

устройство |

||||||

|

завершило подготовку к обмену данными. |

|||||||||

|

Если устройство не готово (READY=0), |

|||||||||

|

TMS320C25 |

ждет |

один |

цикл |

и |

снова |

||||

|

проверяет наличие сигнала READY. |

|

||||||||

|

R/W - сигнал чтения/записи. Показывает |

|||||||||

|

направление |

|

передачи |

данных |

при |

|||||

|

взаимодействии с внешними устройствами. |

|||||||||

|

STRB - стробирующий сигнал. |

|

|

|

||||||

|

BR - сигнал захвата шины. Активный |

|||||||||

|

когда |

процессору |

требуется |

|

доступ к |

|||||

|

глобальной памяти данных. |

|

|

|

|

|||||

|

HOLD - сигнал запроса ПДП. Когда он |

|||||||||

|

активный, процессор переходит в режим |

|||||||||

|

ПДП после завершения текущей команды. |

|||||||||

|

Переводит шины адреса, данных и |

|||||||||

|

управляющие выводы в третье состояние. |

|||||||||

Рис. 4.20. Условное |

HOLDA |

- сигнал подтверждения ПДП. |

||||||||

Показывает, что процессор перешел в режим |

||||||||||

графическое обозначение |

||||||||||

сигнального процессора |

ПДП |

и его |

локальная память |

доступна |

||||||

TMS320C25 |

внешнему процессору. |

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

||

158

SYNC - вход синхронизации. Позволяет синхронизировать работу двух или более TMS320C25. Должен быть активным (низкий уровень) по переднему фронту сигнала CLKIN.

BIO - входной сигнал ветвления. Управляет результатом выполнения команды BIOZ. Активен (низкий уровень) во время действия команды

BIOZ.

IACK - сигнал подтверждения прерывания. После получения сигнала подтверждения прерывания программа делает переход на адрес вектора прерывания, который выставлен на шине адреса А15-А0.

INT0-INT2 - входные сигналы внешних прерываний. Маскируются регистром маски прерывания и битом режима прерывания.

MSC - сигнал завершения микросостояния. Имеет активный низкий уровень, когда TMS320С25 завершил операции с памятью (захват шины или чтение/запись памяти данных). Используется для организации цикла ожидания сигнала READY при работе с медленной внешней памятью.

RS - вход сигнала сброс.

XF - выход внешнего флага (программно переключаемый сигнал). Используется для сигнализации другому процессору при мультипроцессорных связях или для общих целей.

CLKOUT1 - выходной сигнал основной частоты (соответствует частоте кварцевого резонатора, деленной на 4).

CLKOUT2 – дополнительный выходной сигнал, сдвинутый на 900 относительно CLKOUT1.

X1 - вход для подключения внешнего кварцевого резонатора. X2/CLKIN – второй вход для подключения внешнего кварцевого

резонатора или внешнего генератора (при этом X1 не используется). |

|

|||

CLKR - внешний синхросигнал |

для приема данных в регистр DRR |

|||

(регистр |

приема |

данных последовательного порта) через вывод |

DR |

|

(прием данных). |

|

|

|

|

CLKX - внешний синхросигнал |

для передачи данных из регистра DXR |

|||

(регистр |

передачи |

данных последовательного порта) на вывод |

DX |

|

(передача данных).

DR – вход приема данных через последовательный порт. DX – выход передачи данных через последовательный порт.

159

FSR - вход кадровой синхронизации приемника.

FSX - вход/выход кадровой синхронизации передатчика. Обычно FSX работает на вход, но если TXM (бит режима передачи) установлен в единицу, то работает на выход.

Vcc, Vss – выводы для подключения внешнего питания (+5 V) и «земли», соответственно.

4.3.19. ФОРМИРОВАНИЕ СИГНАЛА «СБРОС»

Cхема формирования сигнала сброса RS приведена на рис.4.21.

В исходном состоянии конденсатор C1 заряжен напряжением питания +5V, обеспечивая на контакте RS процессора уровень логической единицы. После нажатия кнопки S1 конденсатор C1 разряжается, обеспечивая сброс процессора. Через время τ=R1C1 конденсатор заряжается и сигнал Reset устанавливается в единицу. Время заряда конденсатора τ должно быть не менее трех машинных циклов процессора, т.е. постоянная времени при использовании 100 нс машинного цикла процессора TMS320C25 должна быть не менее 300 нс.

4.3.20. СИНХРОНИЗАЦИЯ ПРОЦЕССОРА

Внутренний машинный цикл процессора TMS320C25 формируется делением частоты внешнего резонатора или кварцованного генератора на 4. Для обеспечения машинного цикла длительностью 100нс внешняя частота должна быть 1/(100нс) 4=40 МГц.

Схемы синхронизации процессора TMS320C25 для обеспечения машинного цикла длительностью 100 нс с подключением внешнего резонатора или кварцованного генератора приведены на рис.4.22а и рис.4.22б, соответственно.

160

Рис.4.21 Формирование сигнала «СБРОС»

а) |

б) |

Рис.4.22 Синхронизация процессора |

|

4.3.21. ПОДКЛЮЧЕНИЕ ВНЕШНЕЙ ПАМЯТИ ДАННЫХ

Схема включения процессора TMS320C25 с внешней статической памятью данных (RAM) приведена на рис.4.23. Внешняя память данных объемом 4К×16 построена на 4 статических ОЗУ с произвольным доступом SY7C168 организацией 4К×4.

Работа с внешней памятью данных индицируется сигналом DS (Data select) процессора. Сигнал READY формируется дополнительной логикой U1 и U2A (в данном случае не требуется дополнительных циклов ожидания, т.к. память быстродействующая). Выбор банка памяти осуществляется дешифратором адреса 74AS138, стробируемым сигналом строба STRB. Переключение режима чтение/запись производится сигналом R/W. Внешняя память данных находится по адресу «1».

161

Рис.4.23 Подключение внешней памяти данных

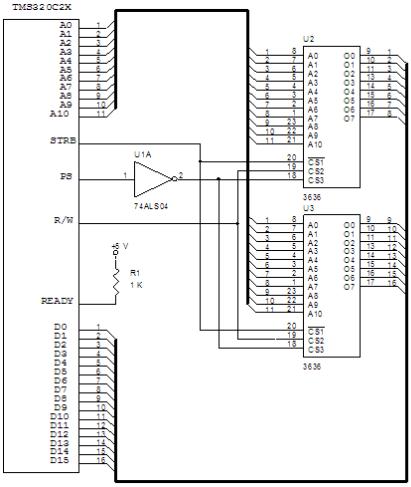

4.3.22. ПОДКЛЮЧЕНИЕ ВНЕШНЕЙ ПАМЯТИ ПРОГРАММ

Схема включения процессора TMS320C25 с внешней быстродействующей памятью программ (ROM) приведена на рис.4.24. Внешняя память программ объемом 2К×16 построена на 2 ППЗУ TBP38L165-35 организацией 2К×8. Работа с внешней памятью программ индицируется сигналом PS (Programm select) процессора. Выбор памяти программ осуществляется сигналами PS, строба STRB и R/W процессора.

162

Рис.4.24 Подключение внешней памяти программ

4.3.23. ВХОДНОЙ АНАЛОГОВЫЙ ИНТЕРФЕЙС

Подключение 12-разрядного АЦП к TMS320C2X приведено на рис.4.25. АЦП, используя сигнал IS (Interface select) процессора, подключен как