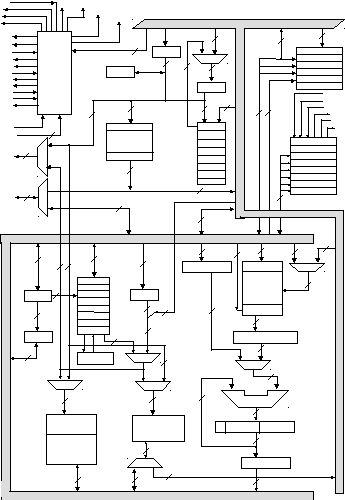

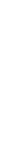

Ris_DSP / RIS_C25_C30N

.docS YNC

X1 X2/CLKIN

YNC

X1 X2/CLKIN

IS CLKOUT1

DS CLKOUT2

PC PROGRAM BUS

R/W C 16 16 16 16

STAB O 16

READY N PFC (16) QIR (16)

BR R MUX IR (16)

XF T 16 ST0 (16 )

HOLD R MCS (16) 16 16 ST1 (16)

HOLDA O RPTC (8)

MSC L PC (16) IFR (6)

BIO L DR

RS E CLKR

IACK R FSR

16 12 16 16 DX

16 8 CLKX

MP/MC 3 ADRESS STACK FSX

INT (2-0) PROGRAMM (8 * 16)

ROM/EPROM RSR (16)

16 M ( 4096 16 ) XSR (16)

A15-A0 U INSTRUCTION 16 DRR (16 )

X 16 DXR (16)

16 16 TIM (16)

16 PRD (16)

6 IMR (6)

D15-D0 16 M 8 GREG (8)

U 16

X 16 16

16

DATA BUS

16 16 16 16 16

3 16 16 16 9

SHIFTER (0 - 16) TR (16) MUX

AR0 (16) 16

3 AR1 (16) MULTIPLER

ARP (3) AR2 (16) DP (9)

AR3 (16)

AR4 (16) 9 7 LSB 32 PR (32)

3 AR5 (16) FROM IR

AR6 (16) 32

AR7 (16) 16 (DRB)

ARB (3 ) 16 (AFB) SHIFTER (- 6, 0, 1, 4 )

3 32

ARAU (16) MUX 16

MUX

(DAB)

16 32

MUX MUX

16 16 32 ALU (32)

32

BLOCK B2 DATA / PROG

( 32 16) RAM ( 256 16 ) C ACCH (16) ACCL (16)

BLOCK B0

DATA RAM 32

BLOCK B1 16

( 256 16 )

MUX SHIFTER (0 - 7)

16 16 16 16

Рис.1.1 Архитектура TMS320C25.

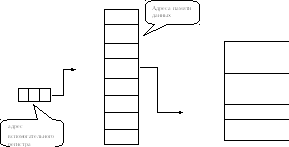

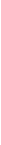

Из счетчика Из вспомогат. Регистров (ARn)

программ или

или из указателя страницы данных (DP)

счетчика и непосредственного адреса

предзахватов

16 16 16

MUX MUX

16 16

Block B2 (32 16) Block B0 (256 16)

Data/Prog RAM

Block B1 (256 16)

Data RAM 16

-

MUX

16 16

к Program Bus

Data Bus (16)

Рис. 1.2 Память данных на кристалле TMS320С25.

ПРОГРАММЫ ПРОГРАММЫ ДАННЫЕ

0 (0000)

прерывания 0 (0000) прерывания

0(0000) адресуемые

0 (0000)

прерывания 0 (0000) прерывания

0(0000) адресуемые

и резерв и резерв 5(0005) регистры

31 (001F) (внешняя) 31 (001F) (внешняя) 6(0006)

32 (0020) 32 (0020) резерв

95(005F)

внутренняя 96(0060) стр.0

EPROM/ROM блок B2

4015(0FAF) 127(007F) на кристалле 4016(0FB0) 128(0080)

резерв резерв стр.1-3

4095(0FFF) 511(01FF)

4096(1000) 512(0200)

блок B0

вшешняя внешняя на кристалле стр.4-5 767(02FF)

768(0300)

блок B1

на кристалле стр.6-7

1023(03FF)

1024(0400)

внешняя стр.8

- 511

65535(FFFF) 65535(FFFF) 65535(FFFF)

MP/MC = 1 MP/MC = 0

(режим микропроцессора) (режим микрокомпьютера)

рис. 1.3 а). Карта памяти после команды CNFD.

ПРОГРАММЫ ПРОГРАММЫ ДАННЫЕ

0 (0000) прерывания

0 (0000) прерывания 0(0000)

адресуемые

0 (0000) прерывания

0 (0000) прерывания 0(0000)

адресуемые

и резерв и резерв 5(0005) регистры

31 (001F) (внешняя) 31 (001F) (внешняя) 6(0006)

32 (0020) 32 (0020) резерв

95(005F)

внутренняя 96(0060) стр.0

EPROM/ROM блок B2

4015(0FAF) 127(007F) на кристалле 4016(0FB0) 128(0080)

резерв резерв стр.1-3

4095(0FFF) 511(01FF)

4096(1000) 512(0200)

не

вшешняя внешняя существует стр.4-5 767(02FF)

768(0300)

блок B1

на кристалле стр.6-7

1023(03FF)

1024(0400)

65279(FEFF) 65279(FEFF) внешняя

65280(FF00) блок B0 65280(FF00) блок B0 стр.8

на кристалле на кристалле - 511

65535(FFFF) 65535(FFFF) 65535(FFFF)

MP/MC = 1 MP/MC = 0

(режим микропроцессора) (режим микрокомпьютера)

рис.1.3 б). Карта памяти после команды CNFP.

Таблица 1.1

|

Регистр |

Адрес |

Назначение |

|

DRR (15-0) |

0 |

Регистр-приемник последовательного порта |

|

DXR (15-0) |

1 |

Регистр-передатчик последовательного порта |

|

TIM (15-0) |

2 |

Регистр таймера |

|

PRD (15-0) |

3 |

Регистр периода |

|

IMR (5-0) |

4 |

Регистр масок прерываний |

|

GREG (7-0) |

5 |

Регистр местоположения глобальной памяти |

Файл вспомогательных

Регистров

Регистров

AR0 0537h Карта памяти

данных

AR1 5150h Адрес

0000h

AR2 E9FCh внутренняя

Указатель память

Вспомогательного AR3 FF3Ah 03FFh

Регистра 0400h

AR4 103Bh внешняя

ARP 0 1 1 память

AR5 26B1h

FF3Ah 3121h (данные)

AR6 0008h

AR7 843Dh FFFFh

Рис.1.4 Пример коссвенной адресации с помощью вспомогательных регистров.

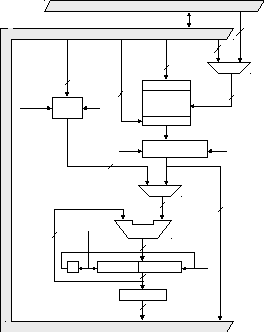

Auxiliary Register 7 (AR7) (16) Auxiliary Auxiliary

Auxiliary Register 6 (AR6) (16) 3 Register 3 Register

Auxiliary Register 5 (AR5) (16) Pointer Buffer

Auxiliary Register 4 (AR4) (16) (ARP) (3) (ARB) (3)

Auxiliary Register 3 (AR3) (16) 8 LSB

Auxiliary Register 2 (AR2) (16) or IR

Auxiliary Register 1 (AR1) (16) 16 3

Auxiliary Register 0 (AR0) (16)

16

MUX MUX

16

In B Out In A 3

Auxiliary Register 3 LSB

Arithmetic Unit or IR

(ARAU) (16)

Auxiliary Register File Bus (AFB) 3

16

Data Bus

Program Bus

Рис.1.5 Файл вспомогательных регистров.

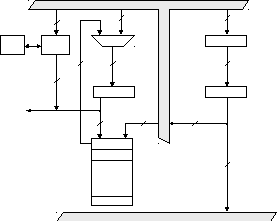

Program Bus

Data Bus 16

16

-

MUX

-

TR (16)

SX or 0 Shifter 0 16 Multiplier 16

( 0-16 )

PR(32)

SX Shifter (-6,0,1,4) 0

MUX

32 16

A B

32 SX ALU(32)

or 0 32

C ACCH (16) ACCL (16) 0

32

Shifter (0-7)

16

рис.1.6 Центральное Арифметическое Устройство

а) C MSB LSB C MSB LSB

x F F F F F F F F ACC x 0 0 0 0 0 0 0 0 ACC

+ 1 - 1

______________ ______________

1 0 0 0 0 0 0 0 0 0 F F F F F F F F

б) x 7 F F F F F F F ACC x 8 0 0 0 0 0 0 0 ACC

+ 1 (OVM=0) - 1 (OVM=0)

_____________ _____________

0 8 0 0 0 0 0 0 0 1 7 F F F F F F F

в) 1 0 0 0 0 0 0 0 0 ACC 0 F F F F F F F F ACC

+ 0 (команда - 1 (команда

_____________ ADDC) ______________ SUBB)

0 0 0 0 0 0 0 0 1 1 F F F F F F F E

рис 1.7. Примеры операций с битом переноса.

Таблица 1.2.

|

Содержимое PM |

Режим сдвига |

|

00 |

Нет сдвига |

|

01 |

Левый сдвиг на 1 разряд |

|

10 |

Левый сдвиг на 4 разряда |

|

11 |

Правый сдвиг на 6 разрядов |

Program Bus

16 16 16

MCS PFC MUX QIR (16)

( 16 ) ( 16 )

16 16 16

16

PC (16) IR (16)

К шине адреса 16 16 16

Памяти данных

Stack

( 8 16 )

16

Data Bus

Рис.1.8 Счетчик команд и стек.

CLKOUT1

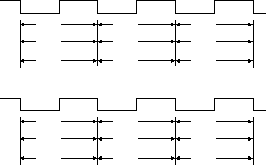

Предзахват N N+1 N+2

Декодирование N-1 N N+1

Выполонение N-2 N-1 N

Рис.1.9 Работа трехуровневого конвеера.

CLKOUT1

Предзахват N N+1 N+2

Декодирование N N+1 N+2

Выполонение N-1 N N+1

Рис.1.10 Работа двухуровневого конвеера.

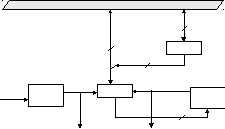

Data Bus

Data Bus

16

-

PRD (16)

16

Clock (Load)

Crystal Divide TIM (16) Zero

or by Four Detect

External

Clock

16

CLKOUT1 Tint

Рис.1.11 Блок-схема таймера.

Таблица 1.3

|

Контакты/Биты/Регистры |

Назначение |

|

CLKX CLKR DX DR FSX FSR |

Тактовая частота передатчика Тактовая частота приемника Передача последовательных данных Прием последовательных данных Кадровая синхронизация передатчика Кадровая синхронизация приемника |

|

FO TXM FSM |

Бит формата Бит режима передачи Бит режима кадровой синхронизации |

|

DXR DRR XSR RSR |

Регистр данных передатчика Регистр данных приемника Регистр сдвига передатчика Регистр сдвига приемника |

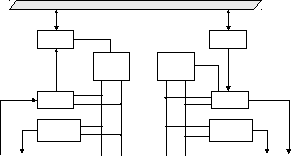

Data

Bus

Data

Bus

-

16

Load

DRR (16) DXR (16)

16 Load Load Load 16

Control Control

Logik Logik

RSR (16) XSR (16)

Byte/Word Byte/Word

Counter Counter

DR RINT FSR CLKR CLKX FSX XINT DX

Рис.1.12 Блок-схема последовательного порта.

Таблица 1.4

|

Вектор прерывания |

Размещение в памяти |

Приоритет |

Функции |

|

RS |

0 |

1 (высший) |

Внешний сигнал сброса |

|

INT0 |

2 |

2 |

Внешнее прерывание 0 |

|

INT1 |

4 |

3 |

Внешнее прерывание 1 |

|

INT2 |

6 |

4 |

Внешнее прерывание 2 |

|

TINT |

24 |

5 |

Внутреннее прерывание от таймера |

|

RINT |

26 |

6 |

Поерывание по приему от последовательного порта |

|

XINT |

28 |

7 (низший) |

Прерывание по передаче к последовательному порту |

|

TRAP |

30 |

N/A |

Адрес команды TRAP |

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

-

Зарезервировано

XINT

RINT

TINT

INT2

INT1

INT0

Рис. 1.13 Регистр масок прерываний.

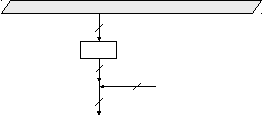

Data Bus (16)

9

DP (9)

9

7 младших разрядов из

регистра команд IR

16

рис.2.1 Прямая адресация

Data Bus (16)

3 3 вспомогательные регистры

3

ARB (3) ARP (3) AR0 (16)

3 AR1 (16)

(ARP=3) AR2 (16) 16

AR3 (16)

AR4 (16)

AR5 (16)

AR6 (16)

AR7 (16)

16 16

ARAU (16)

Рис.2.2 Косвенная адресаци

Таблица 2.1

|

15...8 7 6 5 4 3 2 1 0 в команде |

|

Коп 1 0 0 0 0 Y * ARs/ARP не изменяются |

|

Коп 1 0 0 0 1 Y *,Y Y ARP |

|

Коп 1 0 0 1 0 Y *- ARn-1 ARn |

|

Коп 1 0 0 1 1 Y *-,Y ARn -1 ARn Y ARP |

|

КОп 1 0 1 0 0 Y *+ ARn+1 ARn |

|

КОп 1 0 1 0 1 Y *+,Y ARn+1 ARn Y ARP |

|

КОп 1 1 0 1 0 Y *0- ARn-AR0ARn |

|

КОп 1 1 0 1 1 Y *0-,Y ARn-AR0ARn Y ARP |

|

КОп 1 1 0 0 0 Y *BR0- ARn-rcAR0ARn |

|

КОп 1 1 0 0 1 Y *BR0-,Y ARn-rcAR0ARn Y ARP |

|

КОп 1 1 1 0 0 Y *0+ ARn+AR0ARn |

|

КОп 1 1 1 0 1 Y *0+,Y ARn+AR0ARn Y ARP |

|

Коп 1 1 1 1 0 Y *BR0+ ARn+rcAR0ARn |

|

Коп 1 1 1 1 1 Y *BR0+,Y ARn+rcAR0ARn Y ARP |

rc - распространение инверсии переноса.

Таблица 2.2

|

|

|

АСС аккумулятор |

|

ARn вспомогательный регистр n (AR0-AR7 являются определенными символами ассемблера, равными 0-7 соответственно) |

|

ARP указатель вспомогательного регистра |

|

В 4-разрядное поле, определяющее код |

|

CM 2-разрядное поле, определяющее режим сравнения |

|

D поле адреса памяти данных |

|

DATn метка, определяющая ячейку памяти данных n |

|

dma адрес памяти данных |

|

DP указатель страницы данных |

|

FO бит состояния формата |

|

I бит метода адресации |

|

INTM бит флага режима прерывания |

|

K поле непосредственного операнда |

|

P регистр произведения |

|

PA адрес порта (PA0-PA15) являются определенными символами ассемблер равными 0-15, соответственно |

|

PC счетчик программ |

|

PM 2-разрядное поле, определяющий код сдвига выходного сигнала Р-регистра |

|

pma адрес памяти программ |

|

PRGn метка, определяющая ячейку памяти программ |

|

R 3-разрядное поле операнда, определяющего вспомогательный регистр |

|

S 4-разрядный код сдвига влево |

|

T Т-регистр |

|

TOS вершина стека |

|

X 3-разрядное поле сдвига влево аккумулятора |

|

символ присваивания |

|

| | указывает абсолютную величину |

|

Italic элементы с шрифтом Italic определяются пользователем |

|

[ ] элементы в квадратных скобках являются дополнительными |

|

( ) указывают "содержимое чего-либо" |

|

{ } элементы в фигурных скобках являются альтернативными, один из них должен быть выбран |

|

Пробелы или интервалы должны иметь место там, где показано. |

Таблица 2.3

# - команды недоступны для TMS320C20.

Сл. – количество слов, занимаемое в памяти программ.

|

Инстр. |

Описание |

Операция |

Сл. |

|

КОМАНДЫ, ВЫПОЛНЯЮЩИЕ ОПЕРАЦИИ С АККУМУЛЯТОРОМ |

|||

|

ABS |

Абсолютная величина АСС |

None |

1 |

|

ADD |

Сложение с АСС со сдвигом |

dma[,shift]; ind [,shift[,next ARP]] |

1 |

|

ADDC # |

Сложение с АСС с переносом |

dma; ind[,next ARP] |

1 |

|

ADDH |

Сложение со старшими рзрядами АСС |

dma; ind[,next ARP] |

1 |

|

ADDK # |

Сложение с АСС короткой константы |

constant |

1 |

|

ADDS |

Сложение с АСС без расширения знака |

dma |

1 |

|

ADDT |

Сложение с АСС со сдвигом, определенным Т-рег. |

dma; ind[,next ARP] |

1 |

|

ADLK |

Сложение с АСС длинной константы со сдвигом |

constant[,shift] |

2 |

|

AND |

Логическое “И” с АСС |

dma; ind[,next ARP] |

1 |

|

ANDK |

Логическое “И” короткой константы с АСС |

constant[,shift] |

2 |

|

CMPL |

Дополнение АСС |

None |

1 |

|

LAC |

Загрузка АСС со сдвигом |

dma[,shift]; ind [,shift[,next ARP]] |

1 |

|

LACK |

Загрузка АСС короткой константой |

constant |

1 |

|

LACT |

Загрузка АСС со сдвигом, определеным Т-рег. |

dma; ind[,next ARP] |

1 |

|

LALK |

Загрузка АСС длинной константой |

constant[,shift] |

2 |

|

NEG |

Логическое “НЕ” с АСС |

None |

1 |

|

NORM |

Нормализация АСС |

ind |

1 |

|

OR |

Логическое “ИЛИ” с АСС |

dma; ind[,next ARP] |

1 |

|

ORK |

Логическое “ИЛИ” короткой константы с АСС |

constant[,shift] |

2 |

|

ROL # |

Вращение АСС влево |

None |

1 |

|

ROR # |

Вращение АСС вправо |

None |

1 |

|

SACH |

Сохранить старшее слово АСС со сдвигом |

dma[,shift]; ind [,shift[,next ARP]] |

1 |

|

SACL |

Сохранить младшее слово АСС со сдвигом |

dma[,shift]; ind [,shift[,next ARP]] |

1 |

|

SBLK |

Вычитание из АСС короткой константы со сдвигом |

constant[,shift] |

2 |

|

SFL |

Сдвиг АСС влево |

None |

1 |

|

SFR |

Сдвиг АСС вправо |

None |

1 |

|

SUB |

Вычитание из АСС со сдвигом |

dma[,shift]; ind [,shift[,next ARP]] |

1 |

|

SUBB # |

Вычитание из АСС с переносом |

dma; ind[,next ARP] |

1 |

|

SUBC |

Вычитание условное |

dma; ind[,next ARP] |

1 |

|

SUBH |

Вычитание из старшего слова АСС |

dma; ind[,next ARP] |

1 |

|

SUBK # |

Вычитание из АСС короткой константы |

constant |

1 |

|

SUBS |

Вычит. из младш. слова АСС без расширения знака |

dma; ind[,next ARP] |

1 |

|

SUBT |

Вычитание из АСС со сдвигом, определенным Т-рег. |

dma; ind[,next ARP] |

1 |

|

XOR |

“Исключ. ИЛИ” с АСС |

dma; ind[,next ARP] |

1 |

|

XORK |

“Исключ. ИЛИ” АСС и константы со сдвигом |

constant[,shift] |

2 |

|

ZAC |

Обнуление АСС |

None |

1 |

|

ZALH |

Обнуление мл. слова АСС и загр. числа в ст. слово АСС |

dma; ind[,next ARP] |

1 |

|

ZALR # |

Что и ZALH, но со вращением |

dma; ind[,next ARP] |

1 |

|

ZALS |

Обнуление АСС, загр. мл. слова АСС без расшир. знака |

dma; ind[,next ARP] |

1 |

|

КОМАНДЫ, ВЫПОЛНЯЮЩИЕ ОПЕРАЦИИ СО ВСПОМОГАТЕЛЬНЫМИ РЕГИСТРАМИ И УКАЗАТЕЛЕМ СТРАНИЦ |

|||

|

ADRK |

Сложение со вспомогат. регистром короткой константы |

constant |

1 |

|

CMPR |

Сравнение вспомогат. регистра с регистром AR0 |

constant |

1 |

|

LAR |

Загрузка вспомогательного регистра |

AR, dma; AR, ind[,next ARP] |

1 |

|

LARK |

Загрузка вспомогательного регистра короткой константой |

AR, constant |

1 |

|

LARP |

Загрузка указателя вспомогательного регистра |

constant |

1 |

|

LDP |

Загрузка указателя страницы памяти данных |

dma; ind[,next ARP] |

1 |

|

LDPK |

Загр. указателя стр. памяти данных короткой константой |

constant |

1 |

|

LRLK |

Загрузка вспомогательного регистра длинной константой |

AR, constant |

2 |

|

MAR |

Изменение вспомогательного регистра |

dma; ind[,next ARP] |

1 |

|

SAR |

Сохранение вспомогательного рагистра |

AR, dma; AR, ind[,next ARP] |

1 |

|

SBRK |

Вычитание из вспомогат. регистра короткой константы |

constant |

1 |

|

КОМАНДЫ, ВЫПОЛНЯЮЩИЕ ОПЕРАЦИИ С ПОРТАМИ ВВОДА-ВЫВОДА И ПАМЯТЬЮ ДАННЫХ |

|||

|

BLKD |

Перемещение блока из памяти данных в память данных |

dma1, dma2; dma1, ind [,next ARP] |

2 |

|

BLKP |

Перемещение блока из памяти программ в память данных |

pma, dma; pma, ind [,next ARP] |

2 |

|

DMOV |

Перемещение данных в памяти данных |

dma, ind [,next ARP] |

1 |

|

FORT |

Форматирование регистров последовательного порта |

constant |

1 |

|

IN |

Ввод данных из порта |

dma PA; ind, PA [,next ARP] |

1 |

|

OUT |

Вывод данных из порта |

dma PA; ind, PA [,next ARP] |

1 |

|

RFSM # |

Сбросить бит режима кадровой синхрониз. посл. порта |

None |

1 |

|

RTXM |

Сбросить бит режима передачи последовательного порта |

None |

1 |

|

RXF |

Сбросить внешний флаг |

None |

1 |

|

SFSM # |

Установить бит режима кадровой синхрониз. посл. порта |

None |

1 |

|

STXM |

Установить бит режима передачи последов. порта |

None |

1 |

|

SXF |

Установить внешний флаг |

None |

1 |

|

TBLR |

Читать таблицу |

dma, ind [,next ARP] |

1 |

|

TBLW |

Записать таблицу |

dma, ind [,next ARP] |

1 |

|

КОМАНДЫ УСЛОВНОГО И БЕЗУСЛОВНОГО ВЕТВЛЕНИЯ |

|||

|

B |

Безусловное ветвление |

pma, ind [,next ARP] |

2 |

|

BACC |

Ветвление по адресу, указанному АСС |

None |

1 |

|

BANZ |

Ветвление, если вспомогательный регистр 0 |

pma, ind [,next ARP] |

2 |

|

BBNZ |

Ветвление, если бит ТС 0 |

pma, ind [,next ARP] |

2 |

|

BBZ |

Ветвление, если бит ТС 0 |

pma, ind [,next ARP] |

2 |

|

BC # |

Ветвление при переносе |

pma, ind [,next ARP] |

2 |

|

BGEZ |

Ветвление, если содержимое АСС 0 |

pma, ind [,next ARP] |

2 |

|

BGZ |

Ветвление, если содержимое АСС 0 |

pma, ind [,next ARP] |

2 |

|

BIOZ |

Ветвление, если бит ввода-вывода = 0 |

pma, ind [,next ARP] |

2 |

|

BLEZ |

Ветвление, если содержимое АСС 0 |

pma, ind [,next ARP] |

2 |

|

BLZ |

Ветвление, если содержимое АСС 0 |

pma, ind [,next ARP] |

2 |

|

BNC # |

Ветвление, если нет переноса |

pma, ind [,next ARP] |

2 |

|

BNV |

Ветвление, если нет переполнения |

pma, ind [,next ARP] |

2 |

|

BNZ |

Ветвление, если содержимое АСС 0 |

pma, ind [,next ARP] |

2 |

|

BV |

Ветвление , если есть переполнение |

pma, ind [,next ARP] |

2 |

|

BZ |

Ветвление, если содержимое АСС = 0 |

pma, ind [,next ARP] |

2 |

|

CALA |

Косвенный вызов подпрограммы |

None |

1 |

|

CALL |

Вызов подпрограммы |

pma, ind [,next ARP] |

2 |

|

RET |

Возврат из подпрограммы |

None |

1 |

|

КОМАНДЫ УМНОЖЕНИЯ И КОМАНДЫ, ВЫПОЛНЯЮЩИЕ ОПЕРАЦИИ Т- И Р- РЕГИСТРАМИ |

|||

|

APAC |

Сложение Р-рег. к АСС |

None |

1 |

|

LPH |

Загрузка старших разрядов Р-регистра |

dma; ind[,next ARP] |

1 |

|

LT |

Загрузка Т-регистра |

dma; ind[,next ARP] |

1 |

|

LTA |

Загрузка Т-рег. и сложение с АСС предыдущего произвед. |

dma; ind[,next ARP] |

1 |

|

LTD |

То же, что и LTA, но с движением данных |

dma; ind[,next ARP] |

1 |

|

LTP |

Загрузка Т-рег. и сохранение Р-рег. в АСС |

dma; ind[,next ARP] |

1 |

|

LTS |

Загрузка Т-рег. и вычитание предыдущего произвед. |

dma; ind[,next ARP] |

1 |

|

MAC |

Умножение и сложение |

pma, dma; pma, ind [,next ARP] |

2 |

|

MACD |

Умножение и сложение с движением данных |

pma, dma; pma, ind [,next ARP] |

2 |

|

MPY |

Умножение |

dma; ind[,next ARP] |

1 |

|

MPYA # |

Умножение и сложение с АСС предыдущего произвед. |

dma; ind[,next ARP] |

1 |

|

MPYK |

Умножение на константу |

constant |

1 |

|

MPYS # |

Умножение и вычитание из АСС предыдущего произвед. |

dma; ind[,next ARP] |

1 |

|

MPYU # |

Умножение беззнаковое |

dma; ind[,next ARP] |

1 |

|

PAC |

Сохранение Р-рег. в АСС |

None |

1 |

|

SPAC |

Вычитание Р-рег. из АСС |

None |

1 |

|

SPH # |

Сохранение старшего слова Р-рег. |

dma; ind[,next ARP] |

1 |

|

SPL # |

Сохранение младшего слова Р-рег. |

dma; ind[,next ARP] |

1 |

|

SPM |

Задание режима сдвига на выходе Р-рег. |

constant |

1 |

|

SQRA |

Возведение в квадрат и слож. с АСС предыдущ. произв. |

dma; ind[,next ARP] |

1 |

|

SGRS |

Возведение в квадрат и вычит. предыдущ. произв. из АСС |

dma; ind[,next ARP] |

1 |

Биты

Обознач.

Арифметическая операция

Биты

Обознач.

Арифметическая операция

Символ Значение

Символ Значение