Ris_DSP / TZOS_red4_ch2_C25_Tablet

.pdf

113

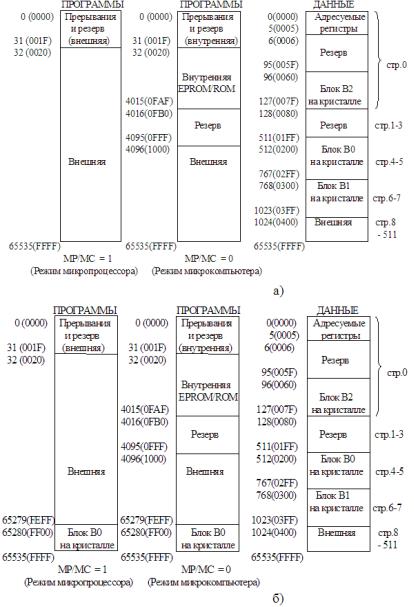

Рис.4.3 Карта памяти. а) - после команды CNFD,

б) - после команды CNFP

114

Если для хранения команд используется высокоскоростная внешняя память или память RAM на кристалле, TMS320C25 выполняет обработку на максимальной скорости без циклов ожидания. Однако к процессору можно подключать более медленную, а значит и более дешевую внешнюю память. Для этой цели используется входной сигнал READY. Загрузка кодов команд из медленной внешней памяти во внутреннюю быстродействующую оперативную память RAM, позволяет увеличить скорость вычислений и одновременно снизить стоимость системы.

4.3.4АДРЕСУЕМЫЕ РЕГИСТРЫ

Впределах внутреннего адресного пространства данных процессора расположены шесть адресуемых регистров (Таблица 4.7, рис.4.3).

Доступ к адресуемым регистрам осуществляется так же, как и к ячейкам памяти данных. Однако команда BLKD не перемещает информацию из области адресуемых регистров.

|

Адрес |

Таблица 4.7 |

Регистр |

Назначение |

|

DRR (15-0) |

0 |

Регистр-приемник последовательного порта |

DXR (15-0) |

1 |

Регистр-передатчик последовательного порта |

TIM (15-0) |

2 |

Регистр таймера |

PRD (15-0) |

3 |

Регистр периода |

IMR (5-0) |

4 |

Регистр масок прерываний |

GREG(7-0) |

5 |

Регистр местоположения глобальной памяти |

4.3.5 ВСПОМОГАТЕЛЬНЫЕ РЕГИСТРЫ

TMS320C25 имеет файл из восьми вспомогательных регистров (AR0AR7). Вспомогательные регистры могут быть использованы для косвенной адресации памяти данных или для временного хранения информации. Косвенная адресация (рис.4.4) дает возможность разместить адрес операнда, находящегося в памяти данных, в одном из восьми

115

вспомогательных регистров. Один из этих регистров ARn можно выбрать, загружая в указатель вспомогательного регистра (ARP) значения от 0 до 7. Вспомогательные регистры и указатель вспомогательного регистра могут быть загружены как из памяти данных, так и с помощью непосредственного операнда определенного в коде команды. Файл вспомогательных регистров соединен с арифметическим устройством вспомогательных регистров ARAU (рис.4.5). После адресации памяти данных с помощью ARn, ARAU может автоматически увеличивать или уменьшать текущий адрес в ARn на 1 либо на значение, содержащееся в AR0. Это позволяет адресовать сложные массивы данных. Как видно из рис.4.5, AR0 постоянно подсоединен к одному из входов ARAU. Другой вход подсоединяется к текущему ARn.

ARAU выполняет следующие операции:

ARn+AR0→ARn |

- к содержимому текущего AR прибавляется |

ARn-AR0→ARn |

содержимое AR0. |

- из содержимого текущего AR вычитается |

|

ARn+1→ARn |

содержимое AR0. |

- автоинкремент текущего AR на 1. |

|

ARn-1→ARn |

- автодекремент текущего AR на 1. |

ARn→ARn |

- ARn остается без изменений. |

ARn+IR(7-0)→ARn |

- к содержимому текущего AR прибавляется |

ARn-IR(7-0)→ARn |

непосредственная 8-разрядная константа. |

- из содержимого текущего AR вычитается |

|

ARn+rcAR0→ARn |

непосредственная 8-разрядная константа. |

- индексация с инверсией битов: к текущему AR |

|

|

прибавляется AR0 с распостранением переноса вправо |

ARn-rcAR0→ARn |

(reverse-carry (rc)). |

- индексация с инверсией битов: из текущего AR |

|

|

вычитается AR0 с распостранением переноса вправо |

|

(reverse-carry (rc)). |

116

Рис.4.4. Пример косвенной адресации с помощью вспомогательных регистров

Рис.4.5. Файл вспомогательных регистров

117

По желанию программиста ARAU можно применять в качестве простого арифметического устройства. Оно выполняет 16-разрядную беззнаковую арифметику в то время, как CALU выполняет 32-разрядную арифметику в дополнительном коде.

Буфер вспомогательного регистра ARB используется для хранения значения указателя ARP во время программных вызовов и прерываний.

4.3.6 ЦЕНТРАЛЬНОЕ АРИФМЕТИКО-ЛОГИЧЕСКОЕ УСТРОЙСТВО (CALU)

Центральное арифметико-логическое устройство (CALU) содержит 16разрядный масштабирующий регистр сдвига, 16x16 параллельный умножитель, 32-разрядное арифметико-логическое устройство (ALU), 32разрядный аккумулятор и несколько дополнительных сдвиговых регистров, расположенных на выходе умножителя и аккумулятора. Функциональная схема CALU представлена на рис.4.6.

Любая операция ALU выполняется в следующей последовательности:

1.Данные захватываются из RAM на шину данных.

2.Данные проходят через масштабирующий сдвиговый регистр и через ALU, в котором выполняются арифметические операции.

3.Результат передается в аккумулятор.

Один вход в ALU всегда соединен с выходом аккумулятора, а второй может получать данные либо из регистра произведения (PR) умножителя, либо из памяти через масштабирующий сдвиговый регистр.

Масштабирующий сдвиговый регистр имеет 16-разрядный вход с шины данных и 32-разрядный выход в ALU. Сдвиговый регистр выполняет левый сдвиг на 0-16 бит. Величина сдвига указывается в команде. При этом младшие разряды заполняются нулями.

Сдвиговые регистры, подсоединенные к выходам умножителя и аккумулятора позволяют выполнить масштабирование, выделение бита, расширенную арифметику и контролировать возможные переполнения.

32-разрядное ALU совместно с ACC выполняют арифметические и логические операции. Результат любой операции выполняемой в ALU помещается в аккумулятор.

118

Рис.4.6 Центральное Арифметическое Устройство

Данные, которые подаются на обработку в ALU могут быть предварительно промасштабированы в сдвиговом регистре.

На один из входов ALU всегда подается содержимое аккумулятора, а другой вход может быть соединен либо с регистром произведения (PR) умножителя либо с выходом масштабирующего регистра.

119

32-разрядный аккумулятор ACC для удобства разделен на два 16-ти разрядных сегмента: ACCH (аккумулятор старший) и ACCL (аккумулятор младший). Прежде чем поместить данные на шину памяти, содержимое ACC может быть сдвинуто на (0-7) разрядов влево. При этом содержимое самого аккумулятора не изменяется. Когда ACCH сдвигается влево, младшие разряды выбираются из ACCL, а старшие теряются. Когда ACCL сдвигается влево, младшие разряды заполняются нулями, а старшие теряются.

Режим насыщения ALU при переполнении может быть запрограммирован при помощи команд SOVM/ROVM (установить/сбросить режим переполнения). Если аккумулятор находится в режиме насыщения при переполнении и произошло переполнение, устанавливается флаг переполнения и аккумулятор загружается наибольшим положительным (7FFFFFFFh) или отрицательным (80000000h) числом, в зависимости от знака переполнения. Если режим насыщения не установлен (бит OVM сброшен), переполненный результат загружается в аккумулятор без изменений.

TMS320C25 выполняет команды ветвления, в зависимости от состояния ALU. Команда BACC (перейти по адресу, расположенному в аккумуляторе) позволяет вычислять адрес перехода. Команды BIT/BITT, не изменяя содержимого аккумулятора, позволяют определять значение конкретных разрядов в любом слове памяти данных.

Аккумулятор TMS320C25 снабжен битом переноса, который устанавливается или сбрасывается в зависимости от операций выполняемых процессором. Бит переноса удобен при работе с переполнениями. Бит переноса изменяется при выполнении большинства арифметических команд, а также команд сдвига, но не изменяется при загрузке аккумулятора, логических операциях, или при других неарифметических или управляющих операциях. Он также не изменяется при выполнении команд умножения MPY, MPYK и MPYU, но изменяется командами MAC и MACD.

Бит переноса устанавливается, если при сложении или загрузке аккумулятора генерируется перенос, или сбрасывается, если при вычитании возникает заем из 16 разряда (рис.4.7а). Во всех остальных

120

случаях он сбрасывается при сложении и устанавливается при вычитании (рис.4.7б). Команды ADDC (прибавить с переносом) и SUBB (вычесть с заемом) позволяют воспользоваться значением переноса полученным в предыдущих командах сложения/вычитания (рис.4.7в).

C |

MSB LSB |

|

C |

MSB LSB |

|

|||||||

x FFFF FFFF |

ACC |

x 0000 0000 |

ACC |

|

||||||||

+ |

1 |

|

|

- |

|

|

1 |

|

|

|

а) |

|

1 0000 0000 |

|

|

0 FFFF FFFF |

|

|

|

||||||

x 7FFF FFFF |

ACC |

x 8000 0000 |

ACC |

|

||||||||

+ |

1 |

|

(OVM=0) |

- |

|

|

1 (OVM=0) |

б) |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

0 8000 0000 |

|

|

1 7FFF FFFF |

|

|

|||||||

|

|

|

|

|

||||||||

1 0000 0000 |

|

ACC |

|

|

|

0 FFFF FFFF ACC |

|

|||||

+ |

0 (команда ADDC) |

- |

|

1 (команда SUBB) в) |

||||||||

|

|

|

|

|

|

|

|

|

|

|

||

0 0000 0001 |

|

|

|

|

|

1 FFFF FFFE |

|

|||||

Рис 4.7. Примеры операций с битом переноса

Аппаратный умножитель MPL работает с 16-разрядными числами в дополнительном коде. Умножитель содержит два регистра:

−16-разрядный регистр (TR) для хранения одного сомножителя;

−32-разрядный регистр произведения (PR) для хранения результата произведение.

Первый сомножитель загружается в регистр TR командой LT (загрузить

T-регистр) с шины данных. Команда MPY (умножить) загружает с шины данных второй сомножитель и выполняет перемножение. Умножение может также выполняться с использованием непосредственного операнда.

Влюбом случае произведение вычисляется за два командных цикла. Команды умножения/накопления (MAC и MACD) позволяют загружать

одновременно оба сомножителя с шины команд и данных. Использование команд MAC и MACD с командами повторения RPT и RPTK позволяет

121

выполнять операции умножения/накопления за один командный цикл. Команды MAC и MACD могут загружать операнды как из внутренней, так и из внешней памяти. Команды SQRA (возвести в квадрат/сложить) и SQRS (возвести в квадрат/вычесть) для вычисления квадрата загружают одно и то же число с шины данных на оба входа умножителя.

32-разрядное произведение размещается в 32-разрядном регистре произведения (PR). Содержимое PR может быть передано в ALU без изменений или с предварительным сдвигом.

Режим сдвига определяется в поле PM регистра состояния ST1 (Таблица 4.8).

|

Таблица 4.8 |

|

Содержимое PM |

Режим сдвига |

|

00 |

Нет сдвига |

|

01 |

Левый сдвиг на 1 |

разряд |

10 |

Левый сдвиг на 4 |

разряда |

11 |

Правый сдвиг на 6 разрядов |

|

4.3.7 УПРАВЛЕНИЕ ПРОЦЕССОРОМ

Управление процессором TMS320С25 осуществляется расположенными на кристалле счетчиком команд, аппаратным стеком, таймером, счетчиком повторений, тремя маскируемыми пользователем прерываниями, внутренними прерываниями, возникающими при работе последовательного порта или таймера, и внешним сигналом сброса.

TMS320C25 содержит 16-разрядный счетчик команд (PC) и 8-уровневый аппаратный стек Stack для хранения содержимого PC (рис.4.8). Счетчик команд для выборки команд адресует внешнюю и внутреннюю память программ. Стек используется во время прерываний и вызовов подпрограмм. Счетчик команд через шину адреса памяти команд (PAB) адресует память программ, расположенную либо на кристалле, либо вне кристалла. Благодаря PAB, команды захватываются из памяти программ и загружаются в регистр команд (IR). После того, как IR загружен, PC инициирует следующий цикл захвата кода команды. PC может адресовать

122

блок B0 RAM, расположенный на кристалле, если B0 используется в качестве памяти программ, а также внешнюю память программ через шину адреса A15-A0.

Рис.4.8 Счетчик команд и стек

TMS320C25 имеет возможность выполнить одну команду N+1 раз. N определяется содержимым счетчика повторений (RPTC). После каждого выполнения команды содержимое RPTC уменьшается на 1, пока RPTC не обнулится.

Использование счетчика повторений полезно при выполнении команд NORM (нормировать содержимое аккумулятора), MACD (умножить и добавить к АСС с перемещением данных), SUBC (условное вычитание). Использование счетчика повторений с многоцикловыми командами типа MACD, позволяет выполнять их более эффективно (за один цикл).

Операции со стеком производятся при помощи команд PUSH и POP. Всякий раз, когда содержимое PC записывается на вершину стека, предыдущее содержимое каждого уровня стека проталкивается вниз, а