TheARMcornA chitecture

RISC

MachineOd rov Roman gr. 345

November 2011

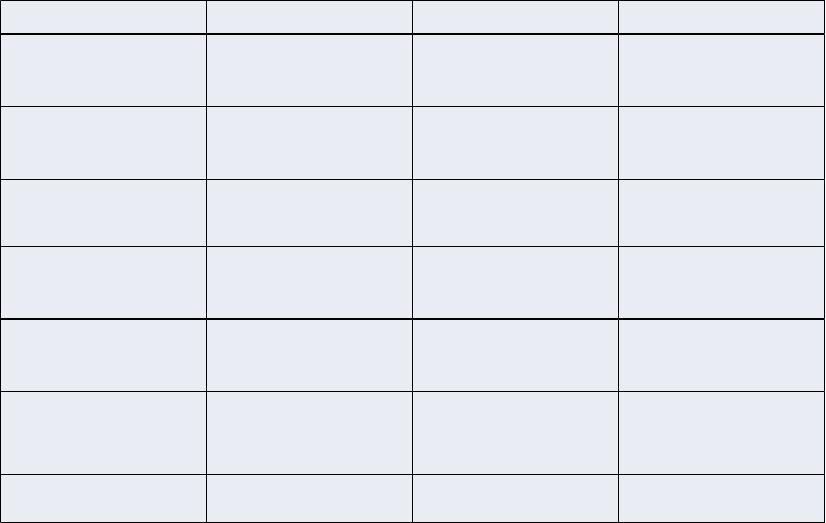

Timeline

Version |

Year |

Features |

Implementation |

V1 |

1985 |

The first |

ARM1 |

|

|

commercial RISC |

|

V2 |

1987 |

Coprocessor |

ARM2, ARM3 |

|

|

support |

|

V3 |

1992 |

MMU |

ARM6, ARM7 |

|

|

Thumb |

ARM7TDMI, ARM8, |

V4 |

1996 |

SystemModeOperati |

ARM9TDMI, |

|

|

ngs |

StrongARM |

|

|

DigitalSignalProcess |

|

V5 |

1999 |

ing and Jazelle |

ARM10, Xscale |

|

|

extensions |

|

V6 |

2001 |

SIMD, Thumb-2, |

ARM11 |

|

|

TrustZone |

|

V7 |

2005 |

|

Cortex |

Architecture

ARM11 Processor Family Features:

•Thumb® instruction set reduces memory bandwidth and size requirements by up to 35%

•Jazelle® technology for efficient embedded Java execution

•DSP extensions

•SIMD (Single Instruction Multiple Data) media processing extensions deliver up to 2x performance for video processing

•TrustZone® technology

•Thumb-2 technology

•High performance processor

•8-stage pipeline (9 stages for ARM1156T2(F)-S)

•Separate load-store and arithmetic pipelines

•Branch Prediction

•Vector Floating Point coprocessor (for example for 3D-graphics accelerating)

Processors types

ARM-processors

‘A’ - application ‘R’ – real-time

‘M’ - microcontroller

* Introduced in V7-architecture

Processor modes:

•User : unprivileged mode under which most tasks run

•FIQ : entered when a high priority (fast) interrupt is raised

•IRQ : entered when a low priority (normal) interrupt is raised

•Supervisor : entered on reset and when a Software Interrupt instruction is executed

•Abort : used to handle memory access violations

•Undef : used to handle undefined instructions

•System : privileged mode using the same registers as user mode

Conditional Execution

C-code

while (i != j)

{

if (i > j) i -= j;

else

j -= i;

}

ARM Assembly-code

loop CMP Ri, Rj; set condition «NE» if (i != j),

; |

"GT" if (i > |

j),

;or "LT" if (i <

j)

SUBGT Ri, Ri, Rj ; if "GT”(greater than),i = i-j;

SUBLT |

Rj, Rj, Ri |

; if "LT" (less than), j = |

j-i; |

loop |

|

BNE |

; if "NE" (not |

equal),then loop

Thumb state

The Thumb instruction set was created after analyzing instructions often used to give better code density and better performance.

For most instructions generated by compiler:

•Conditional execution is not used

•Source and destination registers identical

•Only Low registers used

•Constants are of limited size

ADDS r2,r2,#1

32-bit ARM Instruction

ADD r2,#1

16-bit Thumb

Instruction

Other features

•Thumb-2 state (extended Thumb)

•Jazelle (executes most bytecodes in hardware and some in highly optimized ARM code)

•NEON (extended SIMD)

•VFP (Vector Floating Point). It’s a technology that FPUs are based on

•TrustZone Technology (provides 2 virtual processors, thus 2 execution “worlds” can be chosen…)

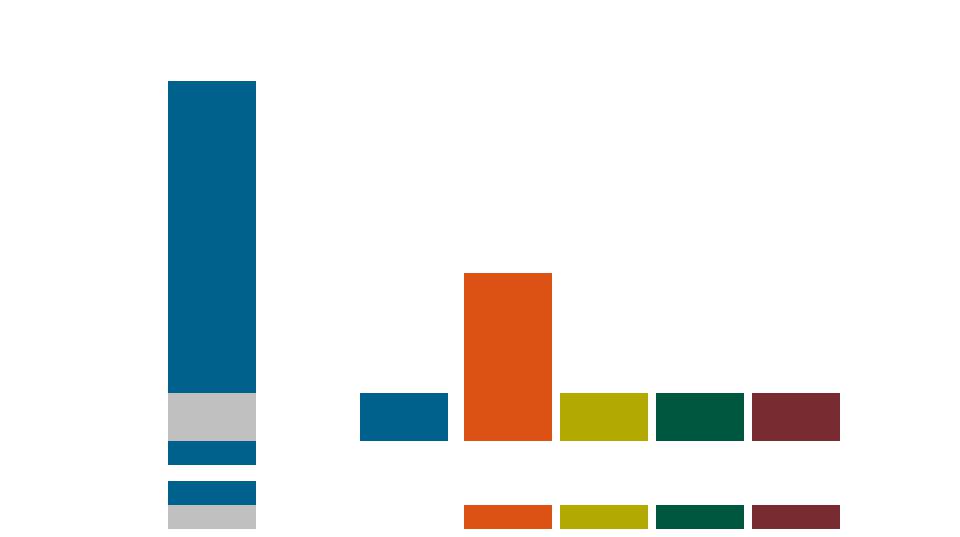

Register set

•ARM has 37 registers all of which are 32-bits long.

–1 dedicated program counter

–1 dedicated current program status register

–5 dedicated saved program status registers

–30 general purpose registers

•The current processor mode governs which of several banks is accessible. Each mode can access

–a particular set of r0-r12 registers

–a particular r13 (the stack pointer, sp) and r14 (the link register, lr)

–the program counter, r15 (pc)

–the current program status register, cpsr

Privileged modes (except System) can also access

– a particular spsr (saved program status register)

Register set

Current Visible |

|

|

|

|

|

|

|

|

|

|||

Abort |

Registers |

|

|

|

|

|

|

|

|

|

||

|

r0 |

|

|

|

|

|

|

|

|

|

|

|

Mode |

|

|

|

|

|

|

|

|

|

|

|

|

|

r1 |

|

|

|

|

|

Banked out |

|||||

|

|

r2 |

|

|

|

|

|

|

|

|

|

|

|

|

r3 |

|

|

|

|

|

Registers |

|

|||

|

|

r4 |

|

|

|

|

|

|

||||

|

|

r5 |

|

User |

FIQ |

IRQ |

|

SVC |

Undef |

|||

|

|

r6 |

|

|

||||||||

|

|

r7 |

|

|

|

|

|

|

|

|

|

|

|

|

r8 |

|

|

|

r8 |

|

|

|

|

|

|

|

|

r9 |

|

|

|

r9 |

|

|

|

|

|

|

|

|

r10 |

|

|

|

r10 |

|

|

|

|

|

|

|

|

r11 |

|

|

|

r11 |

|

|

|

|

|

|

|

|

r12 |

|

|

|

r12 |

|

|

|

|

|

|

|

|

r13 (sp) |

|

r13 (sp) |

|

r13 (sp) |

|

r13 (sp) |

|

r13 (sp) |

|

r13 (sp) |

|

|

r14 (lr) |

|

r14 (lr) |

|

r14 (lr) |

|

r14 (lr) |

|

r14 (lr) |

|

r14 (lr) |

|

|

r15 (pc) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

cpsr |

|

|

|

|

|

|

|

|

|

|

|

|

spsr |

|

|

|

spsr |

|

spsr |

|

spsr |

|

spsr |