- •Московский институт электронной техники (tу)

- •Логического элемента в n-моп базисе”

- •Задание на курсовую работу

- •Упрощение заданной функции с помощью карты Карно.

- •Справочные данные и принятые обозначения.

- •Разработка электрической схемы в заданном схемотехническом базисе.

- •Расчет характеристик схемы с помощью программы pspice.

- •Технологический маршрут формирования n-моп транзистора.

- •Список используемой литературы :

Расчет характеристик схемы с помощью программы pspice.

С помощью представленной ниже программы, произведен расчет передаточной и переходной характеристик схемы логического элемента. Также по полученным характеристикам были определены статические и динамические параметры данного элемента.

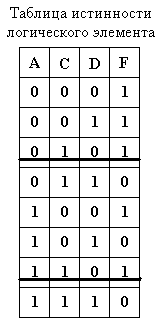

Для определения напряжений подаваемых на вход составляем таблицу истинности. Из нее выбираем такой набор входных напряжений, когда при изменении только одного входа логическая схема переключается.

Программа :

v1 1 0 dc 7

v2 3 0 pulse (5 0.6 10n 1n 1n 800n 900n)

v3 6 0 dc 5

v4 5 0 dc 0.6

c 2 0 0.5p

m1 1 1 2 0 nm l=21u w=6u

m2 2 3 4 0 nm l=6u w=19u

m3 4 5 0 0 nm l=6u w=19u

m4 4 6 0 0 nm l=6u w=19u

.model nm nmos (level=1 tox=50n vto=1.1 kp=4.248e-5 gamma=0.5 uo=600 xj=0.7)

.tran 3n 900n

.dc v2 0 5 0.01

.probe

.end

Параметры МДП-ключа:

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Определение статических параметров:

U0-уровень логического нуля при U0вх=U0вых

U1-уровень логической единицы при U1вх=U1вых

U=U1-U0 –размах логического сигнала

Uп –напряжение переключения передаточной характеристики, точка неустойчивого равновесия Uвх=Uвых

Uпз– напряжение помехозащищенности, характеризует минимальную величину входного напряжения, при котором происходит переход схемы в другое логическое состояние

U0пз=Uп-U0, U1пз=U1-Uп

Uд- напряжение в точках единичного усиления, то есть в точках тангенс угла наклона в которых равен единице

Uдд- ширина активной области. Диапазон напряжений, в котором происходит переключение схемы.

Uдд=U1д-U0д

Uпу- напряжение помехоустойчивости, определяется максимальной величиной входного напряжения, при котором схема сохраняет свое логическое состояние

U0пу=U0д-U0, U1пу=U1-U1д

Определение динамических характеристик:

tср- время среза выходного сигнала. Это время переключения выходного сигнала из состояния “1” в состояние “0”.Определяется по уровню 0,9-0,1 от максимального изменения выходного напряжения.

tф- время фронта определяется временем переключения выходного сигнала из состояния “0” в “1”. Определяется по уровню 0,1-0,9 изменеия выходного сигнала

t01зд- время задержки распространения выходного сигнала при переключении из “0”в “1” относительно входного сигнала. Определяется по уровню 0,5 изменения выходного сигнала

t10зд- время задержки распространения выходного сигнала при переключении из “1”в “0”. Определяется аналогично предыдущему.

tздср- среднее время задержки определяется как среднее арифметическое: tздср=(t01зд+t10зд)/2.

Технологический маршрут формирования n-моп транзистора.

Здесь вкратце представлен технологический маршрут изготовления n-канального МДП транзистора с самосовмещенным (поликремниевым) затвором. Он состоит из нескольких этапов :

Формирование охранных локальных областей (первая фотолитография). Так как операция длительная то вырастает толстый окисел – локос.

Формирование подзатворного диэлектрика – тонкого качественного окисла (без фотошаблона).

Формирование поликремниевого (Si*) затвора (вторая фотолитография). Для исключения контакта между стоком и истоком делают вылет затвора (перекрытие поликремнием тонкого окисла).

Форирование областей стока и истока (производится без фотошаблона) с помощью ионного легирования или диффузии.

Ф

ормирование

контактных окон (третья фотолитография).

ормирование

контактных окон (третья фотолитография).

Метализация (четвертая фотолитография).

Пассивация.Защита схемы от внешних воздействий.

Выводы

В курсовой работе произведена разработка логического элемента по упрощенной заданной функции. Упрощение было произведено с помощью карт Карно, упрощенная функция приведена к базису И-, ИЛИ-НЕ и имеет вид :

![]()

Далее, в соотвествии с упрощением, была составлена электрическая схема, включающая заданную нелинейную нагрузку- общую для группы переключающих транзисторов. Затем произвели аналитический расчет параметров транзисторов схемы и определили геометрические размеры их затворов.

Геометрические размеры транзисторов Т2, Т3, Т4:

L = 6 (мкм).

W = 19 (мкм).

Геометрические размеры для нагрузочного транзистора Тн:

W = 6 (мкм),

L = 21(мкм).

Электрическая схема, описанная в PSPICE, обсчитывалась для определения статических и динамических параметров схемы.

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Логический уровень “1” получился отличным от заданного на 1,86%, а логический уровень “0” получился отличным от заданного на 8,3%.

По полученным геометрическим размерам построена топология логического элемента и вкратце рассказаны основные этапы технологического маршрута изготовления МДП-транзистора с совмещенным поликремниевым затвором, что является главной особенностью данной технологии. Вообще технологический маршрут с Si*- затвором включаетчетыре фотолитографии :

Формирование локальных охранных областей.

Формирование Si*-ого затвора.

Формирование контактных окон.

Металлизация.

В моем случае получился логический элемент с длинной 147 мкм,

шириной 106,2 мкм и общей площадью 15611,4 мкм2. Топология разработана по методу -проектирования с учетом всех заданных топологических ограничений и допусков.