- •Интерфейс eisa.

- •5.2.2 Структура пэвм типа “386/eisa”

- •Сигналы (линии) eisa.

- •Линии заявок и подтверждений пдп.

- •Линии запроса прерывания.

- •Линии управления.

- •Линии разрядности ведомой платы.

- •Сигналы поддерживающие режим блочного обмена.

- •Арбитраж, прерывания и прямой доступ eisa.

- •4.2.3. Временные характеристики.

- •4.2.3.1. Циклы шины.

- •4.2.3.2. Временные диаграммы базовых циклов шины.

4.2.3.1. Циклы шины.

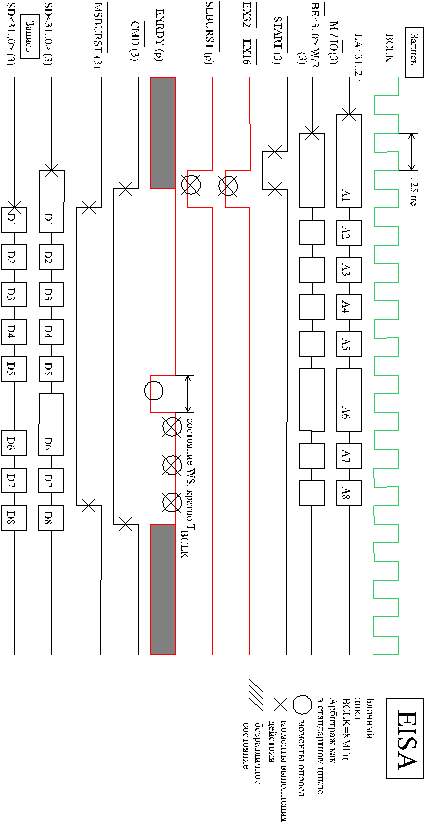

EISA - синхронная шина, моменты изменения сигналов в которой четко соотносятся с определенными фронтами BCLK - синхросигнала шины. Сигнал BCLK образуется из процессорного синхросигнала и имеет частоту в диапазоне от 6 до 8.33 Мгц. Для наиболее быстрых моделей PC/EISA с частотой процессора 33 Мгц - частота BCLK 8.25 Мгц получается делением на четыре, а для моделей с 25 Мгц - делением на три , т.е. 8.33 Мгц (максимально возможная для EISA-шины).

В дополнение к 8- и 16- разрядным циклам ISA-шины (см. раздел 4.1.3) в EISA-шине вводится три типа 32-разрядных циклов - стандартный, сжатый и блочный.

Стандартный цикл требует двух тактов шины. Ускорение передачи с 8 до 16.6 Мбайт/сек происходит за счет удвоения разрядности шины данных и незначительного повышения частоты.

Сжатый цикл требует

1.5 такта шины. Скорость передачи

увеличивается на 50 %. Для организации

сжатого цикла в EISA-шину вводится

специальный стробирующий сигнал

![]() ,

дополняющий число фронтов срабатывания

синхросигнала BCLK.

,

дополняющий число фронтов срабатывания

синхросигнала BCLK.

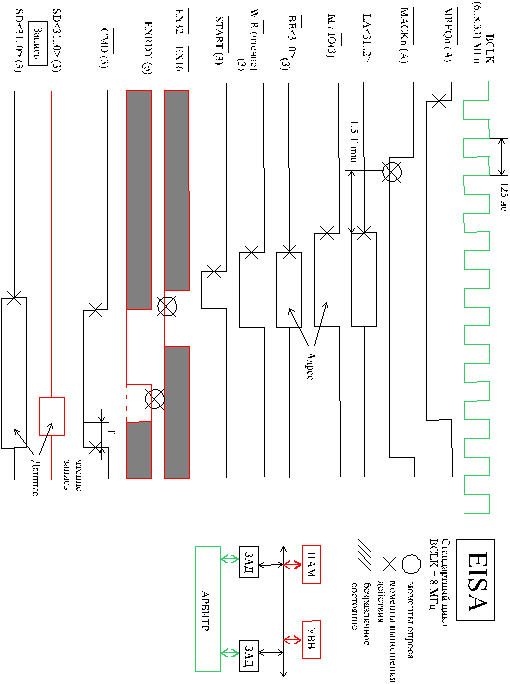

Длительность блочного цикла - один такт шины, что обеспечивает максимально возможную скорость передачи 33 Мбайт/сек.

Стандартный и блочные циклы доступны для использования любым задатчиком шины; сжатый цикл доступен только для центрального процессора.

В EISA-шине, как и в AT-шине, поддерживается семь каналов DMA, но скорость DMA-передач существенно выше. Контроллер DMA поддерживает четыре типа циклов 8-, 16- и 32-разрядных передач:

ISA-цикл, 1 передача за 8 тактов шины;

тип А, 1 передача за 6 такта шины;

тип В, 1 передача за 4 такта шины;

тип С, 1 передача за 1 такт шины;

4.2.3.2. Временные диаграммы базовых циклов шины.

В настоящем разделе рассмотрены достаточно общие временные диаграммы одиночного и блочного циклов шины (причины такого подхода указаны в разделе 4.2.3). Они представляют собой наглядную форму представления сведений по сигналам EISA-шины с указанием их причинно-следственных связей.

На рис. 4.12 представлена временная диаграмма стандартного согласованного цикла передачи задатчика EISA-шины [4.3], уточненная и дополненная с учетом специфики БИС i82355. Последовательность событий соответствует номерам на рисунке.

Устройство - потенциальный задатчик “n” запрашивает доступ к EISA-шине для самостоятельного обмена с исполнителем - выдает уровень сигнала

на падающем фронте сигнала BCLK.

на падающем фронте сигнала BCLK.На следующем падающем фронте BCLK устройство “n” анализирует состояние входного контакта

.

Источником сигналов

.

Источником сигналов является центральный арбитр на СП,

который производит арбитраж сигналов

является центральный арбитр на СП,

который производит арбитраж сигналов ,

воспринимаемых на восходящем фронте

BCLK. При отсутствии сигналов анализ

повторяется на каждом следующем

падающем фронте.

,

воспринимаемых на восходящем фронте

BCLK. При отсутствии сигналов анализ

повторяется на каждом следующем

падающем фронте.

Запрашивающее устройство “n” воспринимает сигнал разрешения на использование EISA-шины - низкий уровень контакта

- и становится задатчиком шины.

- и становится задатчиком шины.

Центральный арбитр разрешает устройству “n” доступ к шине низким уровнем соответствующего сигнала

.

При отсутствии запросов со стороны

других устройств системы (контроллера

регенерации динамической памяти,

контроллера DMA) минимальное время

реакции на поступивший запрос - 10 нс

(установка низкого уровня сигнала

.

При отсутствии запросов со стороны

других устройств системы (контроллера

регенерации динамической памяти,

контроллера DMA) минимальное время

реакции на поступивший запрос - 10 нс

(установка низкого уровня сигнала ).

Это соответствует минимально возможному

времени доступа к EISA-шине, равному

одному периоду BCLK (интервал между

событиями 1 и 2).

).

Это соответствует минимально возможному

времени доступа к EISA-шине, равному

одному периоду BCLK (интервал между

событиями 1 и 2).Минимум через 1.5 периода BCLK на его восходящем фронте задатчик помещает на шину адрес и указывает тип исполнителя: оперативная память или устройство в/в.

На следующем падающем фронте BCLK задатчик указывает тип операции (состоянием линии

)

и байты 32-разрядной шины данных, которые

будут использоватся в цикле обмена

(сигналами

)

и байты 32-разрядной шины данных, которые

будут использоватся в цикле обмена

(сигналами ...

... ).

).На восходящем фронте BCLK задатчик инициирует цикл обмена (низким уровнем сигнала

),

при операции “Запись” (WRITE) - устанавливает

значение на шине данных.

),

при операции “Запись” (WRITE) - устанавливает

значение на шине данных.По истечении одного периода BCLK задатчик:

сбрасывает сигнал

;

;устанавливает сигнал

;

;определяет разрядность исполнителя.

Задатчик проверяет готовность исполнителя завершить цикл обмена на первом падающем фронте BCLK после установки сигнала

(8). Отсутствие готовности исполнителя

- низкий уровень сигнала EXRDY - вынуждает

задатчика отрабатывать состояния

ожидание, длительность которых равна

периоду BCLK (8’ и 8’’), вплоть до прихода

высокого уровня EXRDY (8’’’). На рис. 4.12

показан цикл обмена с тремя дополнительными

состояниями ожидания.

(8). Отсутствие готовности исполнителя

- низкий уровень сигнала EXRDY - вынуждает

задатчика отрабатывать состояния

ожидание, длительность которых равна

периоду BCLK (8’ и 8’’), вплоть до прихода

высокого уровня EXRDY (8’’’). На рис. 4.12

показан цикл обмена с тремя дополнительными

состояниями ожидания.При операции “Чтение” (READ) на первом восходящем фронте BCLK после прихода сигнала готовности исполнителя EXRDY производится прием данных.

Сигнал

сбрасывается задатчиком: при операции

WRITE - на первом восходящем фронте BCLK

после приема высокого уровня сигнала

EXRDY, при операции READ - на втором восходящем

фронте.

сбрасывается задатчиком: при операции

WRITE - на первом восходящем фронте BCLK

после приема высокого уровня сигнала

EXRDY, при операции READ - на втором восходящем

фронте.Задатчик сбрасывает сигнал

на падающем фронте BCLK после сброса

сигнала

на падающем фронте BCLK после сброса

сигнала .

.Центральный арбитр, восприняв сброс сигнала

,

сбрасывает сигнал

,

сбрасывает сигнал .

.

Максимальная скорость передачи на EISA-шине может быть достигнута при использовании блочного режима, временная диаграмма которого, представляющая собой уточненную диаграмму из [4.3] с учетом специфики БИС i82355, приведена на рис.4.13.

В блочном цикле

к набору сигналов, используему в

стандартном цикле, добавляется еще

два: задатчик управляет линией

![]() и анализирует линию

и анализирует линию![]() .

.

Последовательность

событий в блочном цикле (соответствующая

номерам на рис.4.13) совпадает со стандартным

циклом до момента сброса задатчиком

сигнала

![]() ,

а далее выглядит так:

,

а далее выглядит так:

Одновременно со

сбросом сигнала

![]() и

установкой сигнала

и

установкой сигнала![]() задатчик анализирует состояние линий

задатчик анализирует состояние линий![]() ,

,![]() (как и в стандартном цикле) и

(как и в стандартном цикле) и![]() .

Низкий уровень на последней говорит о

способности исполнителя поддерживать

режим блочной передачи.

.

Низкий уровень на последней говорит о

способности исполнителя поддерживать

режим блочной передачи.

На первом после

установки сигнала

![]() падающем фронте BCLK задатчик анализирует

состояние линий EXRDY (как и в стандартном

цикле) и устанавливает сигнал

падающем фронте BCLK задатчик анализирует

состояние линий EXRDY (как и в стандартном

цикле) и устанавливает сигнал![]() ,

указывая исполнителю о работе в блочном

режиме. Данные от задатчикоа достоверны

на шине перед сбросом

,

указывая исполнителю о работе в блочном

режиме. Данные от задатчикоа достоверны

на шине перед сбросом![]() ,

а прием данных от исполнителя (при

операции “Чтение”) осуществляется на

первом восходящем .....

,

а прием данных от исполнителя (при

операции “Чтение”) осуществляется на

первом восходящем .....