- •Интерфейс eisa.

- •5.2.2 Структура пэвм типа “386/eisa”

- •Сигналы (линии) eisa.

- •Линии заявок и подтверждений пдп.

- •Линии запроса прерывания.

- •Линии управления.

- •Линии разрядности ведомой платы.

- •Сигналы поддерживающие режим блочного обмена.

- •Арбитраж, прерывания и прямой доступ eisa.

- •4.2.3. Временные характеристики.

- •4.2.3.1. Циклы шины.

- •4.2.3.2. Временные диаграммы базовых циклов шины.

Сигналы поддерживающие режим блочного обмена.

Т.е. ведущая и ведомая плата работают в режиме максимальной производительности 33 Мбайта/сек.

![]() - Master BURST (задатчик

поддерживает блочный режим).

- Master BURST (задатчик

поддерживает блочный режим).

![]() - Slave BURST (Исполнитель

поддерживает блочный режим).

- Slave BURST (Исполнитель

поддерживает блочный режим).

![]() .

Сигнал сообщает задатчику о том, что

исполнитель поддерживает режим блочной

передачи.

.

Сигнал сообщает задатчику о том, что

исполнитель поддерживает режим блочной

передачи.

![]() .

Низкий уровень сигнала сообщает

адресуемому исполнителю (модулю памяти),

что он будет работать в режиме блочной

передачи. После выдачи сигнала

.

Низкий уровень сигнала сообщает

адресуемому исполнителю (модулю памяти),

что он будет работать в режиме блочной

передачи. После выдачи сигнала

![]() задатчик проверяет наличие сигнала

задатчик проверяет наличие сигнала![]() от исполнителя на восходящем BCLK. Если

от исполнителя на восходящем BCLK. Если![]() активен, то задатчик устанавливает

активный

активен, то задатчик устанавливает

активный![]() на следующем падающем фронте BCLK и

начинает функционировать в блочном

режиме (передача - один период BCLK); в

противном случае -

на следующем падающем фронте BCLK и

начинает функционировать в блочном

режиме (передача - один период BCLK); в

противном случае -![]() не устанавливает и работает в одиночном

режиме (передача - два периода BCLK).

не устанавливает и работает в одиночном

режиме (передача - два периода BCLK).

Арбитраж, прерывания и прямой доступ eisa.

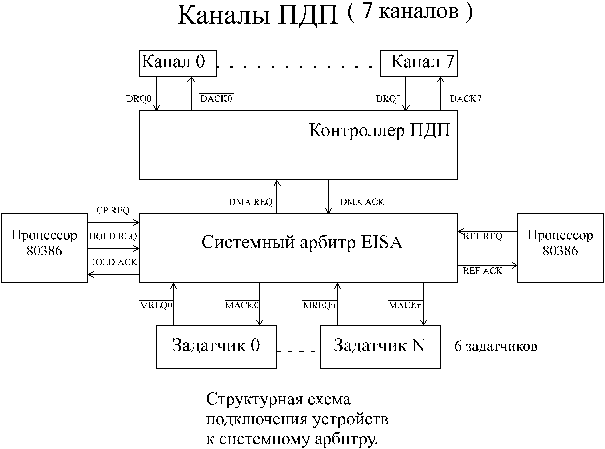

EISA-шина имеет централизованную структуру с единым центральным арбитром (ЦА) для всех типов задающих устройств: ЦП, контроллера регенерации, DMA-устройств и устройств-задатчиков. ЦА располагается на СП и соединен индивидуальными линиями для запрос-ответного режима взаимодействия со всеми задающими устройствами (с DMA-устройствами - через DMA-контроллер).

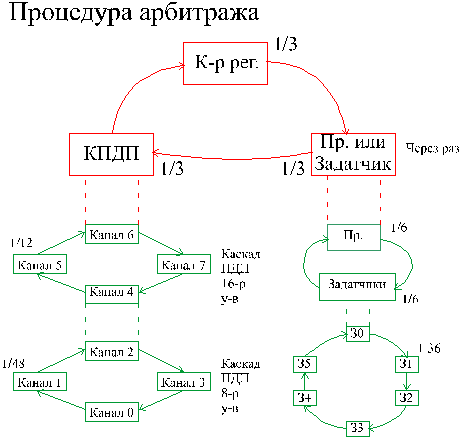

В EISA-шине реализованна процедура арбитража, элементы которой показаны на рисунке. В управлении шиной переодически учавствуют три класса устройств: рефреш-контроллер, DMA-контроллер и комбинация “ЦП - любой задатчик шины”. Наибольший приоритет присвоен рефреш-контроллеру, который может участвовать в каждом арбитражном цикле. Следующий приоритетный уровень имеют DMA-передачи; один из активных DMA-каналов может получать доступ к шине каждый цикл.

Между DMA-каналами реализован равнодоступный, круговой арбитраж - как в пределах одного каскада, так и между каскадами. Частота обслуживания каналов 5-7 в четыре раза выше, чем для каналов 0-3: за цикл обслуживания каналов 5-7 обслуживается один из каналов 0-3. Это препятствует монополизации шины одним каналом и гарантирует обслуживание по любому каналу.

Это справедливо и для подсистемы “ЦП - задатчик”. В ее рамках в каждый момент времени в арбитражном цикле участвует либо ЦП, либо задающее устройство, которое не было задатчиком в предыдущем цикле обмена. Таким образом, половину времени работы этой подсистемы обслуживается ЦП, а другую половину - все задатчики, каждый из которых использует 1/6 часть от этой половины.

Механизм прерываний в EISA в основном совпадает с соответствующим механизмом линии ISA.

В XT/AT-шинах используется фронтовой тип запуска процедуры прерывания. При этом затруднено совместное использование одной линии (одного приоритетного уровня) несколькими устройствами. Шина обладает низкой защищенностью от помех по линии IRQx.

4.2.3. Временные характеристики.

Полнота сведений по временным характеристикам EISA-шины, представленных в настоящем разделе, существенно уступает аналогичным данным по AT-шине. Стандарт на EISA-шину, формально существующий с 1988 года, был недоступен до начала 1990 года - времени апробирования первых БИС поддержки протокола EISA-шины фирмы Intel (серия 82350), характеристики которых, вероятно, легли в основу окончательной спецификации EISA-шины. Первые машины типа 386/EISA появились за рубежом лишь в 1-2 кварталах 1990 года. Для авторов стандарт на EISA-шину недоступен до настоящего времени. Приводимые здесь сведения о EISA-шине являются результатом обобщения журнальной информации.