- •Интерфейс eisa.

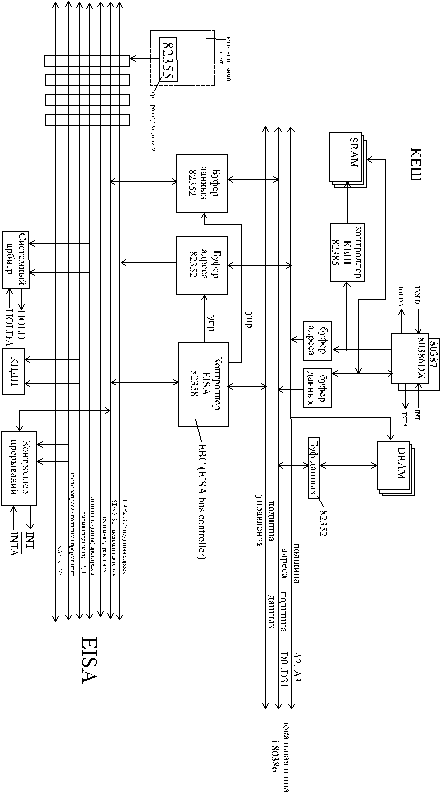

- •5.2.2 Структура пэвм типа “386/eisa”

- •Сигналы (линии) eisa.

- •Линии заявок и подтверждений пдп.

- •Линии запроса прерывания.

- •Линии управления.

- •Линии разрядности ведомой платы.

- •Сигналы поддерживающие режим блочного обмена.

- •Арбитраж, прерывания и прямой доступ eisa.

- •4.2.3. Временные характеристики.

- •4.2.3.1. Циклы шины.

- •4.2.3.2. Временные диаграммы базовых циклов шины.

Интерфейс eisa.

(Extended Industrial Standart Architecture)

1988г, консорциум изготовителей компьютеров.

4.2 Архитектура шины EISA.

4.2.1 Назначение и основные сведения.

Системная шина EISA - 32 разрядная расширенная версия ISA - шины - представляет собой следующий этап в развитии совместимых снизу-вверх системных шин:

XT-bus --> AT-bus (ISA - bus) --> EISA - bus

Основное назначение EISA - шины - способствовать реализации потенциальных возможностей микросхемы i80386.

Переход от XT - к AT - шине был революционным этапом и дал, в основном, рост количественных показателей - числа разрядов адреса и данных, количества уровней прерывания и каналов DMA. Качественно машины типа PC AT мало отличались от PC XT.

Переход к EISA - шине - принципиально новый шаг в развитии системных интерфейсов ПЭВМ. Кроме роста количественных показателей (32 - разрядные передачи, 32 адресных разряда, дающие возможность прямой адресации ОП до 4 Гб), он принес в ПЭВМ ряд новых качеств, являющихся традиционными атрибутами системных шин мини-ЭВМ. EISA - шина обеспечивает:

эффективную поддержку многозадачного режима микропроцессора

средств децентрализованного обмена между интелектуальными устройствами и подсистемами.

Основные характеристики EISA - шины (в дополнение к характеристикам ее неотъемлимой части - AT - шины, см. раздел 4.1.1):

Программная, аппаратная и конструктивная совместимость с 8- и 16 - разрядными XT/AT платами расширения. В каждом цикле обмена - идентификация вида исполнительного устройства и автоматическая настройка на соответствующий тип обмена. Реализация резервов производительности стандартных XT/AT - плат за счет введения новых типов передачи.

Для всех активных устройств EISA - шины (ЦП, контроллера DMA, задатчиков) - поддержка 8-, 16- и 32-разрядных передач в 32-разрядном адресном пространстве.

Автоматическое согласование (выравнивание) формата данных взаимодействующих устройств - преобразование одного 32-разрядного цикла обмена в два 16-разрядных (для плат ISA/EISA-16) или в четыре 8-разрядных цикла (для плат ISA/EISA-8).

Дополнение магистральных линий связи индивидуальными для каждого разъема расширения (разъемно-специфицированную линии связи). Это обеспечивает для EISA-плат географическую адресацию и режим автоконфигурации при включении питания ПЭВМ и устраняет необходимость использования переключателей и перемычек для настройки на требуемый адрес, уровень прерывания, канал DMA и уровень задатчика.

В подсистеме прерывания - возможность выбора одного из двух видов запуска процедуры: фронтом или уровнем. Во втором случае на один приоритетный уровень может быть подключено несколько устройств.

Подсистема DMA.

- в дополнение к стандартному циклу DMA-обмена вводятся три дополнительных (типы А, В, С), каждый с возможностью 8-, 16- и 32-разрядных передач. Скорость DMA-передач до 33 Мбайт/сек.

- алгоритм арбитража - равнодоступный, круговой как в пределах одного контроллера DMA (каскада), так и между каскадами; частота обслуживания каналов 5-7 в четыре раза выше, чем для каналов 0-3; за круг обслуживания каналов 5-7 обслуживается один из каналов 0-3; препятствует монополизации шины одним каналом и гарантирует обслуживание по любому приоритетному каналу DMA в течении определенного времени.

Подсистема задатчиков.

Архитектура EISA-шины не предусматривает самостоятельной подсистемы задатчиков. Задающее устройство может получать управление шиной искусственно, с помощью контроллера DMA, если специально запрограммирован один из его каналов.

В архитектуру EISA-шины введена подсистема задатчиков, имеющая следующие характеристики:

- число уровней приоритета задатчиков на разъемах расширения - шесть; центральному процессору присваивается независимый уникальный уровень приоритета;

- арбитраж запросов на доступ к EISA-шине выполняется централизованным контроллером задатчиков на СП, с помощью однонаправленных магистральных линий запроса и ответа;

- уровни задатчиков - фиксированные, задабтся при сботке системы; к каждому уровню можно подключить только одно устройство;

- алгоритм обработки запросов - равнодоступный, круговой; в моменты предоставления шины задающим устройствам шиной управляют поочередно ЦП и один из группы задатчиков, в пределах которой реализуется круговой приоритет; это гарантирует центральному процессору доступ к EISA-шине после окончания текущего сеанса обмена с задатчиком;

- протокол обмена в фазе арбитража - синхронный, запрос - ответ;

- арбитраж задающих устройств выполняется одновременно с обменом данных по шине;

- поддерживаются блосные передачи, максимальная длительность которых ограничена величиной тайм-аута, с возможностью прекращения блочной передачи при наличии запросов на доступ к шине со стороны других задатчиков.

В шине EISA предусмотрена программная настройка каждого приоритетного уровня либо на режим фронтового запуска (с целью совместимости с используемыми XT/AT-платами), либо на режим уровневого запуска. В последнем случае помехозащищенность повышается и к одному приоритетному уровню допускается подключение нескольких устройств (архитектурно не ограничено).