4 Разработка операционного автомата процессора

При построении операционного автомата процессора как автомата выполнения команд необходимо представить полученный выше алгоритм командного цикла (рисунок 2 - 9) в виде последовательности микроопераций МПА ведущего УУ процессора (рисунок 11). Обозначим множество входных сигналов (логических условий) МПА ведущего УУ через X= {xl,x2,...,xl}, а множество его выходных (управляющих) сигналов - черезY={yl,y2,...,ym}. Выходные сигналыYУУ процессора управляют коммуникациями (передачей) операндов, адресов, флагов и т.п.) между регистрами и блоками процессора, создавая тем самым необходимые предпосылки для выполнения команд. Его входными сигналамиXявляются флаги, хранящиеся в регистре флагов, и унитарные коды, являющиеся результатами дешифрирования управляющих полей команды, хранящиеся в регистре команд.

Совокупность недетализованных основных блоков процессора (за (исключением УУ процессора), детально проработанных регистров и счетчиков, а также коммуникаций между ними является операционным автоматом процессора (иногда называемым устройством или автоматом выполнения команд). Входными сигналами операционного автомата процессора являются выходные сигналы Yведущего УУ процессора (УУ верхнего уровня), а выходными сигналами - входные сигналыXведущего УУ процессора. В связи с этим оба автомата процессора - и операционный, и управляющий - могут быть разработаны на основании одного и того же алгоритма командного цикла, так как он реализуется в результате их взаимодействия

В качестве закона функционирования управляющего автомата выберем закон функционирования автомата Мили. Множество состояний автомата обозначим через S={sl,s2,...sn}. Список соответствующих микроопераций для варианта 1 представлен в таблице 3.

Таблица 3 – Списки микроопераций и логических условий

|

Выходные сигналы УУ |

Микрооперация |

|

y0 |

WF:=0 |

|

y1 |

ZF:=0 |

|

y2 |

IF:=0 |

|

y3 |

SF:=O |

|

y4 |

OF:=0 |

|

y5 |

PC[8:0]:=0 |

|

y6 |

iR:=0 |

|

y7 |

ША[8:0]:=РС[8:0] |

|

y8 |

ШД[15:0]:=ОЗУ[ША[8:0]] |

|

y9 |

RgI[iR*16+15: iR*16] :=ШД[15:0] |

|

y10 |

iR:=iR+l |

|

y11 |

PC[8:0]:=PC[8:0]+1 |

|

y12 |

ША[2:0]:=Rgl[9:7] |

|

y13 |

ШД[15:0]:=Rg[ША[2:0]] |

|

y14 |

RgBuf[8:0]:=ШД[8:0] |

|

y15 |

ШA[8:0]:=RgBuf[8:0] |

|

y16 |

ШД[iR*16+15:iR*16]:=O3У[ШA[8:0]] |

|

y17 |

ША[8:0]:=ША[8:0]+1 |

|

y19 |

ША[8:0]:=RgI[16:7] |

|

y21 |

RgA1:= ШД[7:0];RgA2:= ШД[15:8]; |

|

y22 |

RgС2:=ШД[15:0];RgС1:=ШД[31:16] |

|

y23 |

A:=RgA-RgB |

|

y24 |

A:=RgA+RgB |

|

y25 |

A:=RgA*RgB |

|

y26 |

A:=RgA/RgB |

|

y27 |

A:=RgAVRgB |

|

y28 |

A:=RgAΛRgB |

|

y29 |

A:=RgA○RgB |

|

y30 |

PС[8:0]:=ШУ[25:16] |

|

y31 |

SP[8:0]:=SP[8:0]-l |

|

y32 |

ШA[8:0]:=SP[8:0] |

|

y33 |

ШД[8:0]:=РС[8:0] |

|

y34 |

ОЗУ[ША[8:0]]:=ШД[15:0] |

|

y35 |

PC[8:0]:=ШД[8:0] |

|

y36 |

SP[8:0]:=SP[8:0]+l |

|

y37 |

ШД[7:0]:=А1; ШД[15:8]:=А2; |

|

у38 |

Rg[ШA[2:0]]:=ШД[15:0] |

|

у39 |

ШД[15:0]:=RgI[31:16] |

|

у40 |

O3У[ШA[8:0]]:=ШД[iR*16+15:iR*16] |

|

у41 |

ШД[7:0]:=С1; ШД[15:8]:=С2 |

|

у42 |

А1:=ШД[7:0]; А2:=ШД[15:8]; |

|

у43 |

SP[8:0]:=SP[8:0]-2 |

|

у44 |

SP[8:0]:=SP[8:0]+2 |

|

у45 |

RgС2:=ШД[7:0];RgС1:=ШД[15:8] |

|

у46 |

RgED[15:0]:=ШД[15:0] |

|

у47 |

ШД[15:0]:=RgED[15:0] |

|

у48 |

IF:=1 |

|

у49 |

RgF[4:0]:=ШД[4:0] |

|

у50 |

В[8:0]:=ШД[8:0] |

|

y51 |

SP[8:0]:=ШД[8:0] |

|

y52 |

ШA[8:0]:=RgZ[8:0] |

|

у53 |

ШД[4:0]:=RgF[4:0] |

|

Входные сигналы УУ |

Логическое условие |

|

х0 |

WF=1 |

|

xl |

iR=2 |

|

х2 |

КОп = "сложение" |

|

хЗ |

КOп = "вычитание" |

|

х4 |

КОп = "умножение" |

|

х5 |

КОп = "деление" |

|

Х6 |

КОп = "дизъюнкция" |

|

х7 |

КОп = "конъюнкция" |

|

х8 |

КОп = "сумма по модулю 2" |

|

х9 |

КОп = "УП>0" |

|

х10 |

КОп = "УП<0" |

|

x11 |

КОп = "УП=0" |

|

х12 |

КОп = "УП по переполнению" |

|

х13 |

КОп = "безусловный переход" |

|

х14 |

КОп = "вызов подпрограммы" |

|

х15 |

КОп = "возврат из подпрограммы" |

|

х16 |

КОп = "запись в ЗУ" |

|

Выходные сигналы УУ |

Логическое условие |

|

х17 |

КОп = "чтение из ЗУ" |

|

х18 |

КОп = "запись в стек" |

|

х19 |

КОп = "чтение из стека" |

|

х20 |

КОп = "сложение со стеком" |

|

х21 |

КОп = "вычитание из стека" |

|

х22 |

КОп = "запись в ВУ" |

|

х23 |

КОп = "чтение из ВУ" |

|

х24 |

КОп = "запрещение прерывания" |

|

х25 |

КОп = "разрешение прерывания" |

|

х26 |

КОп = "останов" |

|

х27 |

КОп = "выход из прерывания" |

|

х28 |

КОп = "загрузка регистра базы" |

|

х29 |

КОп = "загрузка указателя стека" |

|

х30 |

ФК = "SI" |

|

х31 |

ТА = "П" |

|

х33 |

iR = 2 |

|

х34 |

SF=0 &ZF=0 |

|

х35 |

SF=1 |

|

х36 |

ZF=1 |

|

х37 |

OF=1 |

|

х38 |

IF=1 |

|

х39 |

RgZ[8:0]=0 |

|

х40 |

арифметико-логическая операция |

|

х41 |

сложение или вычитание со стеком |

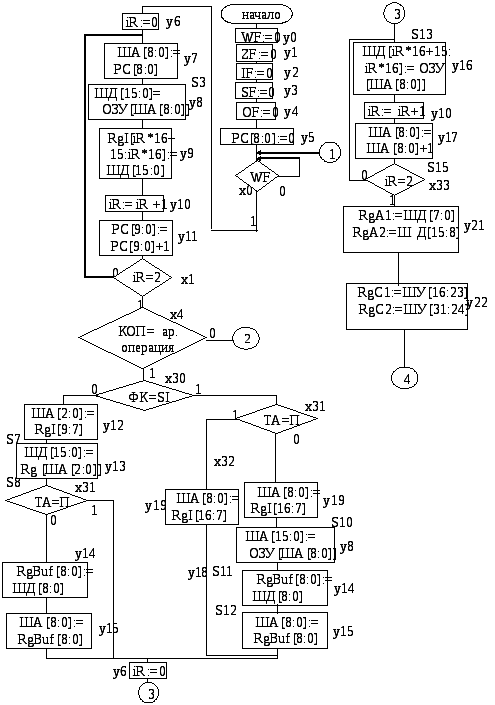

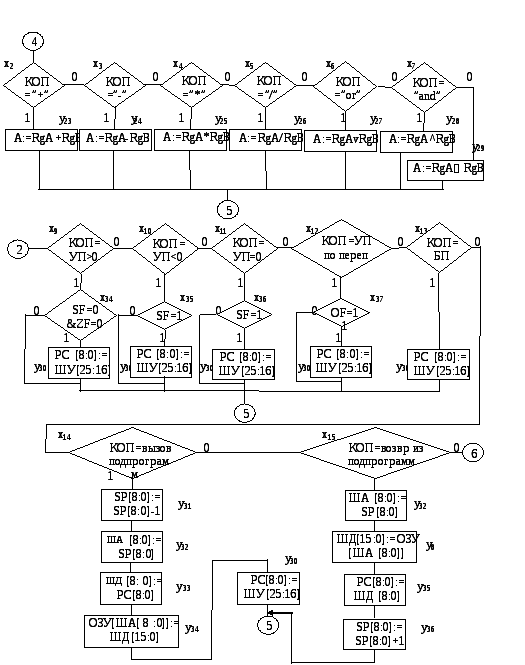

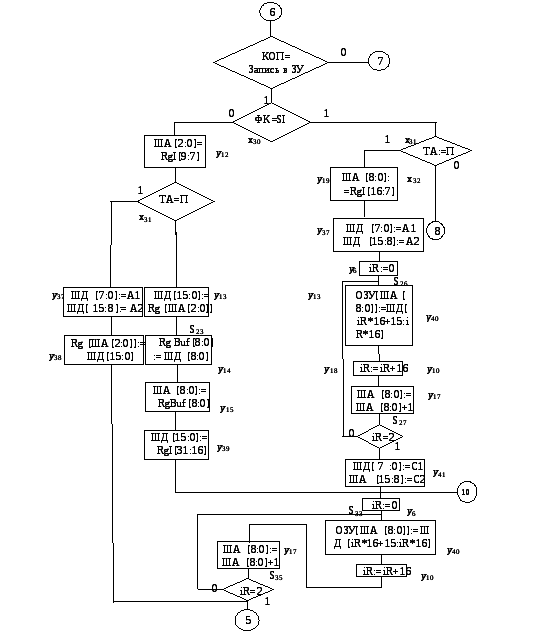

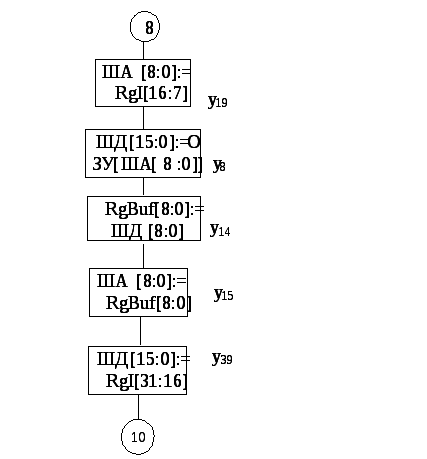

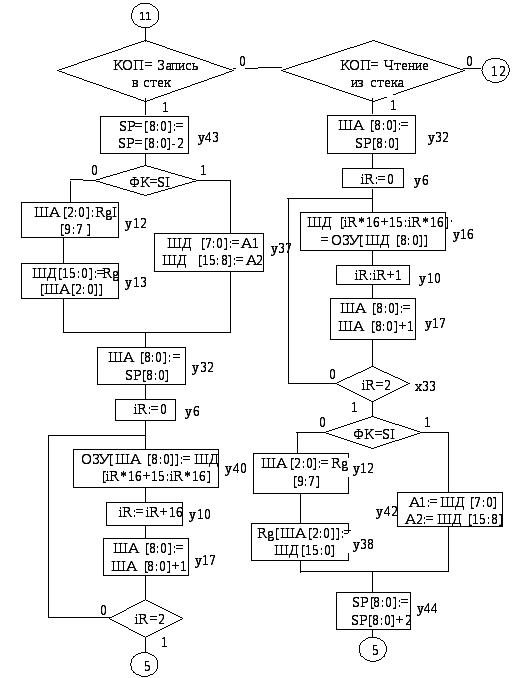

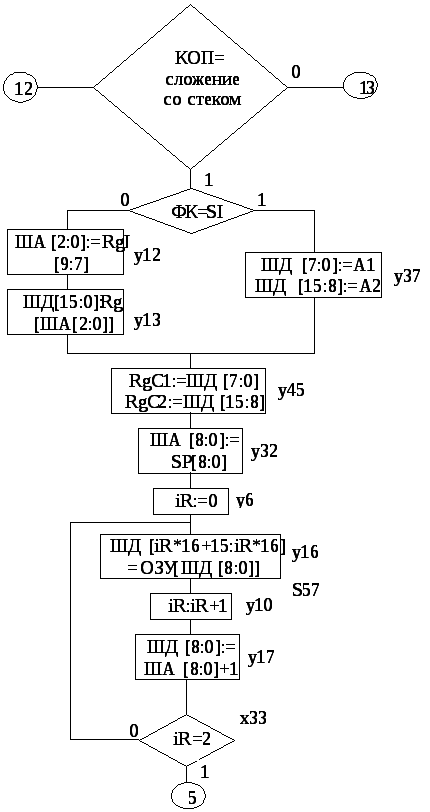

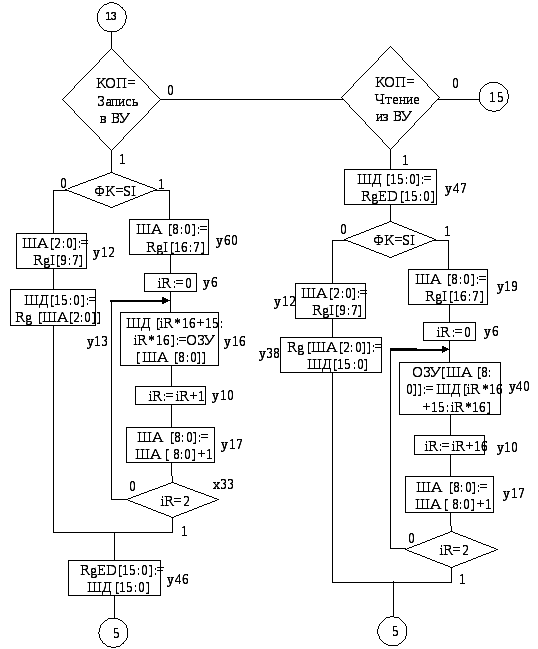

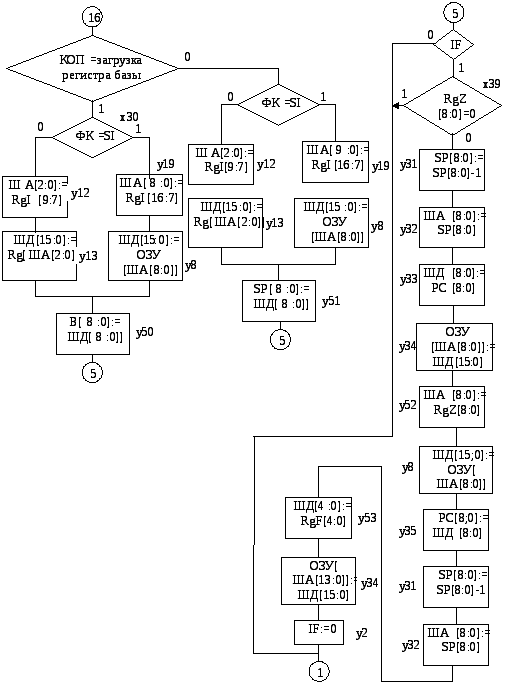

На основе алгоритма командного цикла, списков микроопераций и логических условий составляем обобщенный алгоритм командного цикла с размеченными состояниями как алгоритм МПА ведущего УУ процессора, синтезируемого в виде автомата Мили.

Рисунок 3.10. Размеченный обобщенный алгоритм командного цикла

Рисунок

3.10. Продолжение

Рисунок

3.10. Продолжение

Рисунок

3.10. Продолжение

Рисунок

3.10. Продолжение

Рисунок 3.10. Продолжение

Рисунок 3.10. Продолжение

Рисунок 3.10. Продолжение

Рисунок 3.10. Продолжение

Рисунок 3.10. Продолжение

Рисунок 3.10. Продолжение

Рисунок 3.10. Окончание