- •Федеральное агентство по образованию

- •1. Программируемые логические интегральные схемы

- •1.1 Принципы обработки цифровых данных.

- •1.2 Способы реализации логических функций.

- •1.3 Принципы построения и элементы программируемых логических интегральных схем.

- •1.4 Периферийное сканирование цифровых устройств.

- •2. Периферийные узлы цифровых устройств

- •3. Системы отбражения цифровой информации.

- •3.1 Способы управления одиночными светодиодными индикаторами.

- •3.2 Системы отображения многоразрядных цифровых данных.

- •3.3 Жидкокристаллические индикаторы и способы управления ими.

- •4. Цифроаналоговые и аналого-цифровые преобразователи

- •4.1 Цифроаналоговые преобразователи.

- •4.1.1 Основные параметры и характеристики.

- •4.1.2.Принципы построения цап прямого преобразования.

- •4.1.3 Умножающие цап.

- •4.1.4 Цап с косвенным преобразованием.

- •4.1.5 Области применения цап.

- •4.2 Аналого-цифровые преобразователи.

- •4.2.1 Основные параметры и характеристики.

- •4.2.2 Аналого-цифровые преобразователи с непосредственным преобразованием.

- •4.2.3 Ацп с косвенным преобразованием.

- •4.2.4 Области применения ацп.

- •Контрольные вопросы.

- •Лехин Сергей Никифорович

- •Часть 4.

1.3 Принципы построения и элементы программируемых логических интегральных схем.

Дальнейшее развитие программируемых интегральных схем проходило как по пути увеличения количества элементов на кристалле, так и реализации возможности многократного программирования. Современные ПЛИС условно разделяются на две основные группы: CPLD (Complex programmable logic devices) и FPGA (Field programmable gate array). Первые представляют собой сложную программируемую логическую матрицу, а вторые – матрицы вентилей, программируемую электрическим полем.

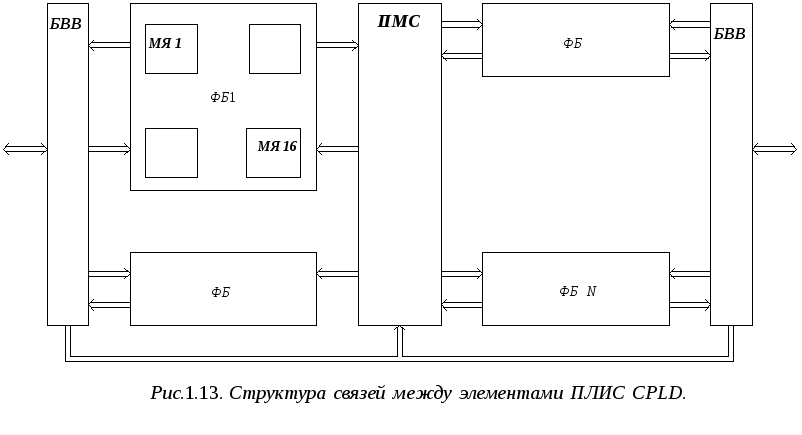

Основой CPLD являются макроячейки (МЯ), которые представляют собой многофункциональные устройства, способные настраиваться на выполнение различных логических операций над многоразрядными данными. В ряде вариантов ПЛИС они выполняются на основе ПМЛ и могут включать в свой состав узлы памяти. Такие ячейки с помощью программируемых линий связи организуются в функциональные блоки (ФБ), а взаимодействие между ними реализуется с помощью программируемой матрицы соединений - ПМС. Упрощенный вариант такой структуры представлен на рис.1.13. Для организации связи с внешними устройствами служат блоки ввода-вывода - БВВ.

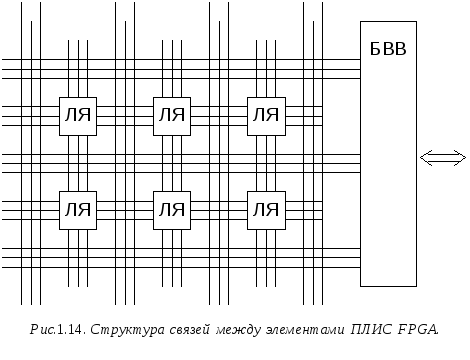

В

о

второй разновидности ПЛИС имеются

наборы элементов – логические ячейки

(ЛЯ), в качестве которых используются:

транзисторные пары, типовые логические

вентили, логические модули на основе

мультиплексоров и модули, содержащие

ПЗУ. Связи между ними могут устанавливаться

относительно произвольным образом.

Требуемая конфигурация логического

элемента реализуется пользователем, а

логические модули настраиваются на

выполнение конкретных относительно

несложных логических операций. Условное

изображение такой структуры представлено

на рис. 1.14.

о

второй разновидности ПЛИС имеются

наборы элементов – логические ячейки

(ЛЯ), в качестве которых используются:

транзисторные пары, типовые логические

вентили, логические модули на основе

мультиплексоров и модули, содержащие

ПЗУ. Связи между ними могут устанавливаться

относительно произвольным образом.

Требуемая конфигурация логического

элемента реализуется пользователем, а

логические модули настраиваются на

выполнение конкретных относительно

несложных логических операций. Условное

изображение такой структуры представлено

на рис. 1.14.

Для

физической реализации соединений между

узлами ПЛИС фирмами изготовителями

используется несколько подходов.

Выпускаются однократно программируемые

и перепрограммир уемые

устройства. В первом случае в качестве

токопроводящих связей могут использоваться

как полевые транзисторы ЛИЗМОП, так и

перемычки типаantifuse,

структура которых приведена на рис.

1.15.

уемые

устройства. В первом случае в качестве

токопроводящих связей могут использоваться

как полевые транзисторы ЛИЗМОП, так и

перемычки типаantifuse,

структура которых приведена на рис.

1.15.

В исходном состоянии между токопроводящими слоями из поликристаллического кремния и кремния с n-проводимостью располагается трехслойная область диэлектрика с чередованием слоев оксид-нитрид-оксид. Программирование осуществляется путем электрического пробоя слоев диэлектрика, в результате чего образуется проводящий канал (перемычка) из поликремния между соответствующими электродами. Устранить эту перемычку нельзя..

При использовании ЛИЗМОП транзисторов перемычка создается за счет перевода, полевого транзистора в проводящее состояние, что осуществляется путем подачи программирующего импульса. Вернуть Подействовав на такой транзистор ультрафиолетовым излучением его можно вернуть в исходное, непроводящее состояние. В однократно программируемых устройствах аналогичной структуры кристаллы защищают от попадания света и, программирование в этом случае возможно только один раз.

В настоящее время для создания многократно программируемых токопроводящих перемычек используются как двухзатворные полевые транзисторы МНОП типа, изготавливаемые по FLASH технологии, так и обычные. В первом случае установление и разрыв связей осуществляется путем подачи специальных программирующих импульсов на соответствующие электроды требуемых транзисторов. При этом они переходят в проводящее или непроводящее состояние. Такой подход позволяет многократно менять конфигурацию разрабатываемого устройства сохраняя ее при выключенном питании.

Во втором случае используется триггерная память конфигурации (SRAM-based). Здесь в качестве перемычки выступает обычный полевой транзистор, затвор которого подключается к триггеру. Высокий уровень сигнала на его выходе переводит транзистор в проводящее состояние, а низкий сохраняет запертое. Триггер устанавливается в требуемое состояние в ходе загрузки программы конфигурации и сохраняет его в течение времени, пока включено питание ПЛИС. Такое оперативное программирование может производиться неограниченное число раз. Однако, в этом случае при включении питания необходимо запускать процесс инициализации конфигурирования, на что требуется определенное время.

Для оценки сложности и возможностей элементов ПЛИС типа FPGA используются понятия зернистости и функциональности. Первое связано со структурой элементов, то есть с тем, насколько мелкими будут части, из которых собираются требуемые устройства. Второе понятие оценивает логические возможности элементов.

Примером наиболее мелкозернистого может служить элемент, состоящий из пары комплементарных МОП транзисторов (рис. 1.16). Такие элементы объединяются в цепочки, между которыми располагаются трассировочные каналы, позволяющие устанавливать требуемые связи между ними.

П ример

организации межсоединений транзисторовVT1

- VT4

для реализации логического элемента

2И-НЕ, принципиальная схема которого

приведена на рисунке 1.17 имеет вид (рис.

1.18). То обстоятельство, что МОП транзисторы

являются симметричными структурами

позволяет их электроды стока и истока

менять местами.

ример

организации межсоединений транзисторовVT1

- VT4

для реализации логического элемента

2И-НЕ, принципиальная схема которого

приведена на рисунке 1.17 имеет вид (рис.

1.18). То обстоятельство, что МОП транзисторы

являются симметричными структурами

позволяет их электроды стока и истока

менять местами.

Д ля

разделения создаваемых таким образом

логических элементов используются пары

транзисторов, к примеруVT5,VT6,

при этом затвор n

- канального соединятся с корпусом, а у

p

- канального с положительным полюсом

источника питания. Оба транзистора

оказываются запертыми и соответствующие

ячейки будут электрически разделены

между собой.

ля

разделения создаваемых таким образом

логических элементов используются пары

транзисторов, к примеруVT5,VT6,

при этом затвор n

- канального соединятся с корпусом, а у

p

- канального с положительным полюсом

источника питания. Оба транзистора

оказываются запертыми и соответствующие

ячейки будут электрически разделены

между собой.

П римером

более крупнозернистых ячеек служат

логические блоки, используемые в ряде

ПЛИС, состоящие из трех мультиплексоров

2→1 и элемента ИЛИ (рис. 1.19). Функция,

описывающая состояние выхода мультиплексора

имеет вид

римером

более крупнозернистых ячеек служат

логические блоки, используемые в ряде

ПЛИС, состоящие из трех мультиплексоров

2→1 и элемента ИЛИ (рис. 1.19). Функция,

описывающая состояние выхода мультиплексора

имеет вид![]() ,

а функция, воспроизводимая логическим

блоком может быть представлена как:

,

а функция, воспроизводимая логическим

блоком может быть представлена как:

![]() .

.

Подавая на входы такого блока переменные и константы можно реализовать все функции от трех, ряд от четырех и некоторые функции от большего числа переменных, всего 702 различных варианта.

О снову

крупнозернистых блоков составляют

табличные функциональные преобразователи,

представляющие собой ППЗУ, а также

программируемые мультиплексоры и

триггера.

снову

крупнозернистых блоков составляют

табличные функциональные преобразователи,

представляющие собой ППЗУ, а также

программируемые мультиплексоры и

триггера.

Системы межсоединений (коммутации) логических блоков ПЛИС типа FPGA имеют различные архитектурные и технологические решения. Для обеспечения максимальной коммутируемости при минимальных задержках и количестве ключей применяется иерархическая система связей, включающая в себя короткие и длинные проводящие сегменты.

В ариант

схемы коммутации одной из разновидностейFPGA

фирмы Actel

приведен на рис. 1.20. Здесь логические

блоки располагаются горизонтальными

рядами между которыми имеются

трассировочные каналы. Каждый канал

содержит четыре линии, которые могут

быть разбиты на сегменты различной

длины. Светлые кружки на пересечениях

линий связи означают возможность их

соединения в данной точке с помощью

программируемой перемычки.

ариант

схемы коммутации одной из разновидностейFPGA

фирмы Actel

приведен на рис. 1.20. Здесь логические

блоки располагаются горизонтальными

рядами между которыми имеются

трассировочные каналы. Каждый канал

содержит четыре линии, которые могут

быть разбиты на сегменты различной

длины. Светлые кружки на пересечениях

линий связи означают возможность их

соединения в данной точке с помощью

программируемой перемычки.

Зачерненными кружками показаны перемычки, которые должны быть установлены для связи точек a, b, c и d соответствующих логических блоков. Кроме этого в каналах имеются непрерывные по всей длине сегменты, один из которых заземлен, а другой связан с источником питания. Это позволяет подавать на входы любого из логических блоков сигналы логического нуля, либо единицы, настраивая их на выполнение соответствующих операций.

В

FPGA

фирмы Xilinx

(рис. 1.21) система связей имеет иной

характер и состоит из связей общего

назначения, длинных линий, прямых связей

и линий тактирования. Каждый логический

блок (ЛБ) окружен переключательными

блоками (ПБ) с помощью которых организуются

требуемые межсоединения. Связи логических

блоков с переключательными устанавливаются

путем создания токопроводящих перемычек

в точках пересечения соответствующих

линий.

FPGA

фирмы Xilinx

(рис. 1.21) система связей имеет иной

характер и состоит из связей общего

назначения, длинных линий, прямых связей

и линий тактирования. Каждый логический

блок (ЛБ) окружен переключательными

блоками (ПБ) с помощью которых организуются

требуемые межсоединения. Связи логических

блоков с переключательными устанавливаются

путем создания токопроводящих перемычек

в точках пересечения соответствующих

линий.

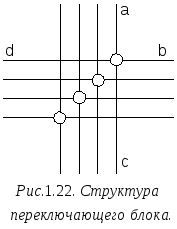

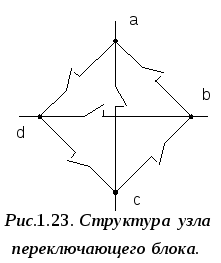

Структура переключающего блока имеет вид, представленный на рис. 1.22.. Кружками отмечены программируемые точки связи, каждая из которых представляет собой узел, содержащий шесть ключевых транзисторов (рис. 1.23). Он позволяет передавать сигналы в любых направлениях между несвязанными в исходном состоянии линиями.

Р еальная

структура связей в аналогичных ПЛИС

гораздо сложнее и между собой соединяются

не только соседние переключательные

блоки, но и расположенные через один,

два и т.п. Кроме этого имеются линии,

пересекающие вдоль и поперек весь

кристалл.

еальная

структура связей в аналогичных ПЛИС

гораздо сложнее и между собой соединяются

не только соседние переключательные

блоки, но и расположенные через один,

два и т.п. Кроме этого имеются линии,

пересекающие вдоль и поперек весь

кристалл.

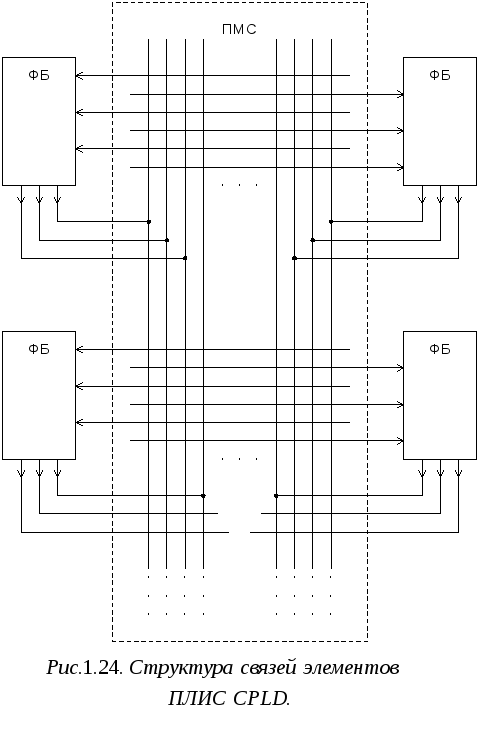

Как уже отмечалось, в ПЛИС типа CPLD макроячейки на первом этапе объединяются в функциональные блоки, которые связываются между собой посредством программируемой матрицы межсоединений ПМС. В отличие от сегментированных линий программируемая матрица соединений образует непрерывную систему идентичных связей.

У прощенная

схема коммутации функциональных блоков

может быть представлена на рис. 1.24. Входы

функциональных блоков соединяются с

горизонтальными, а выходы с вертикальными

линиями связи. При этом любой вход может

быть подключен к любому из выходов, что

обеспечивает полную коммутируемость

блоков.

прощенная

схема коммутации функциональных блоков

может быть представлена на рис. 1.24. Входы

функциональных блоков соединяются с

горизонтальными, а выходы с вертикальными

линиями связи. При этом любой вход может

быть подключен к любому из выходов, что

обеспечивает полную коммутируемость

блоков.

В настоящее время ПЛИС различных конфигураций выпускаются большим количеством фирм изготовителей, наиболее известными из которых являются Altera, Xilincx, Actel, Vantis и ряд других. Устройства разных фирм отличаются по внутренней структуре, методам организации связей между элементами и блоками, быстродействием и иными параметрами.

Фирма Altera выпускает и развивает несколько функциональных линий программируемой логики, в частности MAX, FLEX, APEX. ПЛИС типа МАХ относятся к группе CPLD и имеют блочную структуру, FLEX - к семейству FPGA, а APEX и Virtex фирмы Xilinx представляют собой новый класс программируемой логики, который называется системы на кристалле - SOC (System on chip).

Совершенствование полупроводниковой технологии, и в частности уменьшение размеров элементов позволяет на одном кристалле кремния разместить десятки миллионов элементов (миллионы эквивалентных вентилей), что в свою очередь дает возможность создавать целую систему – процессорную часть, память, интерфейсные схемы и т.д.

Используя свойство программируемости соединений и имея набор одинаковых вентилей, на основе стандартной ПЛИС можно создать практически любое цифровое устройство, реализующее требуемую функцию. Однако, следствием этого может быть неоптимальность конфигурации системы приводящая к снижению быстродействия, излишним затратам аппаратных средств и площади кристалла. В ряде случаев более эффективным является подход, при котором та или иная функция реализуется с помощью специализированного устройства, оптимизированного под ее выполнение.

В частности, аппаратный умножитель 8*8 можно построить на реконфигурируемых логических блоках ПЛИС, а можно спроектировать и реализовать как специализированное устройство. В последнем случае при тех же характеристиках он может быть размещен на площади в несколько раз меньшей.

Если в состав ПЛИС вводить определенные функционально законченные блоки, так называемые специализированные аппаратные ядра, то при реализации сложных систем это может привести к существенному выигрышу как по затратам ресурсов ПЛИС, так и по быстродействию из-за уменьшения числа межсоединений.

При таком подходе система конфигурируется из относительно крупных функционально законченных узлов. Однако при этом возникает вопрос об ассортименте и количестве ядер, так как для решения одних задач потребуются устройства, которых нет в составе ПЛИС, а для других - имеющиеся узлы не понадобятся. Данный вопрос окончательно не решен, но некоторые из разновидностей аппаратных ядер востребованы практически для всех цифровых систем обработки сигналов. Это, в частности, блоки памяти с изменяемой организацией, арифметико-логические устройства параллельные умножители, интерфейсные блоки и т.п.

Н а

основе ПЛИС разработан класс новых

устройств, которые называютсяFPIC

(Field

Programmable

Interconnect

Circuits).

Они содержат лишь набор программируемых

соединений и блоки ввода-вывода. Такие

устройства могут использоваться для

реализации соединений внешних компонентов,

представляющих собой как элементы

средней степени интеграции, так и ПЛИС.

а

основе ПЛИС разработан класс новых

устройств, которые называютсяFPIC

(Field

Programmable

Interconnect

Circuits).

Они содержат лишь набор программируемых

соединений и блоки ввода-вывода. Такие

устройства могут использоваться для

реализации соединений внешних компонентов,

представляющих собой как элементы

средней степени интеграции, так и ПЛИС.

Они выполняют роль печатной платы, конфигурацию соединительных проводников на которой можно программно изменять рис. 1.25). Это позволяет, используя единую конфигурацию печатной платы с фиксированным набором межсоединений между выводами устанавливаемых микросхем, реализовывать различные конфигурации устройств обработки цифровых сигналов.

Ввиду сложности и разнообразия структур схем программируемой логики, для их классификации и оценки возможностей обычно используют обобщенные параметры, к важнейшим из которых относятся: кратность программирования, уровень интеграции, быстродействие и структурная организация.

Выпускаются устройства с однократным, многократным с ограниченным количеством циклов программирования и многократным без такого ограничения. Это свойство определяется типом элементов, применяемых для создания связей между узлами и блоками ПЛИС. Неограниченное количество циклов программирования характерно для схем с триггерной памятью конфигурации.

Уровень интеграции (сложность) может оцениваться числом эквивалентных логических вентилей (обычно под этим понимается элемент 2И-НЕ), размещенных на кристалле, либо их количеством, которое можно реализовать из имеющихся в составе кристалла элементов. Однако для сложных ПЛИС оценка по этому критерию затруднена, так как логические ячейки и блоки реализуются на иных цифровых структурах.

Поэтому был предложен некоторый набор эталонных схем, в частности типовые конфигурации регистров, дешифраторов и т. п. по максимальному количеству которых, реализуемых на конкретной ПЛИС и оценивается ее сложность. Еще один подход заключается в пересчете конфигурации реализованных узлов в число типовых вентилей, которые могли бы потребоваться для этого. Это дает оценку сложности в так называемых системных вентилях.

В реальных кристаллах ПЛИС не все имеющиеся вентили могут быть использованы в конкретном проекте. Их возможное число называется пользовательским. Оно в определенной мере зависит от сложности проекта, так как с этим связана топология соединений элементов ПЛИС. Регулярность структуры внутренних соединительных линий и их ограниченное число приводит к тому, что при реализации сложных устройств с большим количеством связей, некоторые блоки ПЛИС не смогут быть задействованы. Это, в частности связано с тем, что имеющиеся в области их расположения линии связи должны будут востребованы для соединения других узлов и блоков.

В настоящее время единой методики оценки сложности ПЛИС нет, так как ведущие фирмы производители занимают в этом вопросе неодинаковые позиции. Тем не менее, в справочных материалах приводятся данные о том, что современные ПЛИС FPGA фирмы Xilinx содержат на одном кристалле десятки миллионов эквивалентных вентилей, а CPLD – до десятков тысяч макроячеек.

Быстродействие ПЛИС оценивается либо по величине задержки распространения сигнала по конкретным путям, либо максимально возможной частотой работы схемы в целом, (системная частота), или максимальной частотой переключения счетного триггера, собранного на имеющихся в составе ПЛИС вентилях. Использование современных технологий позволяет реализовать вентили с задержками менее одной наносекунды и обеспечить рабочие частоты порядка двухсот и более мегагерц при напряжениях питания менее 3В.

Процедура проектирования цифрового устройства на ПЛИС заключается в организации связей между имеющимися элементами и блоками. Реализация таких связей является чисто технической задачей, которая решается с помощью специальных программаторов. Под их управлением в требуемые участки кристалла подаются электрические импульсы, под действием которых создаются либо разрушаются токопроводящие перемычки.

Вследствие огромной функциональной сложности ПЛИС, использование обычных подходов, применяемых для разработки узлов на микросхемах малой и средней степени интеграции невозможно. Это приводит к необходимости использования средств автоматизированного проектирования и соответствующих программ, к примеру пакета – MAX+PLUS II для схем фирмы Altera, а также специальных языков программирования, в частности VHDL, Verilog AHDL и другие.

Данные средства позволяют исключить необходимость проектирования системы с начального уровня, так как в составе САПР имеются библиотеки готовых компонентов: счетчиков, сумматоров и т.п., которые могут автоматически воспроизводиться на кристалле.

Применение современных ПЛИС позволяет решить ряд задач, реализация которых традиционными способами либо очень затруднительна, либо вообще невозможна.

Одно из таких направлений это создание реконфигурируемых систем. На практике довольно часто встречаются ситуации, когда те или иные блоки аппаратуры работают поочередно. Например, в узлах кодирования и декодирования данных, поступающих по одному каналу, эти операции не выполняются одновременно. Поэтому, в принципе, не обязательно иметь два устройства – кодер и декодер, а можно использовать одно, которое в зависимости от ситуации меняет вид выполняемой операции. Реализация этой идеи возможна при использовании ПЛИС с триггерной памятью конфигурации, кодировки структуры которых хранятся в некотором ПЗУ. Если в соответствующие моменты времени производить перепрограммирование связей, то одна и та же микросхема будет способна выполнять различные функции.

Второе направление позволяет решать задачи логической эмуляции. Обычно при разработке какого-либо устройства делается его прототип, (макетный образец) и с помощью реальных сигналов испытывается его работоспособность. При выявлении ошибок производится отладка и. т.п., что является достаточно длительным и дорогим процессом.

Работу цифрового устройства можно смоделировать на цифровой вычислительной машине. Такие модели легко корректируются при выявлении ошибок в проекте, обеспечивают возможность пошагового решения и.т.д. Однако существенным недостатком данного подхода является невозможность точно оценить свойства и характеристики реальной аппаратуры при работе с реальными сигналами.

Применение ПЛИС позволяет сочетать достоинства обоих подходов, так как требуемая аппаратная система создается и переконфигурируется программно, но, в то же время работает с физическими сигналами. В этом случае результаты испытаний будут соответствовать реальной ситуации.

На основе ПЛИС развивается новое направление динамически реконфигурируемых систем, которые могут использоваться в устройствах цифровой обработки сигналов с последовательным во времени порядком выполнения действий.

В таких устройствах имеется и хранится во внутренней памяти набор настроек, которые могут достаточно быстро сменять друг друга в соответствии с требованиями алгоритма обработки. К примеру, для сложения на каком-либо этапе двух чисел организуется сумматор, при необходимости их перемножения формируется аппаратный умножитель и т.д. При таком подходе алгоритм определяет структуру операционного узла, оптимизированного под каждую процедуру.