- •Федеральное агентство по образованию

- •1. Программируемые логические интегральные схемы

- •1.1 Принципы обработки цифровых данных.

- •1.2 Способы реализации логических функций.

- •1.3 Принципы построения и элементы программируемых логических интегральных схем.

- •1.4 Периферийное сканирование цифровых устройств.

- •2. Периферийные узлы цифровых устройств

- •3. Системы отбражения цифровой информации.

- •3.1 Способы управления одиночными светодиодными индикаторами.

- •3.2 Системы отображения многоразрядных цифровых данных.

- •3.3 Жидкокристаллические индикаторы и способы управления ими.

- •4. Цифроаналоговые и аналого-цифровые преобразователи

- •4.1 Цифроаналоговые преобразователи.

- •4.1.1 Основные параметры и характеристики.

- •4.1.2.Принципы построения цап прямого преобразования.

- •4.1.3 Умножающие цап.

- •4.1.4 Цап с косвенным преобразованием.

- •4.1.5 Области применения цап.

- •4.2 Аналого-цифровые преобразователи.

- •4.2.1 Основные параметры и характеристики.

- •4.2.2 Аналого-цифровые преобразователи с непосредственным преобразованием.

- •4.2.3 Ацп с косвенным преобразованием.

- •4.2.4 Области применения ацп.

- •Контрольные вопросы.

- •Лехин Сергей Никифорович

- •Часть 4.

1.2 Способы реализации логических функций.

П

ервый

из них состоит в использовании типовых

или расширенных наборов логических

элементов. Пусть требуется осуществить

функциональное преобразование над

четырьмя логическими переменными.

ервый

из них состоит в использовании типовых

или расширенных наборов логических

элементов. Пусть требуется осуществить

функциональное преобразование над

четырьмя логическими переменными.![]() .

Это выражение можно упростить

следующим образом После

преобразований получается одна из

минимальных форм представления функции

у,

и схема для ее реализации имеет вид,

представленный на рис. 1.7. Количество

элементов оказывается небольшим, но

функция, реализуемая таким устройством

задана жестко (аппаратно). Если в алгоритм

обработки потребуется ввести какие-либо

изменения, например убрать инверсию

.

Это выражение можно упростить

следующим образом После

преобразований получается одна из

минимальных форм представления функции

у,

и схема для ее реализации имеет вид,

представленный на рис. 1.7. Количество

элементов оказывается небольшим, но

функция, реализуемая таким устройством

задана жестко (аппаратно). Если в алгоритм

обработки потребуется ввести какие-либо

изменения, например убрать инверсию

![]() ,

то сделать

это в готовом узле невозможно.

,

то сделать

это в готовом узле невозможно.

|

X3 |

X2 |

X1 |

X0 |

А |

у (Di) |

|

0 |

0 |

0 |

0 |

А0 |

0 |

|

0 |

0 |

0 |

1 |

А1 |

0 |

|

0 |

0 |

1 |

0 |

А2 |

0 |

|

0 |

0 |

1 |

1 |

А3 |

0 |

|

0 |

1 |

0 |

0 |

А4 |

0 |

|

0 |

1 |

0 |

1 |

А5 |

0 |

|

0 |

1 |

1 |

0 |

А6 |

0 |

|

0 |

1 |

1 |

1 |

А7 |

0 |

|

1 |

0 |

0 |

0 |

А8 |

0 |

|

1 |

0 |

0 |

1 |

А9 |

0 |

|

1 |

0 |

1 |

0 |

А10 |

1 |

|

1 |

0 |

1 |

1 |

А11 |

0 |

|

1 |

1 |

0 |

0 |

А12 |

0 |

|

1 |

1 |

0 |

1 |

А13 |

0 |

|

1 |

1 |

1 |

0 |

А14 |

1 |

|

1 |

1 |

1 |

1 |

А15 |

1 |

|

Рис. 1.8. Табличное представление логической функции. | |||||

Другой

способ реализации логических функций

основан на использовании мультиплексора,

как универсального логического элемента.

На его управляющие входы подаются

логические переменные, а значения

функции выставляются на входах данных.

Так как их можно задавать произвольным

образом, то при таком подходе не меняя

структуры устройства можно реализовать

любую из функций, число которых связано

с количеством логических переменных

соотношением

![]() ,

где

,

где![]() количество управляющих входов

мультиплексора.

количество управляющих входов

мультиплексора.

Для реализации на мультиплексоре рассмотренной выше функции строится таблица в которой задаются значения функции на всех наборах ее аргументов (рис.1.8). При необходимости изменить вид функции достаточно перекоммутировать сигналы на входах данных мультиплексора.

Структура устройства для обработки цифровых сигналов, реализованного таким образом получается однородной, оно будет состоять из одинаковых элементов –мультиплексоров. Однако при этом возникает проблема избыточности, так как для реализации функции на мультиплексоре может потребоваться существенно большее количество реальных логических элементов, чем в первом случае. В мультиплексоре 16→1 их содержится более двадцати, и это число не зависит от вида реализуемой функции.

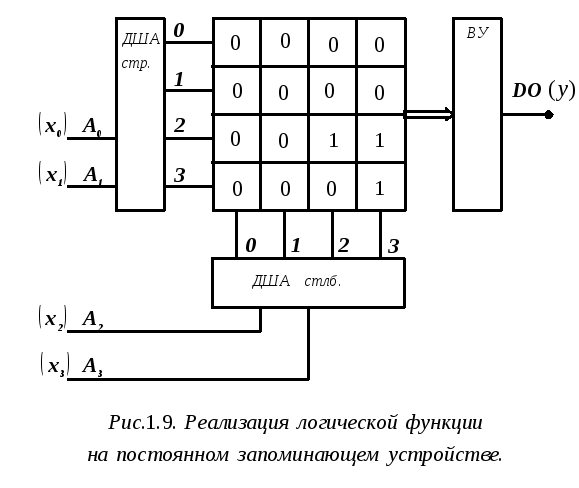

Е ще

один подход к воспроизведению произвольных

логических функций заключается в

использовании программируемых и

перепрограммируемых запоминающих

устройств. Их основой является матрица

ячеек (накопитель), каждая из которых

может быть переведена в состояние

логического нуля, либо единицы. Структура

запоминающего устройства емкостью 16

бит приведена на рис. 1.9. Свои состояния

ячейки накопителя могут сохранять

достаточно длительное время, либо

постоянно, в случае однократно

программируемых устройств. Состояние

ячейки можно прочитать, задав адрес,

который представляет собой ее порядковый

номер, представленный в двоичном коде.

ще

один подход к воспроизведению произвольных

логических функций заключается в

использовании программируемых и

перепрограммируемых запоминающих

устройств. Их основой является матрица

ячеек (накопитель), каждая из которых

может быть переведена в состояние

логического нуля, либо единицы. Структура

запоминающего устройства емкостью 16

бит приведена на рис. 1.9. Свои состояния

ячейки накопителя могут сохранять

достаточно длительное время, либо

постоянно, в случае однократно

программируемых устройств. Состояние

ячейки можно прочитать, задав адрес,

который представляет собой ее порядковый

номер, представленный в двоичном коде.

В ячейки с адресами от 0 до 15, представленного на рис. 1.9 запоминающего устройства, можно занести значения любой логической функции от четырех переменных, в том числе и рассмотренной ранее. При подаче на адресные входы комбинаций логических переменных на выходе запоминающего устройства будет формироваться соответствующее значение функции.

Количество логических переменных для которых можно реализовать любую из функций здесь определяется лишь разрядностью адресного пространства запоминающего устройства и, соответственно емкостью его накопителя. При таком подходе набор однотипных устройств также позволяет построить любой цифровой узел обработки сигналов.

Однако,

как и в случае с мультиплексорами,

данному варианту реализации логических

функций присуща избыточность. Если, к

примеру, требуется сформировать функцию

![]() ,

то нулями

придется заполнить все ячейки накопителя

кроме одной.

,

то нулями

придется заполнить все ячейки накопителя

кроме одной.

При увеличении количества переменных на единицу сложность мультиплексора и объем накопителя запоминающего устройства возрастают примерно в два раза, что существенно ограничивает возможности рассмотренных подходов при проектировании реальных многоразрядных цифровых устройств.

Новое направление в области реализации логических функций начало развиваться после разработки программируемых логических устройств - PLD (programmable logical device), которые выпускаются в двух вариантах: программируемые логические матрицы - ПЛМ (PLA - programmable logic array) и программируемая матричная логика – ПМЛ (PAL - programmable array logic). Идея их построения состоит в том, что связи между некоторым набором логических элементов, размещенных на кристалле микросхемы, могут задаваться пользователем относительно произвольным образом. При этом стандартная структура может быть сконфигурирована в требуемое цифровое устройство.

Основой ПЛМ служит набор элементов И и ИЛИ, а также входных и выходных буферов, которые могут выполнять операцию инверсии. Для реализации логической функции с помощью ПЛМ, ее надо представить в виде суммы конъюнкций, то есть в дизъюнктивной нормальной форме.

Пусть,

к примеру, требуется сформировать три

логические функции от четырех

переменных.:![]() ,

,![]() и

и![]() .

Это можно сделать с помощью ПЛМ, имеющей

структуру, приведенную на рис. 1.10. Она

состоит из четырех основных слоев:

первый –формирователь прямых и инверсных

значений входных переменных, второй –

слой элементов И, третий – элементов

ИЛИ, и четвертый – набор инверторов.

.

Это можно сделать с помощью ПЛМ, имеющей

структуру, приведенную на рис. 1.10. Она

состоит из четырех основных слоев:

первый –формирователь прямых и инверсных

значений входных переменных, второй –

слой элементов И, третий – элементов

ИЛИ, и четвертый – набор инверторов.

Пользователь получает в свое распоряжение ПЛМ со всеми связями между ее элементами. В этом случае при любой комбинации входных сигналов на выходах схем И будут сформированы логические нули, так как на их входы подаются прямые и инверсные значения каждой из переменных. Однако такая матрица может быть требуемым образом запрограммирована (скоммутирована). Суть программирования заключается в устранении пользователем специальных плавких перемычек, ненужных в конкретной ситуации. Это может быть осуществлено путем их пережигания.

Е сли

связи, помеченные на рис. 1.10 крестиками

устранить, то на выходах элементов И

будут формироваться все требуемые

конъюнкции, на выходах схем ИЛИ – прямые

значения логических сумм конъюнкций,

которые при необходимости могут быть

проинвертированы. Устранение перемычек

в других местах позволяет реализовать

иные логические функции. При таком

подходе программирование осуществляется

пользователем единственный раз, так

как удаленная перемычка не восстанавливается.

Аналогичный подход используется при

занесении информации в однократно

программируемые ПЗУ.

сли

связи, помеченные на рис. 1.10 крестиками

устранить, то на выходах элементов И

будут формироваться все требуемые

конъюнкции, на выходах схем ИЛИ – прямые

значения логических сумм конъюнкций,

которые при необходимости могут быть

проинвертированы. Устранение перемычек

в других местах позволяет реализовать

иные логические функции. При таком

подходе программирование осуществляется

пользователем единственный раз, так

как удаленная перемычка не восстанавливается.

Аналогичный подход используется при

занесении информации в однократно

программируемые ПЗУ.

В отличие от ПЗУ программируемая логическая матрица обладает гораздо меньшей функциональной избыточностью при регулярной структуре. Кроме того, в реальных ПЛМ используются не стандартные логические элементы, а их упрощенные варианты. В частности, схемы И выполняются на диодных сборках, ИЛИ - на одном многоэмиттерном транзисторе и т. п. Это позволяет создавать на одном кристалле достаточно мощные по функциональным возможностям устройства. Микросхема К556РТ1, представляющая собой ПЛМ на биполярных транзисторах, содержит в первом слое 48 тридцатидвухвходовых элементов И, что соответствует шестнадцатиразрядной входной шине. Во втором слое имеется восемь 48-входовых элементов ИЛИ с возможность инвертирования сигнала.

ПЛМ часто используется в качестве управляющей памяти для микроконтроллеров. При больших партиях выпускаемых изделий экономически целесообразно программирование их осуществлять на последнем этапе изготовления (как и для ПЗУ), путем нанесения токопроводящих дорожек через специальные шаблоны.

В ряде случаев логическая мощность ПЛМ используется неполностью. Это проявляется при воспроизведении логических функций не имеющих пересечений друг с другом по одинаковым наборам конъюнкций. В приведенном примере такими являются функции F1 и F3. Для их реализации наличие связей выходов любых конъюнкторов со входами любых дизъюнкторов становится излишним, а отказ от этого существенно упрощает структуру устройства.

Данная идея реализована в схемах программируемой матричной логики - ПМЛ, упрощенная структура одного из вариантов которой приведена на рис. 1.11. Программирование ПМЛ осуществляется таким же образом, как и для ПЛМ. Схемы программируемой матричной логики имеют меньшую функциональную гибкость по сравнению с ПЛМ, так как здесь любая конъюнкция используется лишь однократно, но структура связей между элементами проще.

Д

ля

расширения функциональных возможностей

программируемой логики в состав некоторых

ПЛМ и ПМЛ (КР1556ХП4 – ХП8) вводятся

последовательностные устройства, в

частности триггера и регистры (рис.

1.12). Здесь логическая матрица выполняет

роль комбинационного узла, кроме этого

имеется элемент памяти и цепь обратной

связи. Такое устройство представляет

собой последовательностную схему,

конфигурация которой может определяться

пользователем.

ля

расширения функциональных возможностей

программируемой логики в состав некоторых

ПЛМ и ПМЛ (КР1556ХП4 – ХП8) вводятся

последовательностные устройства, в

частности триггера и регистры (рис.

1.12). Здесь логическая матрица выполняет

роль комбинационного узла, кроме этого

имеется элемент памяти и цепь обратной

связи. Такое устройство представляет

собой последовательностную схему,

конфигурация которой может определяться

пользователем.

Еще одной разновидностью программируемых цифровых устройств являются базовые матричные кристаллы – БМК, которые представляют собой набор нескоммутированных логических вентилей и отдельных элементов - транзисторов, резисторов и т.п. Осуществление связей между ними обычно проводится на последней стадии изготовления БМК путем нанесения слоев металлизации на поверхность кристалла через специальные шаблоны, либо пользователем.

При таком подходе полуфабрикаты могут производится в массовых количествах без ориентации на конкретного заказчика. Придание им индивидуального характера, то есть реализация конкретного цифрового узла, происходит на последней стадии производства для чего необходимо лишь создание соответствующего шаблона. В этом случае разработка и изготовление какого либо устройства в интегральном исполнении требует гораздо меньших материальных и временных затрат по сравнению с проектированием и созданием такого же устройства как специализированной микросхемы.