- •Федеральное агентство по образованию

- •1. Программируемые логические интегральные схемы

- •1.1 Принципы обработки цифровых данных.

- •1.2 Способы реализации логических функций.

- •1.3 Принципы построения и элементы программируемых логических интегральных схем.

- •1.4 Периферийное сканирование цифровых устройств.

- •2. Периферийные узлы цифровых устройств

- •3. Системы отбражения цифровой информации.

- •3.1 Способы управления одиночными светодиодными индикаторами.

- •3.2 Системы отображения многоразрядных цифровых данных.

- •3.3 Жидкокристаллические индикаторы и способы управления ими.

- •4. Цифроаналоговые и аналого-цифровые преобразователи

- •4.1 Цифроаналоговые преобразователи.

- •4.1.1 Основные параметры и характеристики.

- •4.1.2.Принципы построения цап прямого преобразования.

- •4.1.3 Умножающие цап.

- •4.1.4 Цап с косвенным преобразованием.

- •4.1.5 Области применения цап.

- •4.2 Аналого-цифровые преобразователи.

- •4.2.1 Основные параметры и характеристики.

- •4.2.2 Аналого-цифровые преобразователи с непосредственным преобразованием.

- •4.2.3 Ацп с косвенным преобразованием.

- •4.2.4 Области применения ацп.

- •Контрольные вопросы.

- •Лехин Сергей Никифорович

- •Часть 4.

Федеральное агентство по образованию

ПСКОВСКИЙ ГОСУДАРСТВЕННЫЙ

ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ

С.Н. Лехин

СХЕМОТЕХНИКА ЭВМ

Учебное пособие

Часть 4

Псков

2006

УДК 681.3.06

ББК 32.973.26

Рецензенты: к.т.н.. Агафонцев В.В., Ильин С.Н.

Лехин С.Н.

Схемотехника ЭВМ: Учебное пособие. Часть 4.

ППИ, 2006 – 139 с.: ил.

Учебное пособие (часть 4) по дисциплине «Схемотехника ЭВМ» (СД. 03) предназначено для студентов Псковского государственного политехнического института специальности 230101 «Вычислительные машины, комплексы, системы и сети» очной, очно-заочной и сокращенной форм обучения.

В пособии рассмотрены принципы построения и работы программируемых логических интегральных схем, систем отображения цифровой информации, периферийных устройств цифровой техники, а также цифроаналоговых и аналого-цифровых преобразователей.

Учебное пособие может использоваться учащимися и студентами других специальностей и специализаций, интересующихся вопросами схемотехники узлов цифровых вычислительных машин.

УДК 681.3.06

ББК 32.973.26

Рекомендовано к изданию научно-методическим советом Псковского государственного политехнического института

© Псковский государственный политехнический институт

© С.Н. Лехин

1. Программируемые логические интегральные схемы

1.1 Принципы обработки цифровых данных.

В связи с возможностями, которые открывает использование цифровых сигналов в системах сбора, передачи данных, телекоммуникации, вычислительной техники важными являются вопросы, связанные с проектированием цифровых устройств для их обработки. В общем случае цифровая обработка заключается в реализации определенных функциональных преобразований над множеством входных данных, представленных в виде двухуровневых последовательностей. Конкретный вид таких преобразований, включающих в себя наборы арифметических и логических операций, зависит от решаемой задачи и задается алгоритмом обработки. Он описывает совокупность и последовательность действий, приводящих к требуемому результату.

В озможны

несколько подходов к аппаратной

реализации систем обработки сигналов.

Первый заключается в распределении

алгоритма обработки в пространстве. Он

предполагает представление функции,

описывающей связь входных и выходных

сигналов в виде совокупности простейших

логических и арифметических операций.

Сопоставляя каждой соответствующий

логический элемент или устройство и

организуя связи между ними, можно

построить узел, осуществляющий

необходимую процедуру обработки (рис.

1.1).

озможны

несколько подходов к аппаратной

реализации систем обработки сигналов.

Первый заключается в распределении

алгоритма обработки в пространстве. Он

предполагает представление функции,

описывающей связь входных и выходных

сигналов в виде совокупности простейших

логических и арифметических операций.

Сопоставляя каждой соответствующий

логический элемент или устройство и

организуя связи между ними, можно

построить узел, осуществляющий

необходимую процедуру обработки (рис.

1.1).

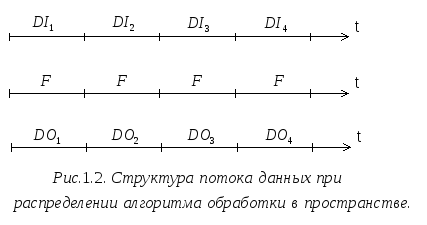

При

таком подходе требуемая очередность

элементарных операций над данными

реализуется путем соединения выходов

и входов цифровых устройств. Здесь

алгоритм обработки, определенный

соответствующей функцией

![]() жестко зафиксирован и на входы устройства

поступает лишь поток данных, который

трансформируется по неизменному во

времени алгоритму (рис. 1.2).

жестко зафиксирован и на входы устройства

поступает лишь поток данных, который

трансформируется по неизменному во

времени алгоритму (рис. 1.2).

Учитывая,

что задержки переключения с овременных

логических элементов достаточно малы

и ряд операций может выполняться

одновременно (параллельно), быстродействие

структуры с такой организацией оказывается

максимально возможным. В большинстве

случаев результат обработки получается

до поступления новой порции данных, то

есть обработка осуществляется в реальном

масштабе времени.

овременных

логических элементов достаточно малы

и ряд операций может выполняться

одновременно (параллельно), быстродействие

структуры с такой организацией оказывается

максимально возможным. В большинстве

случаев результат обработки получается

до поступления новой порции данных, то

есть обработка осуществляется в реальном

масштабе времени.

Такой подход получил название метода жесткой логики, так как функция, выполняемая соответствующим элементом и всей системой, не может быть изменена. В этом случае при необходимости введения каких либо коррекций в алгоритмы работы уже готового устройства, может потребоваться его существенная переделка, вплоть до разработки нового.

Используя аксиомы алгебры логики, любую логическую функцию можно преобразовать таким образом, что для ее реализации понадобятся лишь элементы 2И-НЕ, либо 2ИЛИ-НЕ. То есть имея набор однотипных элементов можно решить любую сколь угодно сложную задачу по цифровой обработке сигналов.

Однако в реальных ситуациях удобнее использовать более сложные функционально законченные узлы: мультиплексоры, триггера, сумматоры, регистры, счетчики и т.п., и на их основе строить требуемые устройства.

В этом случае на первом этапе разработки аппаратуры необходимо грамотно разбить функцию, подлежащую реализации, на подфункции, которые можно воспроизвести, применяя типовые узлы соответствующих серий микросхем. Однако здесь может возникнуть ряд проблем, в частности некоторые микросхемы могут использоваться не полностью, (например, требуется только один из двух или более триггеров, размещенных в корпусе), а некоторые узлы в составе серий не выпускается и их необходимо конструировать на основе имеющихся.

Кроме того, с ростом сложности решаемых задач резко возрастает количество требуемых корпусов микросхем и число связей между ними. Это приводит к увеличению габаритов и энергопотребления, а также к снижению надежности аппаратуры.

Любое устройство для цифровой обработки сигналов можно выполнить в интегральном исполнении, в виде одной или нескольких микросхем. Однако с экономической, ценовой точки зрения это оправдано лишь при производстве таких микросхем в количествах не менее сотен тысяч штук и более. Данное обстоятельство объясняется очень высокой стоимостью разработки и изготовления фотошаблонов, посредством которых формируются соответствующие слои полупроводников для получения элементов микросхемы.

В

торой

подход к проектированию цифровых узлов

заключается в распределении алгоритма

обработки во времени. Это подразумевает

использование устройства с программируемыми

функциями (УОПФ) которые могут меняться

в зависимости от набора управляющих

сигналов, называемых командой (рис.1.3).

Подавая их в определенной последовательности

можно реализовать любую логическую и

арифметическую операции, то есть

осуществить обработку данных по требуемым

алгоритмам. Необходимая для этого

последовательность команд, называется

программой. В данном случае на

соответствующие входы УОПФ должны

поступать потоки данных и команд

(рис.1.4.).

торой

подход к проектированию цифровых узлов

заключается в распределении алгоритма

обработки во времени. Это подразумевает

использование устройства с программируемыми

функциями (УОПФ) которые могут меняться

в зависимости от набора управляющих

сигналов, называемых командой (рис.1.3).

Подавая их в определенной последовательности

можно реализовать любую логическую и

арифметическую операции, то есть

осуществить обработку данных по требуемым

алгоритмам. Необходимая для этого

последовательность команд, называется

программой. В данном случае на

соответствующие входы УОПФ должны

поступать потоки данных и команд

(рис.1.4.).

Одним из примеров узла с программируемыми функциями является арифметико-логическое устройство - АЛУ, способное выполнять набор операций, зависящих от кода поступающей в данный момент времени команды.

С этой точки зрения, АЛУ можно считать неким универсальным устройством, позволяющим решать любые задачи, при неизменной внутренней структуре.

Развитием этой идеи была разработка микропроцессоров, представляющих собой сложные цифровые автоматы, у которых, выполняемая в текущий момент операция также определяется кодом поступающей команды. Однако, по сравнению с АЛУ, количество команд гораздо больше и соответственно возможности микропроцессоров шире.

При таком подходе одинаковые по структуре устройства могут использоваться для решения разных задач, так как алгоритм обработки задается последовательностью соответствующих команд. Это позволяет выпускать их большими партиями, что несмотря на достаточно сложную внутреннюю структуру и большие потенциальные возможности обуславливает невысокую стоимость таких устройств.

Если разработка цифровых узлом методом жесткой логики заключалась в основном в проектировании принципиальной схемы, то при втором подходе требуется создание программы для микропроцессора.

Однако, если необходима быстрая обработка больших массивов данных, второй подход к проектированию цифровых устройств может оказаться неприемлемым. Это объясняется тем, что в отличие от аппаратных методов реализации, где используются параллельные процедуры обработки, применение программных автоматов обязательно приводит к последовательному выполнению соответствующих действий, что существенно снижает скорость вычислений. Кроме того, разрядность микропроцессоров невелика, что вызывает необходимость обработки многоразрядных слов по частям и приводит к дополнительному снижению быстродействия.

Универсальность, присущая микропроцессорам приводит к элементной избыточности. При выполнении в текущий момент времени конкретной операции некоторые из его элементов будут незадействованы, но их наличие необходимо, так как они могут понадобиться в следующих тактах. Это приводит к тому, что число возможных состояний такой системы намного превышает количество рабочих при реализации конкретного алгоритма, что может являться причиной возникновения сбоев. Тем не менее, программируемые устройства очень широко используются в соответствующих областях.

Так как из-за ограниченности числа выводов микросхем, одни и те же контакты могут играть роль входов, выходов, адресных шин и т.п., то для разделения соответствующих сигналов, используются внешние регистры, мультиплексоры и аналогичные узлы на микросхемах невысокой степени интеграции с фиксированными видами выполняемых операций.

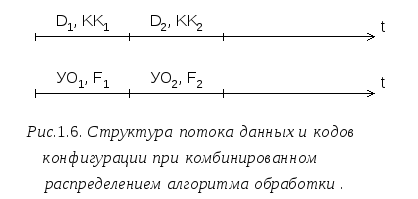

Т

ретий

подход к проектированию цифровых

устройств в какой-то мере сочетает

достоинства двух предыдущих. Его основная

идея заключается в том, что алгоритм

обработки одновременно реализуется в

пространстве и во времени посредством

устройств с программируемой конфигурацией

(УОПК) Алгоритм разбивается на достаточно

большие функционально завершенные

фрагменты, каждый из которых может

параллельно выполняться в устройстве

определенной конфигурации. Каждому из

разновидностей таких устройств

устанавливаются в соответствии коды

(команды) конфигурации - КК. Под действием

этих команд УОПК меняет свою внутреннюю

структуру, настраиваясь каждый раз на

реализацию фрагмента алгоритма (рис.1.6).

При этом, как и при первом подходе,

текущая процедура обработки оказывается

пространственно распределенной по

сконфигурированным на данный момент

узлам устройства.

ретий

подход к проектированию цифровых

устройств в какой-то мере сочетает

достоинства двух предыдущих. Его основная

идея заключается в том, что алгоритм

обработки одновременно реализуется в

пространстве и во времени посредством

устройств с программируемой конфигурацией

(УОПК) Алгоритм разбивается на достаточно

большие функционально завершенные

фрагменты, каждый из которых может

параллельно выполняться в устройстве

определенной конфигурации. Каждому из

разновидностей таких устройств

устанавливаются в соответствии коды

(команды) конфигурации - КК. Под действием

этих команд УОПК меняет свою внутреннюю

структуру, настраиваясь каждый раз на

реализацию фрагмента алгоритма (рис.1.6).

При этом, как и при первом подходе,

текущая процедура обработки оказывается

пространственно распределенной по

сконфигурированным на данный момент

узлам устройства.

Скорость обработки сигналов в таких устройствах на порядки больше, чем в предыдущем варианте, а сами они будут универсальными. В их состав, к примеру, может входить набор элементов 2И-НЕ, связи между которыми в каждый конкретный момент времени устанавливаются программно, а обработка в получившемся устройстве - сумматоре, преобразователе кодов и т. п., осуществляется аппаратно, параллельным образом.

В этом случае регулярность исходной структуры из одинаковых элементов позволяет обеспечить очень высокую степень интеграции микросхемы, а ее программируемость делает такое устройство универсальным, что в свою очередь позволяет выпускать их массовыми партиями при относительно небольшой цене.

Данное направление развивалось поэтапно, сначала были разработаны простейшие варианты программируемых логических интегральных схем – ПЛИС в виде программируемых логических матриц – ПЛМ и схем программируемой матричной логики – ПМЛ. Затем появились базовые матричные кристаллы – БМК, а в настоящее время выпускаются программно-реконфигурируемые системы цифровой обработки сигналов.