- •1.2. Основные характеристики и типы мп

- •Организация и особенности использования днокристальных микроконтроллеров

- •4.1. Общие сведения о микроконтроллере 1816

- •4.2. Организация микроконтроллера 1816

- •4.2.1. Функциональное назначение выводов корпуса мк

- •4.2.2. Арифметическо-логическое устройство

- •4.23. Память микроконтроллера

- •4.24. Организация ввода — вывода информации в мк

- •4.2.5. Управление работой микроконтроллера

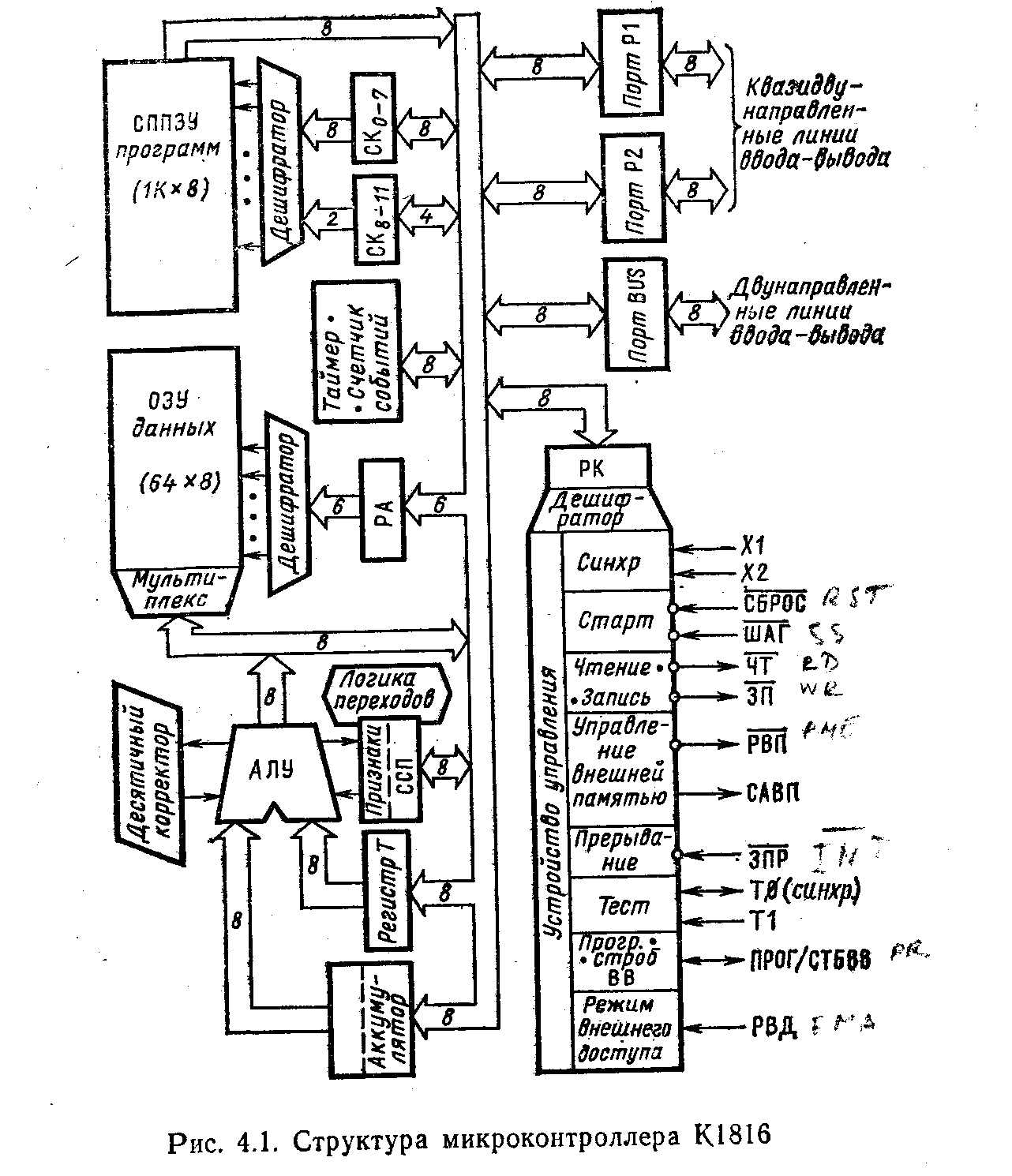

4.2. Организация микроконтроллера 1816

На рис. 4.1 показана структура МК 1816. Основу струк туры МК образует внутренняя двунаправленная разделяе мая 8-битная шина, которая связывает между собой все устройства БИС: арифметическо-логическое устройство, устройство управления, память и порты ввода—вывода ин формацц Рассмотрим последовательно основные элемен ты структуры и особенности организации МК.

4.2.1. Функциональное назначение выводов корпуса мк

Микроконтроллер 1816 конструктивно Выполнен в корпусе БИС с 40 внешними выводам и. Все выводы электрически совместимы с элементами ТТЛ, входы представляют собой единичную нагрузку, а выходы могут быть нагружены ОДНОЙ ТТЛ-нагрузкой. Ниже приводятся символические имена ВЫВОДОВ (сигналов), в скобках указываются номера выводов корпуса и дается краткое пояснение назначения вывода.

Земля (20) — потенциал земли.

Uосн (40) — основное напряжение питания +5 В подается во время работы и при программировании СIIПЗУ.

Uдоп (26) —дополнительноё напряжение питания +5 В во время работы МК обеспечивает электропитаниё только для СППЗУ; на этот вывод при программировании СППЗУ подается уровень +25 В.

ПРОГ/СТБВВ (25) —вход для подачи программирующего импульса +25 В при загрузке СГIПЗУ; выход стробирующего сигнала УВВ во время работы.

ХI (2) —вход для подключения вывода кварцевого осциллятора или вход для сигнала от внешнего источника синхронизации

Х2 (3) — вход для подключения второго вывода осциллятора.

СБРОС (4) вход сигнала общего сброса при запуске МК; сигнал 0 при программировании и проверке СППЗУ.

ШАГ (5) — сигнал, который совместно с сигналом САВП позволяет выполнять программу с остановом после исполнения очередной команды; используется на этапе отладки.

РПВ (9) — разрешение внешней памяти; сигнал подается на вход разрешения буфера внешней памяти только тогда, когда происходит обращение к внешней памяти программ.

САВП (11) —строб адреса внешней памяти; сигнал используется для приема и фиксации адреса внешней памяти на внешнем регистре, сигнал является идентификатором машинного цикла, так как всегда выводится из МК с частотой, в 5 раз меньшей основной частоты синхронизации.

ЧТ(8) — стробирующий сигнал при чтении из внешнёй памяти или УВВ.

ЭП (10) —стробирующий сигнал при записи во внешнюю память данных или УВВ.

Т0 (1) —входной сигнал, опрашиваемый по командам условного перехода ЛО и Л используется при программировании СППЗУ; может быть использован для вывода сигнала синхронизации по команде ENT0 CLK.

Т1 (39) — входной сигнал, опрашиваемый командами условного перехода JT1 и JNT1 кроме того, используется в качестве входа внутреннего счетчика внешних событий после исполнения команды STRT СNТ

ЭПР (б) — сигнал запроса прерывания от внешнего источника; вызывает подпрограмму обслуживания прерывания, если прерывание разрешено ранее по команде ЕNI сигнал СБРОС запрещает прерывания.

РВД (7) —режим внешнего доступа; уровень 1 на этом входе заставляет МИ выполнять выборку команд только из внешней памяти программ; используется при тестировании прикладной программы и отладке МК.

Порт Р1 0—7 (27—34) — 8-разрядный квазидвунаправленный порт ввода—вывода информации; каждый разряд порта может быть запрограммирован на ввод и вывод.

Порт Р2 (2 35—38)----8-разрядный квазидвунаправленный порт ввода — вывода информации; каждый разряд порта может быть запрограммирован на ввод или вывод; биты Р2 во время чтения из внешней памяти программ содержат старшие четыре разряда счетчика команд СК время ввода—вывода используются для схемы расширения ввода —вывода и адресуют внешние порты Р4—Р7.

Порт ВUS 0—7 (12—19) 8-разрядный двунаправленный порт ввода—вывода информации; может быть отключен от нагрузки; может выполнять прием и выдачу байтов синхронно с сигналами ЧТ и ЭП; при обращении к внешнему ППЭУ программ содержит 8 младших разрядов счетчика команд и затем по сигналу РВП принимает выбранную команду; при обращении к внешнему ОЗУ данных содержит младшие 8 раз рядов адреса синхронно с сигналом САВП и байт данных синхронно с сигналами ЧТ или ЭП.