- •Определение и принципы организации информационных процессов эвм

- •Принципы Фон Неймана

- •Классификация эвм по принципу действия

- •Классификация эвм по этапам создания

- •Классификация эвм по размерам и функциональным возможностям

- •Сравнительные параметры классов современных эвм

- •Классификация пк по поколениям процессоров

- •Классификация пк по типу используемого мп

- •Функционирование эвм с шинной организацией

- •Периферийные устройства

- •Обобщенный алгоритм функционирования классической эвм

- •Эвм с канальной организацией

- •Основные команды эвм

- •Основные термины и определения для пк ibmpc

- •Внешние интерфейсы

- •Типы корпусов и бп для пк

- •Форм-фактор матплат

- •Состав mb

- •Первоначальная загрузка и самотестирование пк

- •Шина расширения (шр)

- •Обобщенная архитектура шин

- •Чипсеты для mb

- •Блок-схемаMb на чипсете Intel 430fx

- •Блок-схема mb на чипсете Intel 440bx

- •Наборы микросхем системной логики для Pentium II/III

- •Современные mb

- •Архитектура mb для мп Hammer

- •Развитие современных мп

- •Архитектура современного мп

- •Идеология проектирования мп

Современные mb

Основная задача системной платы – это дать всем устройствам возможность работать на требуемых ими скоростях, а эти скорости постоянно растут. Также возрастает многообразие используемых интерфейсов, что влечет за собой изменения архитектуры системных плат в классическом дизайне Intel440BX. Взаимодействие между устройствами, требующими максимальной полосы пропускания (МП, ОП,AGP), происходит через системный контроллер (северный мост), в который включен также контроллер 32-х разрядной шиныPCI.

Через эту шину подключаются все прочие устройства, причем часть из них с помощью контроллера периферийных устройств (южный мост), который сам является PCI-устройством и включает в себя контроллерыIDE-устройств,USBи других устройств, т.е. шинаPCIкак бы разделяется на 2 части: быстрая (на севере) и медленная (на юге). Пиковая пропускная способность шиныPCI– 133 Мб/с, что с трудом хватало даже для режимаUltraDMA66, особенно с учетом того, что южный мост вынужден делить пропускную способность шины с другимиPCI-устройствами. Решение проблемы было предложено фирмойIntelв 1999 году – использовать для связи между мостами вместо шиныPCIспециальную шину типа «точка-тире-точка» с высокой пропускной способностью (хабовая архитектура, мосты называются хабы). Для обеспечения высокой пропускной способности и возможности ее наращивания в шине используется принцип трансляции ширины в частоту, но передавать данные на высокой частоте.

Шина IntelH18 (AHA), начавшая применяться в чипсетах серииi8xxимеет ширину 8 разрядов и передает данные с частотой 266 МГц. Реальная частота шиныAHA– 133 МГц, но используется режим 2x, т.е. данные передаются два раза за один такт. Пропускная способностьH18 составляет 266 Мб/c, для ее увеличения можно использовать параллельное включение двух шин (H116). Появились также и новые версии межмостовых шинIntel, которые называютсяHubLine(HL).

Шина HL-1.5 является 8-ми разрядной и обладает такой же пропускной способностью, что иH18 – 266 Мб/с. ШинаHL-2.0 является 16-ти разрядной и работает на более высокой частоте – 266 МГц, так что ее пропускная способность в 4 раза выше и равна 1,06 Гб/с. Аналогичный подход используют и другие производители чипсетов, напримерVIA(V-Link),SiS(MuTIOL,AML).HyperTransportимеет более универсальное назначение и поддержана многими производителями. Ее ширина от 2-х до 32-х бит и пропускная способность до 12,8 Гб/с.

Применение для связи между мостами специальной выделенной шины с высокой пропускной способностью внесло коррективы в архитектуру системных плат Intel810. Данная архитектура чипсета применяется в современных платах, однако уже разработан более радикальный подход к оптимизации внутрикомпьютерных соединений.

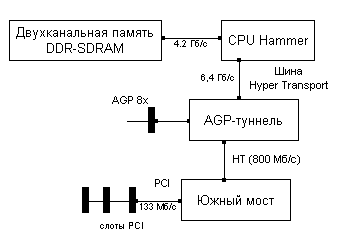

Архитектура mb для мп Hammer

МП AMDHammerимеет встроенный контроллер памяти, что устраняет допзадержки времени, возникающие при обращении к внешнему контроллеру. Кроме того он имеет один или несколько встроенных контроллеровHT, используемых для связи с южным мостом и другими МП (в многопроцессорных системах). Северный мост как таковой отсутствует, вместо него контроллерAGP-порта, служащий также туннелем (терминAMD) для обмена данными с южным мостом. В свете новой архитектуры роль шиныPCIизменилась, он по-прежнему остается основной шиной расширения, предназначенной для подключения внешних устройств. Для самых требовательных устройств имеются два варианта скоростной шиныPCI, контроллеры которой реализуются на дополнительных микросхемах, подключенных к северному мосту - 64-х разряднаяPCI, имеющая пропускную способность 533 Мб/с при частоте 66 МГц. Следующий шаг в росте пропускной способности обеспечивает 64-х разрядная шинаPCI-X, обладающая обратной совместимостью с 32-х и 64-х разрядной шинойPCIс тактовой частотой 133 МГц и пропускной способностью 1066 Мб/c. Предусмотрены версии, передающие за такт 2 или 4 пакета данных с пропускной способностью до 2.1 Гб/с и до 4.2 Гб/с соответственно.

На смену шине PCIвыходит технология 3GIO(ThirdGenerationI/O), которая была представлена фирмойIntelв феврале 2001 года (др. названиеSerialPCI). По замыслу ее создателей она обладает программной совместимостьюPCIи предназначена заменить последнюю в качестве межчипового соединения, а также в качестве шины расширения ПК и серверов на базе МПIntel. Принципиальное различие между 3GIOотPCIсостоит в том, что эта непараллельная разделяемая шина, а последовательная с архитектурой «точка-тире-точка». Один канал обеспечивает пропускную способность 2,5 Гб/c. В дальнейшем пропускная способность будет повышена до предельных значений для медных проводников (10 Гбит/с).

Каналов может быть до 32-х штук. В перспективе 3GIOможет заменить какPCI, так и другие соединения на уровнеMB, включаяAGPиIntelHubLinkи обеспечивают точки подключения всех внешних скоростных шин. Технология 3GIOоткрывает реальный путь к созданию так называемых «запечатываемых» компьютеров, обладающих некоторой способностью к модернизации, за счет модулей расширения в виде специальных картриджей; однако вопрос о том, получит ли такой подход поддержку индустрии, остается открытым.