- •4. ПОСЛЕДОВАТЕЛЬНОСТНЫЕ УСТРОЙСТВА

- •4.1. Регистры

- •4.1.1. Регистр памяти

- •4.1.2. Регистр сдвига

- •4.1.3. Кольцевой регистр

- •4.1.4. Универсальный регистр

- •4.2. Счетчики

- •4.2.1. Асинхронный двоичный счетчик

- •4.2.2. Синхронный двоичный счетчик

- •4.2.3. Синхронный двоичный реверсивный счетчик

- •4.2.4. Синхронный счетчик с входами прямого и обратного счета

- •4.2.5. Асинхронный двоично-десятичный счетчик

- •4.2.6. Синхронный двоично-десятичный счетчик

- •4.2.7. Счетчики с предварительной параллельной установкой

- •4.2.8. Счетчик с переменным модулем счета

- •4.2.9. Наращивание разрядности счетчиков

- •4.2.10. Кольцевые счетчики

- •4.3. Устройства обработки асинхронного сигнала

- •4.3.1. Схема устранения влияния вибраций механических контактов

- •4.3.2. Синхронизаторы асинхронных сигналов

- •4.3.3. Цифровые мультивибраторы

- •5. ПОЛУПРОВОДНИКОВЫЕ ЗАПОМИНАЮЩИЕ УСТРОЙСТВА

- •5.1. Оперативные запоминающие устройства

- •5.1.1. Принципы построения схем ОЗУ

- •5.1.2. Динамические параметры ОЗУ

- •5.1.3. Увеличение информационной емкости ОЗУ

- •5.2. Постоянные запоминающие устройства

- •5.2.1. Принципы построения схем ПЗУ

- •5.2.2. Программируемые ПЗУ

- •5.3. Флэш-память

- •5.3.1. Общий принцип работы ячейки флэш-памяти

- •5.3.2. Многоуровневые ячейки

- •5.3.3. Доступ к флэш-памяти

- •6. ПРОГРАММИРУЕМЫЕ ЛОГИЧЕСКИЕ ИНТЕГРАЛЬНЫЕ СХЕМЫ (ПЛИС)

- •6.1. Особенности программирования ПЛИС

16

Рис. 4.8. 4-разрядный двоичный асинхронный суммирующий счетчик К155ИЕ5:

а– схема, б – УГО

4.2.2.Синхронный двоичный счетчик

Триггеры счетчика будут переключаться синхронно, если входные импульсы поступят одновременно на тактовые входы триггеров всех разрядов. Для того чтобы выходные переменные соответствовали таблице состояний, т.е. чтобы все триггеры не переключались одновременно, необходимо использовать дополнительные схемы формирования переноса из младших разрядов в старшие. Такой способ объединения триггеров в единую систему отличает схемы синхронных, или параллельных, счетчиков. Их можно строить на основе следующих закономерностей табл. 4.2:

−переменная Q0 меняет свое значение после каждого входного импульса;

−переменная Qi ( i ≥1) меняет свое значение при поступлении очередного k -го импульса в том случае, если после ( k −1)-го импульса переменные всех младших разрядов имели единичное значение.

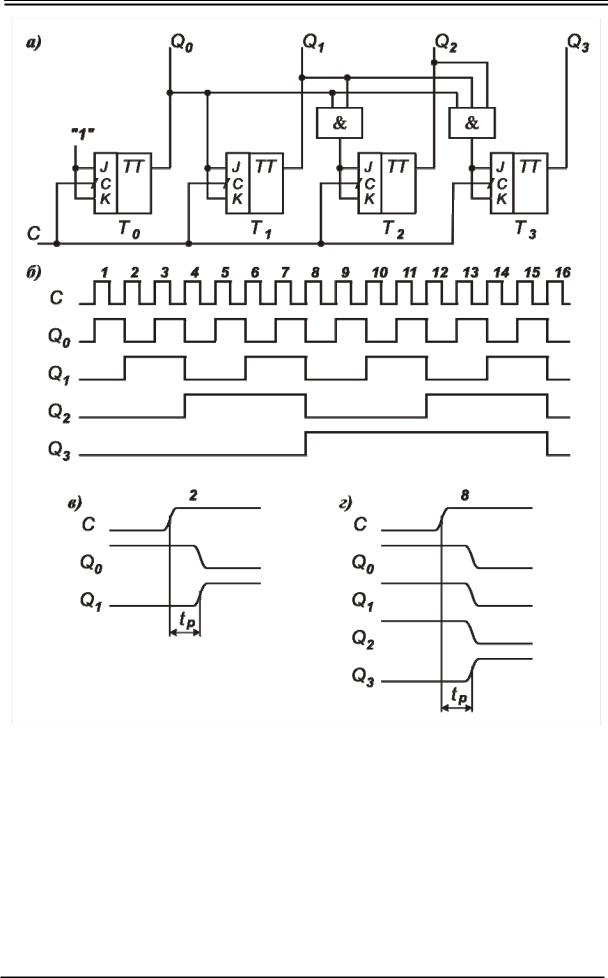

Схема синхронного суммирующего счетчика, составленная с учетом приведенных закономерностей, приведена на рис. 4.9а.

ЦИФРОВЫЕ УСТРОЙСТВА И МИКРОПРОЦЕССОРЫ. ЧАСТЬ 2

17 ПОСЛЕДОВАТЕЛЬНОСТНЫЕ УСТРОЙСТВА

Рис. 4.9. 4-разрядный двоичный синхронный счетчик: а – схема, б, в, г – временные диаграммы

Счетчик построен на динамических JK-триггерах, срабатывающих по фронту тактового сигнала. На информационных входах триггера T0

уровни J = K =1, поэтому он меняет свое состояние с каждым импульсом (рис. 4.9б). Так как время задержки переключения динамического триггера больше времени удержания (рис.2.20 [1]), то в интервале фронта 1-го импульса на входах J и K всех триггеров - нулевой уровень. Поэтому

18

после первого импульса переключается только триггер T0 . Разрешение на переключение триггера T1 дается сигналом Q0 (при J = K =Q0 =1 триггер T1 меняет свое состояние по фронту тактового импульса C , при Q0 =0

триггер T1 находится в режиме хранения). Первый раз триггер T1 переключается по фронту 2-го импульса (рис.4.9б). При этом происходит перенос единицы из разряда Q0 в разряд Q1 . Разрешение на переключение

триггеров T2 и |

T3 |

формируется с помощью элементов 2И и 3И |

соответственно. Перенос в разряд Q2 происходит при Q0 = Q1 =1 , в Q3 |

||

при Q0 =Q1 =Q2 |

=1. Переключение всех триггеров (при переносе единицы |

|

из младшего разряда |

Q0 в старший Q3 ) происходит одновременно. |

|

Значения Qi меняются спустя время задержки t р после фронта тактовых импульсов (рис.4.9г).

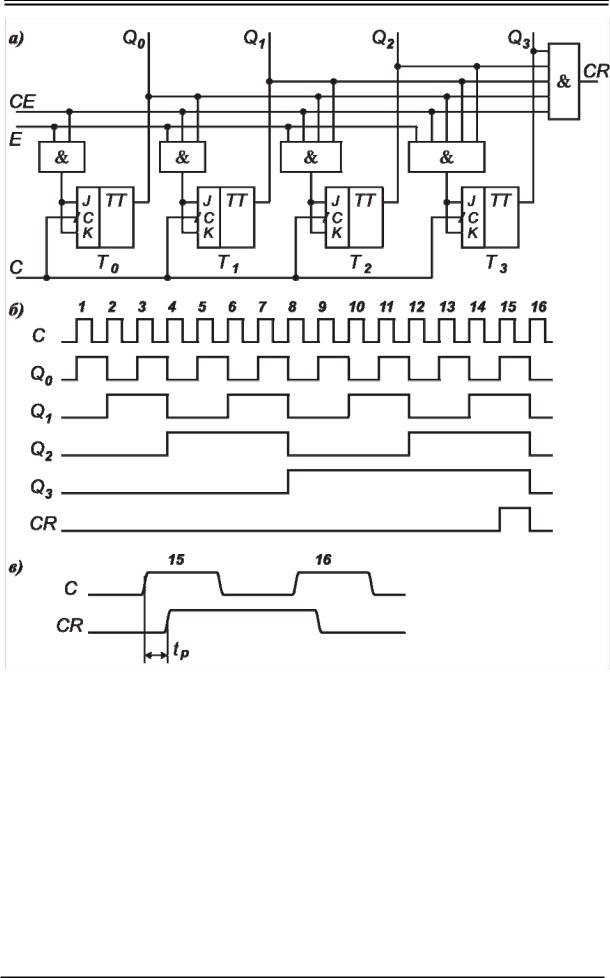

Счетчик, построенный по схеме рис.4.9а, может считать число импульсов от 0 до 15. Значительное наращивание разрядности в соответствии с этой схемой невозможно из-за отсутствия многовходовых элементов И. Поэтому многоразрядные счетчики строят путем соединения 4-х разрядных секций, каждая из которых имеет выход переноса CR и вход разрешения переноса CE (рис.4.10а). Если CE =0 , то триггеры меняют свое состояние под действием входных импульсов C . Когда значения всех разрядов секции равны 1 и CE =1 (во всех младших секциях все триггеры находятся в единичном состоянии), формируется сигнал переноса CR =1 в старшую секцию счетчика. С помощью выхода переноса и входа разрешения переноса можно создавать счетчики произвольной разрядности. Показанный на рис.4.10а счетчик имеет также вход разрешения счета E . При E = 0 счет запрещен (в счетчике хранится записанная информация), при E =1 - разрешен. Сигнал на входе разрешения счета не влияет на формирование переноса CR .

Временные диаграммы, иллюстрирующие работу счетчика с выходом переноса CR , приведены на рис. 4.10б, в. После 15-го импульса все триггеры переходят в единичное состояние и на выходе CR появляется единичный уровень. По фронту 16-го импульса происходит перенос единицы в младший разряд следующей по старшинству секции (этот

разряд |

имеет весовой коэффициент 24=16) и |

одновременно триггеры |

T0 −T3 |

возвращаются в нулевое состояние. При |

этом на выходе переноса |

CR появляется нулевой уровень и по фронту 17-го импульса срабатывает только младший триггер T0 данной секции.

ЦИФРОВЫЕ УСТРОЙСТВА И МИКРОПРОЦЕССОРЫ. ЧАСТЬ 2

19 ПОСЛЕДОВАТЕЛЬНОСТНЫЕ УСТРОЙСТВА

Рис 4.10. 4-разрядный двоичный синхронный счетчик: а – схема, б, в, – временные диаграммы при Е = СЕ = 1

Пример ИС:

К555ИЕ10 - 4-разрядный двоичный синхронный суммирующий счетчик (рис. 4.11).