- •Министерство общего и профессионального образования

- •Язык vhdl

- •Курсовое задание Вариант-7

- •Элементы использующиеся в архитектурах

- •Имя файла: Kunits.Vhd

- •Архитектуры

- •Имя файла: Kursovik.Vhd

- •Процедурное моделирование

- •Vhdl-проектов логических систем

- •2.5Ns 1 0 1 0 0 0 0

- •Файлы с сигналами входов схемы: r1,c1,ec

Курсовое задание Вариант-7

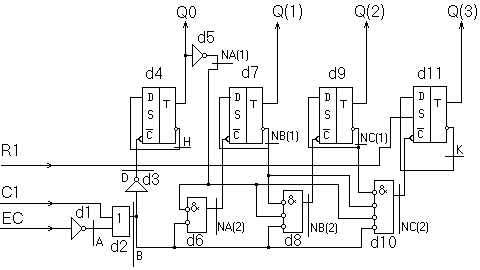

Данная схема содержит два синхронных двоичных счетчика- делителя (без дешифраторов). Каждый счётчик основан на четырёх D- триггерах. Линии С и ЕС(тактовая и разрешения тактов) взаимозаменяемые, но отличаются противоположными активными уровнями, поэтому можно организовать счёт по каждому фронту такта: по положительному и отрицательному.

ВХОД

C1ECR1

Режим

/ BHСчётчик работает

Н \ Н “

“

\ xН Код не

меняется

x / Н “

“

/ H Н “

“

B\ Н“

“

x x Н “

“

Элементы использующиеся в архитектурах

В этом файле содержатся элементы, использующиеся в архитектурах.

Элементы описаны специально в отдельном файле для удобства их применения.

Перед подключением компонент в архитектурах надо сначала откомпилировать этот файл чтобы потом подключить библиотеки.

Имя файла: Kunits.Vhd

entity sdnctt is

port(s,d,c: in bit; q,nq: inout bit);

end sdnctt;

architecture behavior of sdnctt is

signal stored,intsig: bit;

begin

process(s,d,c)

begin

if s = '1' then intsig <= '1'; stored <= '1';

elsif c = '1' and not c'stable then intsig <= stored;

elsif c = '0' then stored <= d;

end if;

q <= intsig;

nq <= not intsig;

end process;

end behavior;

entity mnd is

generic(p:natural:=2);

port (x: in bit_vector(1 to p);y: out bit);

end mnd;

architecture poh of mnd is

begin

process(x)

variable count: integer :=0;

begin

for i in x'range loop

if x(i) = '0' then count:= count + 1; end if;

end loop;

if count /= p then y<= '0' ;

else y<= '1' ;

end if;

end process;

end poh;

entity inv is

port(x: in bit;y: out bit);

end inv;

architecture beh of inv is

begin

y<=not(x);

end beh;

entity sum is

port(x,y: in bit;z: out bit);

end sum;

architecture sum_beh of sum is

begin

z<=(x or y);

end sum_beh;

Архитектуры

Архитектуры структурная и регистровая также содержатся в отдельном файле и перед подключением этого файла как библиотеку надо его откомпилировать.

Имя файла: Kursovik.Vhd

library kunits;

use kunits.all;

entity KURS is

port(r1,c1,ec: in bit; q: out bit_vector(1 to 3); qo: inout bit);

end KURS;

architecture KROT of KURS is

component inv

port(x: in bit; y: out bit);

end component;

component sum

port(x,y: in bit; z: out bit);

end component;

component mnd

generic(m:natural:=2);

port(x: in bit_vector(1 to m); y: out bit);

end component;

component SDNCTT

port(s,d,c: in bit; q,nq: inout bit);

end component;

for all: sdnctt use entity kunits.sdnctt(behavior);

for all: inv use entity kunits.inv(beh);

for all: mnd use entity kunits.mnd(poh);

for all: sum use entity kunits.sum(sum_beh);

signal na,nb,nc : bit_vector(1 to 2);

signal k,a,b,d,h: bit;

begin

d1: inv port map(ec,a);

d2: sum port map(c1,a,b);

d3: inv port map(b,d);

d5: inv port map(qo,na(1));

d6: mnd port map(na(1),b,na(2));

d8: mnd generic map(3)

port map(nb(1),na(1),b,nb(2));

d10: mnd generic map(4)

port map(nc(1),nb(1),na(1),b,nc(2));

d4: SDNCTT port map(r1,h,d,qo,h);

d7: SDNCTT port map(r1,nb(1),na(2),q(1),nb(1));

d9: SDNCTT port map(r1,nc(1),nb(2),q(2),nc(1));

d11: SDNCTT port map(r1,k,nc(2),q(3),k);

end krot;

architecture lis of KURS is

component SDNCTT

port(s,d,c: in bit; q,nq: inout bit);

end component;

for all: sdnctt use entity kunits.sdnctt(behavior);

signal na,nb,nc: bit_vector(1 to 2);

signal k,a,b,d,h: bit;

begin

d1: a<=not ec;

d2: b<=not c1 or a;

d3: d<=not b;

d4: SDNCTT port map(r1,h,d,qo,h);

d7: SDNCTT port map(r1,nb(1),na(2),q(1),nb(1));

d9: SDNCTT port map(r1,nc(1),nb(2),q(2),nc(1));

d11: SDNCTT port map(r1,k,nc(2),q(3),k);

d5: na(1)<=not qo;

d6: na(2)<= not(na(1)) and not(b);

d8: nb(2)<= not(nb(1)) and not(b) and not(na(1));

d10: nc(2)<= not(nc(1)) and not(nb(1)) and not(b) and not(na(1));

end lis;