- •Лекция 6 Топологическое проектирование.

- •Пример: топология кмоп инвертора.

- •Слои технологического файла.

- •Символы контактов

- •Топологические ограничения.

- •Разработка идеи топологического размещения элементов схемы.

- •Создание топологической ячейки (Layout Cellview).

- •Топологический редактор Virtuoso Editing и работа с окном задания и выбора маскирующих слоев Layer Selection Window (lsw)

- •Create Rectangle

- •Поликремниевый затвор.

- •Создание активного контакта.

- •Edit Copy

- •Выполнение охранного кольца n-типа

Топологические ограничения.

Ограничения слоев:

1A Минимальная ширина NWELL 1.0um

1B Минимальное расстояние между NWELL 1.0um

2A Минимальная ширина OXIDE 0.4um

2B Минимальная ширина OXIDE 0.3um

2C Минимальное перекрытие NWELL слоя OXIDE 0.5um

3A Минимальная ширина NIMP 0.4um

3B Минимальное расстояние между NIMP 0.4um

3C Минимальное перекрытие NIMP слоя OXIDE 0.2um

4A Минимальная ширина PIMP 0.4um

4B Минимальное расстояние между PIMP 0.4um

4C Минимальное перекрытие PIMP слоя OXIDE 0.2um

5A Минимальная ширина POLY 0.18um

5B Минимальное расстояние между POLY 0.3um

5C Minimum POLY extension beyond OXIDE (poly endcap) 0.2um

5D Minimum OXIDE extension beyond gate POLY 0.4um

5E Минимальное расстояние между Poly и OXIDE 0.2um

6A Минимальная и максимальная ширина CONT 0.2um

6B Минимальное расстояние между CONT 0.2um

6C Минимальное перекрытие OXIDE слояf CONT 0.2um

6D Минимальное перекрытие POLY слоя CONT 0.2um

6E Минимальное расстояние между POLY и CONT 0.2um

7A Минимальная ширина METAL1 0.3um

7B Минимальное расстояние между METAL1 0.3um

7C Минимальное перекрытие METAL1 CONT 0.1um

8A Минимальная и максимальная ширина VIA1 0.2um

8B Минимальное расстояние между VIA1 0.3um

8C Минимальное перекрытие METAL1 слоя VIA1 0.1um

9A Минимальная ширина METAL2 0.3um

9B Минимальное расстояние между METAL2 0.3um

9C Минимальное перекрытие METAL2 слоя VIA1 0.1um

10A Минимальная и максимальная ширина VIA2 0.2um

10B Минимальное расстояние между VIA2 0.3um

10C Минимальное перекрытие METAL2 слоя VIA2 0.1um

Начнем с идеи конструкции проектирования топологии и получим комплект маскирующих слоев используя возможности редактора.

Шаги топологического проектирования.

Старт

разработка идеи топологического размещения элементов схемы;

создание топологической ячейки (Layout Cellview);

вход в топологический редактор Virtuoso Editing и работа с окном задания и выбора маскирующих слоевLayer Selection Window (LSW)

N-МОП

прорисовка n-диффузионного слоя для создания областей стока и истока;

прорисовка поликремниевого затвора;

прорисовка омических контактов

прорисовка металлических нашлепок и межсоединений Metal-1;

прорисовка охранного кольца подлегирования n-слоем

P-МОП

прорисовка p-диффузионного слоя для создания областей стока и истока;

прорисовка поликремниевого затвора;

прорисовка омических контактов

прорисовка металлических нашлепок и межсоединений Metal-1;

прорисовка охранного кольца подлегирования p-слоем;

прорисовка области кармана n-типа (N-well)

Соединения между транзисторами

размещение P-МОП и N-МОП

соединение стоков и создание выхода (output)

соединение затворов и создание входа (input)

выполнение переходного окна от поликремниевого входа к слою металл-1

соединение истоков транзисторов с шинами питания

создание контакта подключения p-подложки к шине земли

создание контакта подключения n-кармана к шине питания

Проверка выполнения разводки межсоединений пректа (Design Rule Checking).

Разработка идеи топологического размещения элементов схемы.

Для прорисовки топологии схемы необходимы две составляющие:

Электрическая схема проекта

Диаграмма сигналов

Электрическая схема проекта

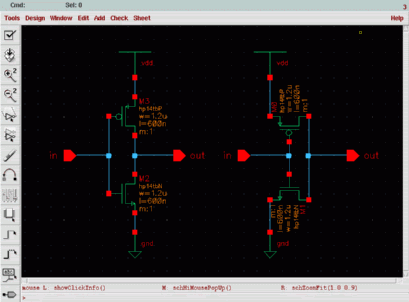

Ранее для схемотехнического или поведенческого моделирования разрабатываемой схемы уже создавалась прорисовка описания схемы в графическом редакторе Virtuoso как schematic. Однако для разработки идеи конструирования топологии необходимо модифицировать описанную схему, чтобы как можно короче выполнялись межсоединения для уменьшения паразитных эффектов RC-цепей. Поэтому на примере инвертора это преобразование описания схемы выглядит следующим образом.

В этом примере N-МОП и P-МОП транзисторы имеют одинаковые размеры W=1.2мкм и L=0.6мкм. Минимально-допустимый технологический

размер λ составляет 0.3мкм, поэтому минимальный допустимый размер слоя 2λ=0.6мкм.

Диаграмма сигналов.

Как правило проект включает в себя несколько подсхем. У каждой подсхемы, впрочем и у кристалла в целом, имеются входы и выходы. Необходимо так выполнить топологию, чтобы входы одной подсхемы можно было соединить с выходами другой подсхемы. При переходе на малые размеры технологии ограничение по площади кристалла в большей степени определяется выполнением межсоединений, поскольку размеры активных элементов интегральной схемы незначительны. Поэтому разработчик топологии обязан очень тщательно просмотреть возможные варианты размещения элементов и выполнения межсоединений.