Лабораторная работа №7.

Моделирование схемы с учетом экстрагированных паразитных элементов.

Задание

Лабораторная работа выполняется индивидуально. Каждому студенту необходимо разработать топологию КМОП триггера на базовом технологическом процессе GPDK 0,18 мкм и выполнить моделирование переходной характеристики с учетом экстрагированных RC элементов. Номер выполняемого задания соответствует номеру студента в списке группы.

№ |

|

|

|

Тип |

|

|

Фамлилия И.О. |

Wn |

Ln=Lp |

логического |

|

п/п |

|

[мкм] |

[мкм] |

элемента |

|

1 |

|

0.4 |

0.18 |

2И-НЕ |

Рис.1 |

2 |

|

0.54 |

0.18 |

|

Рис.2 |

3 |

|

0.72 |

0.18 |

|

Рис.1 |

4 |

|

0.9 |

0.18 |

|

Рис.2 |

5 |

|

1.08 |

0.18 |

|

Рис.1 |

6 |

|

1.26 |

0.18 |

|

Рис.2 |

7 |

|

1.44 |

0.18 |

|

Рис.1 |

8 |

|

1.62 |

0.18 |

|

Рис.2 |

9 |

|

1.8 |

0.18 |

|

Рис.1 |

10 |

|

1.98 |

0.18 |

|

Рис.2 |

11 |

|

2.16 |

0.18 |

|

Рис.1 |

12 |

|

2.34 |

0.18 |

2ИЛИ-НЕ |

Рис.3 |

13 |

|

2.52 |

0.18 |

|

Рис.4 |

14 |

|

2.7 |

0.18 |

|

Рис.3 |

15 |

|

2.88 |

0.18 |

|

Рис.4 |

16 |

|

3.06 |

0.18 |

|

Рис.3 |

17 |

|

3.24 |

0.18 |

|

Рис.4 |

18 |

|

3.42 |

0.18 |

|

Рис.3 |

19 |

|

3.6 |

0.18 |

|

Рис.4 |

20 |

|

3.78 |

0.18 |

|

Рис.3 |

21 |

|

3.96 |

0.18 |

|

Рис.4 |

22 |

|

4.14 |

0.18 |

|

Рис.3 |

23 |

|

4.32 |

0.18 |

|

Рис.4 |

24 |

|

4.5 |

0.18 |

|

Рис.3 |

В этой лабораторной работе, направленной на изучение сквозного проектирования ИС с помощью инструментальных средств Cadence, необходимо выполнить следующие этапы:

1.Ввести предложенную схему с помощью графического редактора

Virtuoso.

2.Создать символьное представление.

3. Ввести тестовую схему для моделирования переходной характеристики для проверки функционирования. Задать параметры

источников (например: логические уровни входных сигналов V1=0v, V2=3v, задержка td=20ns, фронт tr=1ns, срез tf=1ns, длительность t=50ns, период T=100ns)

4. |

По полученным характеристикам определить измеряемые |

||||||||

|

динамические параметры и заполнить таблицу. |

|

|||||||

|

|

|

|

|

|

|

|

|

|

Параметр |

|

tC |

|

tФ |

|

tЗД01 |

|

tЗД10 |

tЗД СР |

Значение |

|

|

|

|

|

|

|

|

|

5. |

Выполнить топологическое проектирование на топологических |

||||||||

|

ячейках 2И-НЕ или 2ИЛИ-НЕ, разработанных в лабораторной работе |

||||||||

|

№6. |

|

|

|

|

|

|

|

|

6. |

Выполнить программу проверки Правил Проектирования DRC для |

||||||||

|

подтверждения |

получения |

топологии |

триггера, удовлетворяющей |

|||||

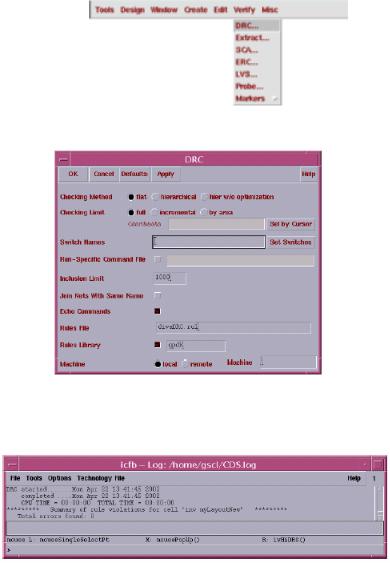

технологическим ограничениям и допускам. Из меню Verify выбираем опцию DRC

Далее открывается диалоговое окно опции DRC.

В окне DRC необходимо проверить, чтобы правильно были установлены библиотека (Rules Library) - gpdk и файл правил проверки - divaDRC.rul (Rules File).

Программа прошла успешно.

7. Выполнить программу Extract (экстракции схемы из топологии логического элемента) для извлечения из топологии транзисторов и межсоединений, а также паразитных RC элементов.

Из меню Verify выбирете опцию Extract

Проверяем в открывшемся окне правильность Rules File.

С помощью клавиши Set Switches задаем тип экстрагированных параметров и запускаем программу экстракции.

В результате работы программы экстракции получим новое представление ячейки – extracted. Откройте это представление с помощью Library Manadger и убедитесь, что экстрагированные RC элементы имеются в экстрагированной топологии. Красные прямоугольники указывают, что это компоненты внутри некоторой иерархии проекта. Нажимая Shift-F, можно видеть всю иерархию.

8.Выполнить программу проверки LVS для сравнения экстрагированного представления триггера со схемотехническим.

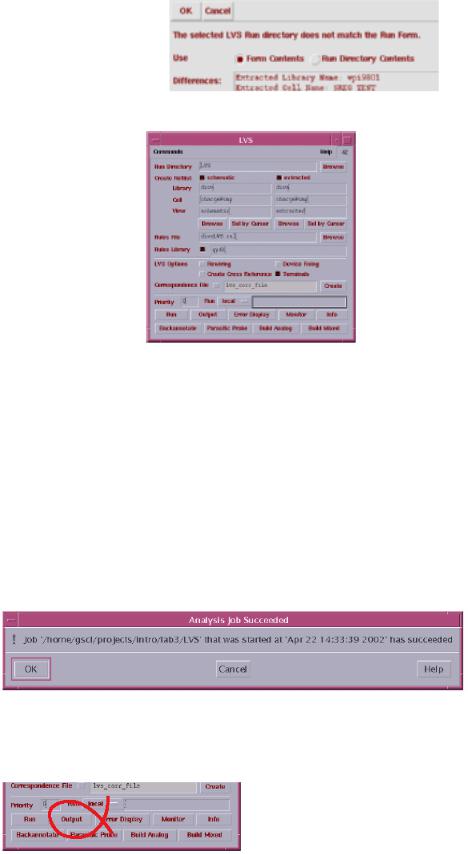

Из меню Verify выбираем опцию LVS.

Если Вы уже выполняли проверку LVS, то выскочит маленькое окно предупреждений. Удостоверитесь, что опция Form Contents выбрана в этом окне.

Появится окно LVS формы.

Верхная половина параметров LVS окна - разбита на две части. Часть слева соответствует схематическому представлению ячейки (schematic), и правая часть соответствует экстрагированному представлению ячейки (extracted), которые должны сравниваться. Удостоверьтесь, что данные введенное в этих рамках соответствуют значениям для вашей схемы.

Хотя имеется еще ряд параметров для LVS, выберете Run, чтобы запустить сравнение с заданными по умолчанию параметрами, достаточными для выполнения базисных вычислений.

Алгоритм сравнения выводится на заднем плане, результат выполненного LVS будет отображаться в окне сообщений. Первое сообщение: «LVS job now started». Будьте терпеливы, даже для очень маленького проекта, выполнение LVS может длиться некоторое время (минуты).

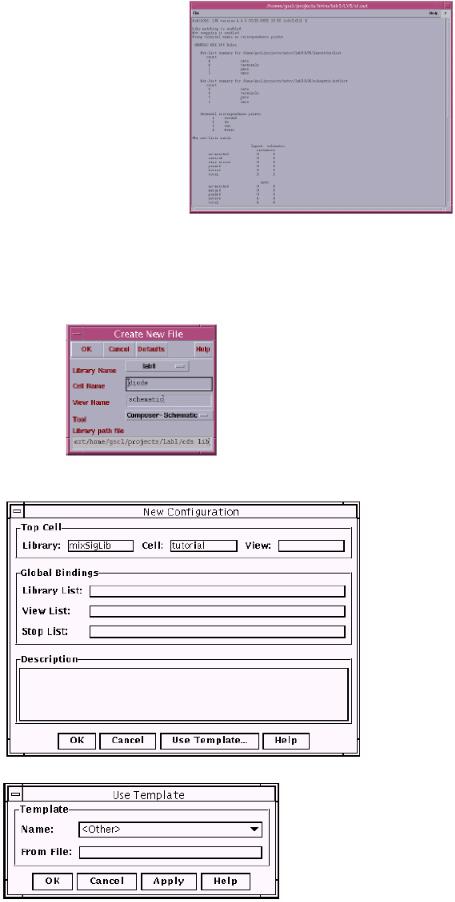

Для наблюдения за результатом выполнения LVS , Вы должны проверять распечатку работы программы LVS. Для этого надо выбрать в окне LVS опцию Output справа от команды Run.

9.Следующий шаг - получить в иерархическом редакторе конфигурацию для моделирования экстрагированного представления триггера.

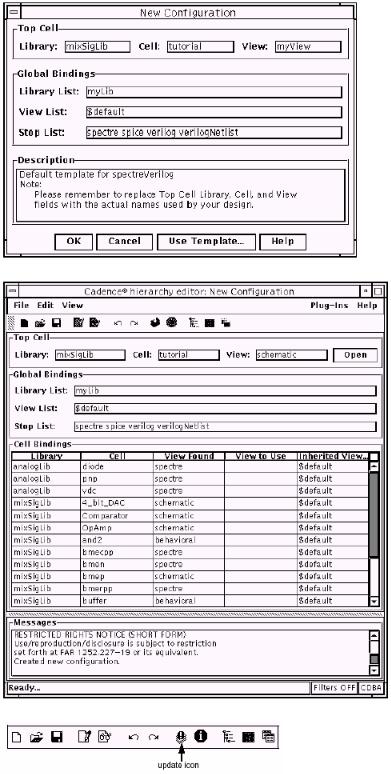

Выбираем в Library Manadger File → New → Cell View

config

config

Hierarchy-Editor

Hierarchy-Editor

Откроется окно новой конфигурации иерархического редактора

Заполняем окно Top Cell и выбираем клавишу Use Template.

В окне Name выбираем spectre и выполняем Apply и OK. В результате получим запоненное окно конфигурации.

После выполнения ОК получаем новую конфигурацию.

Введя в графе View to Use extracted и выполнив Update

получим схему с представлением config.

10.Выполнить моделирование переходного процесса для экстрагированного представления триггера с учетом паразитов. Заполнить таблицу динамических параметров.

Войдите в окне графического редактора Virtuoso схемы с представлением config в Tools → Analog Environment. Загрузите пакет исходных данных и выполните моделирование переходного процесса.

NS |

|

NR |

1 |

1 |

t |

|

NQ |

|

|

|

|

C |

|

NS |

|

t |

|

|

|

|

1 |

1 |

Q |

|

|

|

NR |

|

С |

|

|

t

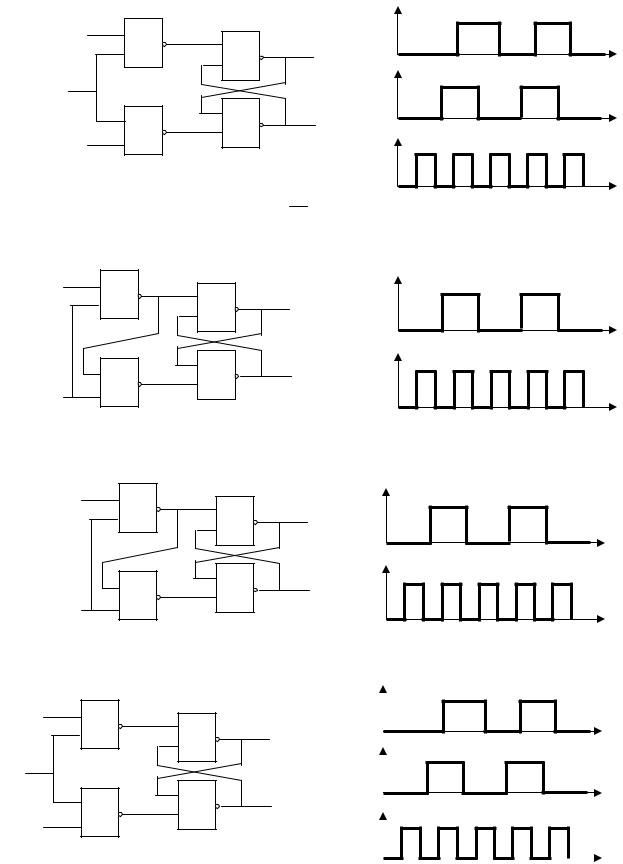

Рис.1. Синхронизируемый уровнем RS-триггер на элементах 2И-НЕ(2NAND)и входные воздействия.

D |

|

|

|

D |

|

1 |

|

Q |

|

|

1 |

t |

||

|

|

|

||

|

|

1 |

NQ |

С |

C |

1 |

|

||

|

|

t |

||

|

|

|

|

Рис.2. Синхронизируемый уровнем D-триггер на элементах 2И-НЕ (2NAND)и входные воздействия.

D |

|

|

|

D |

|

& |

|

Q |

|

|

& |

t |

||

|

|

|

||

|

|

& |

NQ |

С |

C |

& |

|

||

|

|

t |

||

|

|

|

|

Рис.3. Синхронизируемый уровнем D-триггер на элементах 2ИЛИ-НЕ (2NOR) и входные воздействия.

S |

|

R |

& |

& |

t |

|

Q |

|

|

|

|

|

|

S |

C |

|

t |

& |

& |

NQ |

|

||

R |

|

С |

|

|

t

Рис.4. Синхронизируемый уровнем RS-триггер на элементах 2ИЛИ-НЕ (2NOR) и входные воздействия.