- •1.1. Компенсация реактивной мощности 7

- •Здесь будет лист со штампом Общесистемный раздел

- •1.1. Компенсация реактивной мощности

- •1.2. Промышленные потребители реактивной мощности

- •1.3. Устройства компенсации реактивной мощности

- •1.4. Основные положения проектирования микропроцессорных устройств.

- •1.5. Pcad -основное средство проектирования микропроцессорных систем

- •1.5.1. Основные характеристики

- •1.5.2. Структура пакета

- •Здесь будет лист со штампом.

- •2. Специальный раздел

- •2.1. Техническое задание на разработку контроллера - компенсатора реактивной мощности

- •2.2. Общая характеристика

- •2.3. Обоснование элементной базы

- •2.3.1. Микропроцессор и микропроцессорный комплект

- •2.3.2. Память и логические элементы

- •2.3.3. Силовые элементы

- •2.4. Аппаратные средства контроллера

- •2.4.1. Плата контроллера

- •2.4.2. Плата тиристорного управления

- •2.4.3. Блок питания

- •2.4.4. Подключение контроллера – компенсатора

- •2.5. Алгоритмы контроля и управления

- •2.5.1. Измерение тока, напряжения и угла

- •2.5.2. Принцип управления конденсаторной установкой

- •2.6. Программное обеспечение контроллера

- •2.6.1. Структура программного обеспечения

- •2.6.1.1. Основная программа

- •2.6.1.2. Подпрограмма обработки прерывания trap

- •2.6.1.3. Подпрограмма обработки прерывания rst 7.5

- •2.6.1.4. Комплекс подпрограмм типа bios

- •2.6.2. Распределение адресного пространства

- •Область векторов прерываний

- •2.7.2. Технология разработки и отладки программ контроллера наIbm– совместимом компьютере.

- •2.7.3. Программные средства Сервисная программа контроллера-компенсатора

- •2.7.4. Конструктив

- •3. Организационно – экономический раздел

- •4. Раздел безопасности и экологичности Заключение

- •Литература

- •Приложение

1.5.2. Структура пакета

В системе P-CAD можно выделить следующие взаимосвязанные подсистемы:

подсистема входного проектирования;

подсистема проектирования печатных плат;

подсистема проектирования ПЛМ;

подсистема моделирования;

интерфейсы системы;

библиотека радиоэлектронных компонентов.

Каждая из этих подсистем включает в себя несколько взаимосвязанных пакетов.

Подсистема входного проектирования

Пакеты подсистемы имеют следующее назначение и краткую характеристику:

PC-CAPS - предназначен для проектирования принципиальных электрических схем РЭА и создания образов радиоэлектронных компонентов (РЭК). При этом формируется база данных электрических соединений и связей: для принципиальных схем файл с расширением .SCH; для РЭК - файл с расширением .SYM, эти вновь созданные РЭК используются в следующих этапах проектирования принципиальных схем.

Имеются средства редактирования и коррекции. Все функции пакета реализуются с помощью команд МЕНЮ в интерактивном режиме.

PC-NODES извлекает список электрических соединений из схематической базы данных, созданной посредством PC-CAPS, или из базы данных печатных плат, созданной посредством PC-CARDS (файл .PCB).

При этом присваиваются имена неименованным связям и создается таблица соединений. Результат работы - файл .NLT. Выходной список соединений потом может быть входным для PC-LINK, PC-FORM, PC-PACK, PRESIM, PC-ERC и интерфейсным программам.

PC-LINK из нескольких взаимосвязанных таблиц (списков) соединений, находящихся в нескольких базах данных, создает единую базу данных для принципиальной схемы, состоящей из нескольких листов.

Выходной файл с расширением .xnl. Он может быть входным для PC-PACK, PC-FORM, PRESIM и другим интерфейсным программам.

PC-ERC позволяет выполнить до десяти проверок проектирования схемы.

Это следующие проверки:

плавающие (floating) выводы;

цепи без или с одним соединением;

цепи без входных выводов;

цепи без выходных выводов;

цепи с несколькими (более одного) выходными выводами;

цепи без (pull-up) резистора;

цепи со всеми общими входными выводами;

несоответствие упаковки;

межплатных соединений(page connectors);

сумма числовых значений присвоенных атрибутам компонентов.

PC-ERC можно использовать для выполнения одной, всех или любой комбинации из этих проверок. Первые шесть тестируют на несоответствие цепей, следующие две на несоответствие компонентов и последние две формируют справочные отчеты.

Интерфейс с подсистемой проектирования ПП

PREPACK преобразует созданный пользователем текстовый файл (с расширением .FIL) из формата ASCII в двоичный формат (файл с расширением .LIB). Исходный файл (.FIL) содержит список используемых в схеме компонентов (логических элементов) из библиотеки компонентов (.SYM часть, см. описание библиотеки РЭК P-CAD). Выходной файл (.LIB) содержит двоичное описание РЭК , используемых в принципиальной схеме и является входным файлом для PC-PACK.

PC-PACK читает таблицу соединений (.XNL) электрической схемы из базы данных электрических схем, двоичный ссылочный файл используемых в схеме компонентов (.LIB), файл базы данных печатной платы (.PCB) и файл компонентов печатной платы (.PRT).

Он выводит следующее:

базу данных печатной платы (.PCB) с логическими вентилями, упакованными по кристаллам микросхем и соединенными согласно предварительному размещению на плате;

список физических соединений базы данных печатной платы (.pnl);

командный файл упаковки (.cmd), содержащий информацию об упаковке вентилей электрической схемы в физические микросхемы для обратной связи с исходной базой данных электрической схемы;

двоичный файл списка соединений схемы с номерами упакованных выходов элементов с ссылочными обозначениями, присвоенными каждому компоненту для ввода в интерфейсные программы.

PC-BACK считывает команды упаковки элементов (.cmd) и отчет размещений (.rpt), созданные соответственно в PC-PACK и в PC-CARDS, а затем генерирует обратный ссылочный файл (.bka), который может быть введен в PC-CAPS для обновления или изменения исходной схемы с учетом возможных изменений в PC-PLACE или PC-CARDS.

PC-NLC сравнивает и выдает отчет о несоответствии электрических соединений между двумя таблицами соединений. PC-NLC является гибкой программой, созданной для сравнения нескольких комбинаций списков соединений. Выходные отчетные файлы будут меняться в зависимости от сравниваемой комбинации.

Можно сравнивать следующее:

два списка соединений схемы (выбранные из баз данных, созданных с PC-CAPS);

два списка соединений ПП (выбранные из баз данных, созданных с PC-CARDS);

список соединений схемы со списком соединений ПП.

Подсистема проектирования пп

PC-PLACE, используя упакованную базу данных (файл .PKG, созданный с PC-PACK), выполняет в автоматическом или ручном (интерактивном) режиме размещение всех РЭК на ПП. Дополнительно (в тех же режимах) обеспечивает средствами векторов направленности, изображения гистограмм и связок цепей для анализа и оптимизации размещения.

Векторы направленности используют для указания теоретически "лучшего" места размещения каждого РЭК. Гистограммы (изображены цветом) представляют плотность потенциальных путей трассировки, а численный фактор указывает степень попытки положительного или отрицательного изменения размещения элементов. Изображение связки цепей (вывод элемента - вывод элемента, один РЭК, все РЭК сразу) помогает при анализе размещения РЭК.

Пользователь определяет следующие параметры:

указывает места точек привязки (lattice point);

определяет одну или несколько (lattice point);

определяет РЭК, которые будут размещены на каждом указанном (lattice point);

указывает (association) дискретного компонента к основным (ИС) или отдельно (lattice points) дискретных РЭК;

указывает определенные требования к зазором между РЭК;

задает управляющие параметры, устанавливающие порядок и ориентацию основных элементов в рамках контура ПП;

определяет место (outlinr);

определяет параметры изображения гистограмм;

выполняет предварительное размещение и фиксирует места их расположения;

PC-ROUTE читает файл (.PLC) базы данных, содержащей физическое размещение РЭК, упаковочную и логическую информацию и выполняет автотрассировку ПП. Пользователь может указать следующие параметры и стратегию трассировки:

метод соединений;

пары выводов с Т-образными соединениями;

пары выводов без Т-образных соединений;

только цепочечное соединение пар выводов;

стратегия трассировки;

качество трассировки;

большая скорость трассировки;

ширина проводников и зазоров;

разрешающая способность 0.001" (0.0254 мм);

отдельно определяемые конкретным цепям, таким как земля, питание;

зазоры контактных площадок и переходов;

разрешающая способность 0.001";

определяемые отдельно конкретным типам площадок и переходов;

вертикальные и горизонтальные прямые сетки;

резервирование точек переходов для предварительного размещения переходов;

количество трассируемых слоев;

количество проходов трассировки каждого слоя;

порядок трассировки;

вначале короткие соединения;

вначале длинные соединения;

Информация о состоянии трассировки:

изображение состояния только в текстовом виде;

изображение состояния и графического образа ПП, показывающих оттрассированные проводники и "воздушную линию" текущей трассируемой цепи;

статус, оттрассированые проводники, "воздушную линию" и область поиска пути трассировки текущей цепи.

Информация о состоянии трассировки включает:

общее количество пар слоев;

количество проходов трассировки на пару слоев;

общее количество соединений;

количество оттрассированных соединений;

количество оттрассированных проводников в процентах;

текущая трассируемая пара слоев;

текущий проход трассировки на паре слоев;

порядковый номер текущей трассируемой цепи;

Программные характеристики:

вводит базу данных ПП, созданную с PC-PLACE или PC-CARDS (с или без предварительной ручной трассировкой части цепей);

выводит оттрассированную базу данных ПП, которая может быть введена в PC-CARDS и отредактирована (дотрассирована).

PC-ROUTE поддерживает:

300 компонентов;

2500 цепей;

4000 выводов;

50 слоев;

60"х60" печатную плату с масштабом 1:1;

разрешающая способность для ширины и зазоров проводников (0.001");

внутренние слои цепей питания и земли.

PC-CARDS это интеллектуальный графический редактор топологии проектируемой ПП. Меню редактора включает набор команд для черчения, редактирования, вращения, копирования, уничтожения, перемещения и ввода компонентов, цепей и площадок. Многие из этих команд оперируют как с одиночными элементами, так и с их группами. Команды обзора обеспечивают 11 уровней увеличения и уменьшения, перемещение, сохранение и восстановление 10 изображений, а также обзор изображения, выбранного окна.

Утилиты ПП

PC-NLT преобразует файл формата ASCII со списком соединений схемы в файл базы данных ПП. Этот процесс выполняется в семь этапов:

1. Используя текстовый редактор, создается ASCII список соединений (<имя_файла>.ALT), который содержит компоненты и цепи схемы.

2. Используя PC-CARDS, если нужно создается первоначальная база данных ПП. Этот файл должен содержать уровневую структуру. Опционально он может содержать контур печатной платы и предварительно размещенные компоненты (например разъёмы). Если необходима только уровневая структура, файл LAYS.PCB может быть использован как первоначальная база данных ПП. В первоначальной базе данных не разрешены проводники.

3. Затем в ASCII формате вводится список цепей в PC-NLT, который создает следующие файлы:

базу данных ПП (<имя_файла>.PCB) содержащей компоненты и соединения между ними;

PC-NLT протокольный ("журнальный") файл (PCNLT.LOG), содержащий все сообщения поступившие при выполнении PC-NLT. Этот файл полезен при анализе любых сообщений об ошибках, которые создаются с PC-NLT;

файл отчета (по информативности можно выбрать четыре разных отчета).

4. Исследуется PC-NLT протокольный файл. Если обнаружены любые ошибки, исправьте их.

5. Затем можно заново пустить программу PC-NLT и указать параметры отчета для перечисления списка содержимого базы данных печатной платы. Можно выбрать и сгенерировать список компонентов по ссылочным обозначениям, по типу компонента, по именам цепей или по названиям схем.

6. Проверьте приведенный список со схемой. Если обнаружите ошибки, исправьте входной файл списка цепей. Затем вернитесь к PC-NLT и повторите шаги 4 и 5. Если ошибок нет, то выполняйте 7 шаг.

7. Теперь база данных ПП готова для размещения и трассировки.

PC-NODES назначение смотрите в описании подсистемы входного проектирования.

PC-NLC назначение смотрите в описании интерфейса ПП подсистемы входного проектирования.

PC-DRC считывает сгенерированный с PC-CARDS файл ПП из базы данных и проверяет его на несоответствие (несоединения) и нарушения (допусков), т.е. установленных правил проектирования. Эта программа генерирует дополнительный слой в базе данных ПП на котором помещаются ошибки проектирования, а также генерирует отчетный файл ASCII, в котором приводится список этих ошибок.

PC-PRINT считывает данные из плоттерного файла, созданного с PC-CAPS, PC-CARDS или PC-PLACE и преобразует его в инструкции (команды) принтера (мозаичного печатающего устройства).

PC-PLOTS считывает данные из плоттерного файла, созданного с PC-CAPS, PC-CARDS, или PC-PLACE и преобразует его в инструкции (команды) плоттера (чертежного устройства).

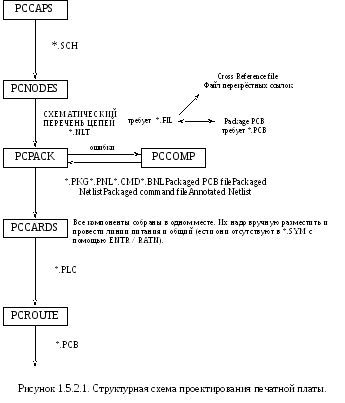

Последовательность действий, выполняемых при создании печатной платы, приведена на рисунке 1.5.2.1.

Интерфейс с производством

PC-DRILL считывает базу данных ПП (файл .PCB) и преобразует его в файл с форматом данных для сверлильного станка с ЧПУ.

PC-PHOTO считывает данные из плоттерного файла и преобразует их в инструкции фотоплоттера (фотокоординатографа). Эти инструкции вводятся непосредственно или косвенно (с диска) в фотоплоттер, который считывает команды черчения, размеров аппаратуры, выдержки и чертит фотошаблон.

Подсистема моделирования

PRESIM преобразует двоичную базу данных схемы (файл и /или файлы .NLT, .XNL) в формат совместимый с пакетом PC-LOGS.

PCMODEL компилирует модель поведения PC-LOGS. Скомпилированная модель добавляется к исследуемой базе данных препроцессором (пакетом PRESIM) к PC-LOGS.

PC-LOGS выполняет логическое моделирование базы данных.

POSTSIM используется для подготовки и просмотра результатов моделирования.

Библиотека радиоэлектронных компонентов

Библиотека радиоэлектронных компонентов базируется на общепринятых стандартах (западных стран). Графический образ РЭК использует стандартные его размеры, цоколёвку и расстояния между выводами, расположение текста в соответствии с ANSI стандартом. Где возможно для графических образов РЭК применяется IEEE стандарт.

Каждый компонент библиотеки имеет свой символьный графический образ РЭК (символьная часть, обозначаемая в библиотеке с расширением .SYM) и физический образ РЭК (упакованная по кристаллам микросхем часть, обозначаемая расширением .PRT). То есть, библиотека РЭК состоит как бы из двух частей - символьного (.SYM ) и физического (.PRT) графического представления РЭК.

Стандартная библиотека, представляемая с системой включает РЭК (.SYM и .PRT часть) типа TTL, CMOS, Линейные, дискретные, микропроцессоры семейства Intel, Motorpla, Zilog и другие. В целом библиотека содержит более 2000 компонентов.

Кроме того, пользователь, работая в символьном режиме, посредством PC-CAPS или PC-CARDS может дополнять библиотеку новыми РЭК. С PC-CAPS создается .SYM часть, а с PC-CARDS создается .PRT часть РЭК.