- •Электроника

- •Содержание

- •Раздел 1. Элементы электронной техники

- •Раздел 2.Истчники электропитания

- •Раздел3. Аналоговые интегральные микросхемы

- •Раздел 4. Цифровые интегральные микросхемы

- •Раздел 5. Фотоэлектрические приборы

- •Раздел 6. Аналого-цифровые функциональные устройства

- •Раздел 7. Микроконтроллеры

- •Раздел 1

- •Пассивные элементы электрических цепей

- •1.1 Резисторы

- •1.2 Конденсаторы

- •1.3 Индуктивности

- •1.4 Трансформаторы

- •2. Диоды

- •2.1 Принцип работы диода

- •Вольт-амперная характеристика диода

- •2.2 Выпрямительные диоды

- •2.3 Высокочастотные диоды

- •2.4 Импульсные диоды

- •2.5 Стабилитроны и стабисторы

- •3. Биполярные транзисторы

- •3.1Общие принципы

- •3.2 Основные параметры транзисторов

- •3.3 Схемы включения транзисторов

- •3.4 Ключевой режим работы транзистора

- •3.5 Усилительный режим работы транзистора

- •3.5 Способы задания рабочей точки по постоянному току в усилительном режиме

- •3.6 Схема включения транзистора с общим коллектором

- •4. Полевые (униполярные) транзисторы

- •4.1 Полевой транзистор с p-n переходом

- •Входные и выходные характеристики полевого транзистора с p-n переходом и каналом n-типа

- •4.2 Полевые транзисторы с встроенным каналом

- •Входные и выходные характеристики моп - транзистора с встроенным каналом n -типа (кп 305)

- •4.3 Полевые транзисторы с индуцированным каналом

- •Крутизна

- •Особенности полевых моп транзисторов

- •Режимы работы каналов и полярности электродных напряжений полевых транзисторов

- •5. Генераторы электрических сигналов

- •5.1 Принципы построения генераторов.

- •5.3 Генераторы импульсов на логических элементах ттл и таймере 555 (кр1006ви).

- •6. Силовые полупроводниковые приборы

- •6.2 Тиристор.

- •6.3 Симисторы

- •6.4 Igbt транзистор

- •Раздел 2

- •7.1 Однофазный мостовой выпрямитель

- •7.2Стабилизаторы напряжения

- •7.2.1 Параметрические стабилизаторы напряжения

- •Раздел 4

- •8. Аналоговые микросхемы.

- •8.1 Свойства оу

- •Практическая трактовка свойств оу

- •8.2 Основы схемотехники оу

- •Входной дифференциальный каскад

- •Современный входной дифференциальный каскад

- •8.3 Параметры операционных усилителей

- •8.4 Принцип отрицательной обратной связи

- •8.5 Основные схемы включения оу. Инвертирующее включение

- •Применение инвертирующего усилителя в качестве интегратора

- •Неинвертирующее включение

- •Ограничитель сигнала

- •8.6 Компараторы

- •8.7 Триггер Шмитта

- •8.8 Схема мультивибратора

- •8.9 Активные фильтры

- •9.2 Обозначение и типы комбинационных логических микросхем

- •9.3 Структура ттл логических микросхем

- •Основные параметры логических ттл элементов

- •9.4 Микросхемы последовательного тип

- •9.4.1 Интегральные триггеры

- •9.4.2 Rs асинхронный триггер

- •9.4.3 Асинхронный d - триггер

- •9.4.4 Синхронный d - триггер со статическим управлением

- •9.4.5 Синхронный d -триггер с динамическим управлением

- •9.4.6 Синхронный jk - триггер

- •9.4. 8. Вспомогательные схемы для триггеров

- •9.4.9 Формирователь импульса

- •Мультиплексоры и демультиплексоры

- •Шифраторы, дешифраторы и преобразователи кодов

- •Счётчики импульсов

- •Раздел 5 Фотоэлектронные приборы

- •Отоэлектрические приборы.

- •10.1 Понятия о оптоэлектронных приборах

- •10.2 Элементы оптоэлектроники.

- •Раздел 6

- •11. Аналого-цифровые преобразователи

- •Основные характеристики интегрирующих ацп

- •12. Цифро-аналоговые преобразователи

- •Характеристики интегральных микросхем цап

- •Раздел 7

- •13. Микропроцессоры

- •13.1 Cisc--процессоры

- •13.2 Risc—процессоры

- •14. Компьютерное моделирование электронных устройств

- •15. Используемая литература

Шифраторы, дешифраторы и преобразователи кодов

Схемы, предназначенные для преобразования цифровой информации из десятичной системы счисления в двоичную, обычно называются шифрирующими, а для обратного преобразования - дешифрирующими. Схемы, предназначенные для преобразования различных кодов в двоичной системе, называют преобразователями кода. Все эти схемы относятся к узлам комбинационного типа.

Шифраторы. Составление таких схем основано на комбинационной таблице. Здесь показан пример разработки схемы преобразования десятичных цифр 0÷9 в код 8421.

Таблица 13.1 - Комбинационная таблица шифратора

-

цифра

Код «1 из 10»

Код 8421

0

1

2

3

4

5

6

7

8

9

D

С

B

А

0

1

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

1

0

0

0

0

0

0

0

0

0

0

0

1

2

0

0

1

0

0

0

0

0

0

0

0

0

1

0

3

0

0

0

1

0

0

0

0

0

0

0

0

1

1

4

0

0

0

0

1

0

0

0

0

0

0

1

0

0

5

0

0

0

0

0

1

0

0

0

0

0

1

0

1

6

0

0

0

0

0

0

1

0

0

0

0

1

1

0

7

0

0

0

0

0

0

0

1

0

0

0

1

1

1

8

0

0

0

0

0

0

0

0

1

0

1

0

0

0

9

0

0

0

0

0

0

0

о

0

1

1

0

0

1

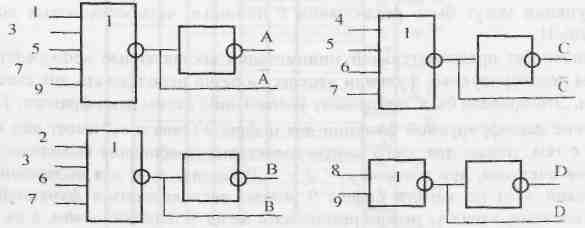

Из таблицы (и на рисунке 13.1) видно, что двоичным цифрам 1 в столбике А соответствуют десятичные цифры 1, 3, 5, 7 и 9, т. е. можно написать: А=1 + 3 + 5 + 7+9. Это алгебраическое выражение логического сложения. Точно так же справедливо, что: В = 2 + 3 + 6 + 7; С = 4 + 5 + 6 + 7;D= 8 + 9. На рисунке 13.1 представлен пример реализации схемы на элементах ИЛИ-НЕ. В состоянии покоя на всех входах низкий уровень. Подобным образом можно составить схемы преобразования десятичных цифр в любой код.

в базисе ИЛИ-НЕ

Рисунок 103 - Шифратор цифр 0÷9 в код 8421

Дешифраторы. При разработке различного рода цифровых управляющих устройств часто необходимо решать задачу, когда управляющее воздействие определяется значениями входных сигналов только в данный момент времени и не зависит от их значений в предыдущие моменты времени. Иными словами, выходной сигнал, характеризующий управляющее воздействие, здесь зависит только от наличия соответствующей комбинации сигналов на входах устройства. Примером таких комбинационных схем являютсядешифраторы.

Дешифратором называют комбинационную логическую схему, в которой каждой из комбинаций сигналов на входах соответствует сигнал только на одном из его выходов. Они находят применение в управляющих системах для выдачи управляющих воздействий в те или иные цепи в зависимости от комбинации сигналов на входах.

Значения сигналов а, b, с,dна выходах счетчика и

требуемые при этом показания

дешифратора могут быть использованы

для определения элементов схемы

дешифратора. Так, при нулевом показании

счетчика сигнал «1» присутствует на

инверсных выходах его триггеров (см.

таблицу 13.2), в связи с чем реализуемая

каналом![]() функция будет:

функция будет:

![]() .

.

Таблица - Состояния дешифратора

|

Число входных импульсов |

Триггеры счётчика |

Выходы дешифратора | ||||||||||||

|

Тр4 (d) |

Тр3 (с) |

Тр2 (b) |

Тр1 (а) |

x0 |

x1 |

x2 |

x3 |

x4 |

x5 |

x6 |

x7 |

x8 |

x9 | |

|

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

1 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

2 |

0 |

0 |

2 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

3 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

|

4 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

|

5 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

|

6 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

|

7 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

|

8 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

|

9 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

о |

1 |

Аналогично для канала

![]() имеем:

имеем:

![]() ;

а для канала

;

а для канала![]() :

:

![]() .

Логические функции могут быть реализованы

с помощью четырехвходовых логических

элементов И.

.

Логические функции могут быть реализованы

с помощью четырехвходовых логических

элементов И.

Однако без предварительной минимизации

составленные непосредственно из таблицы

дешифрируемые функции нецелесообразно

использовать для схемной реализации.

Это привело бы к заведомому усложнению

схемы дешифратора. Табличное выражение

дешифрируемой функции для цифры 9 (канала

![]() )

имеет вид

)

имеет вид

![]() .

Вместе с тем, только для этого канала

характерна комбинация выходных сигналов

триггеров счетчика, при которой

.

Вместе с тем, только для этого канала

характерна комбинация выходных сигналов

триггеров счетчика, при которой

![]() .

В связи с этим для выделения сигнала

(логической «1») по каналу цифры 9 можно

воспользоваться функцией

.

В связи с этим для выделения сигнала

(логической «1») по каналу цифры 9 можно

воспользоваться функцией

![]() .

Иными словами, канал

.

Иными словами, канал![]() можно реализовать не на четырёхвходовом,

а на двухвхо-довом логическом элементе

И.

можно реализовать не на четырёхвходовом,

а на двухвхо-довом логическом элементе

И.

Минимизацию функций дешифратора удобно проводить по карте Карно, которая составляется в данном случае для четырех переменных.

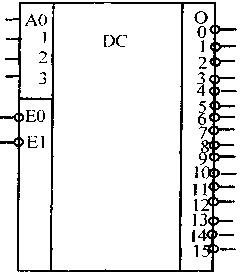

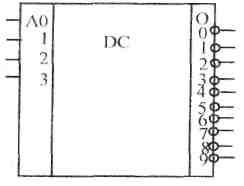

Электронная промышленность выпускает дешифраторы в виде интегральных схем, например, в серии 1533 интегральные схемы КР1533ИДЗ, КР1533ИД6. ИХ условное графическое обозначение приведено на рисунке 104.

1533ИД3 1533ИД6

Рисунок 104 - Интегральные схемы дешифраторов серии 1533

Преобразователи кодов. Преобразователем кодов называется логическое устройство, предназначенное для изменения кода информации, передаваемой и обрабатываемой цифровыми устройствами. Существующее множество кодов предназначено для обеспечения удобства перевода чисел из десятичной системы в двоичную, простоты выполнения арифметических операций и контроля результатов вычислений. Выбор кода влияет также на аппаратные затраты реализуемых схем цифровых устройств и на надежность выполнения ими заданных алгоритмов.

Рассмотрим синтез комбинационных преобразователей кодов на примерах преобразования двоично-десятичного кода 8421 в широко применяемый в цифровых устройствах двоично-десятичный код 2421. Алгоритм преобразования двоично-десятичного кода 8421 в код 2421 может быть представлен таблицей истинности (таблица 13.3).

Таблица 13.3 - Таблица истинности преобразователя кода 8421 в код 2421

-

Десятичное число

Код

8421

2421

х4

x3

x2

x1

F4

F3

F2

F1

0

0

0

0

0

0

0

0

0

1

0

0

0

1

0

0

0

1

2

0

0

1

0

0

0

1

0

3

0

0

1

1

0

0

1

1

4

0

1

0

0

0

1

0

0

5

0

1

0

1

1

0

1

1

б

0

1

1

0

1

1

0

0

7

0

1

1

1

1

1

0

1

8

1

0

0

0

1

1

1

0

9

1

0

0

1

1

1

1

1