2005_podyak / кафедра 17

.doc2.4.2 Комбинационные двоичные сумматоры

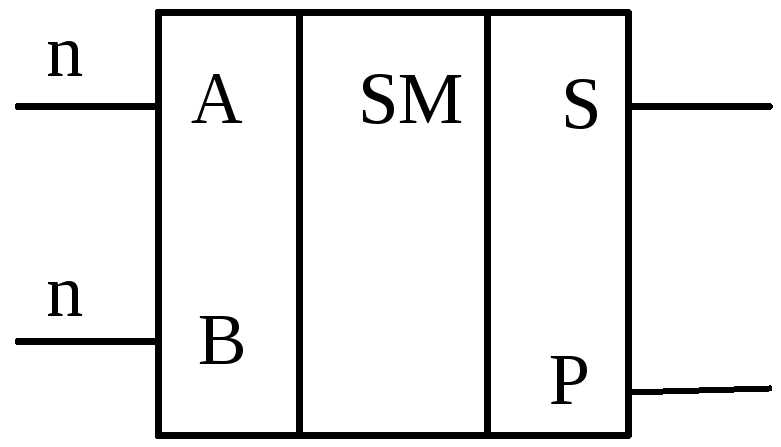

Двоичный сумматор (рис.2.16) представляет собой логическое устройство, формирующее сумму “S” n- разрядных двоичных чисел А и В. При этом также создается сигнал переноса P в следующий (I+1) разряд.

В основе построения много разрядного

сумматора лежит одноразрядный сумматор,

представляющий собой устройство

суммирования трех одноразрядных чисел:

одноименных разрядов двух двоичных

чисел и сигнала переноса от суммы

предыдущих разрядов.

основе построения много разрядного

сумматора лежит одноразрядный сумматор,

представляющий собой устройство

суммирования трех одноразрядных чисел:

одноименных разрядов двух двоичных

чисел и сигнала переноса от суммы

предыдущих разрядов.

Рис.2.16

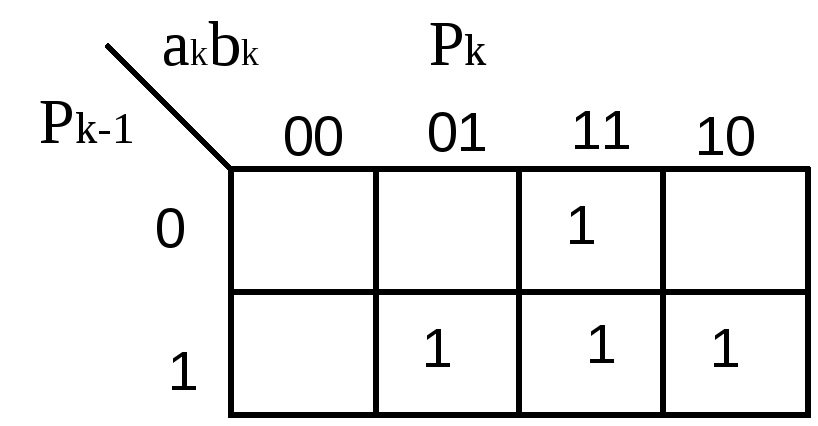

Таблица истинности одноразрядного сумматора (табл. 2.14), построенная по правилам суммирования двоичных чисел, приведена применительно к процедуре сложения к-тых разрядов аk, bk и сигнала переноса Pk-1

Таблица 2.14

|

Pi-1 |

ak |

bk |

SK |

PK |

|

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

1 |

1 |

0 |

|

0 |

1 |

0 |

1 |

0 |

|

0 |

1 |

1 |

0 |

1 |

|

1 |

0 |

0 |

1 |

0 |

|

1 |

0 |

1 |

0 |

1 |

|

1 |

1 |

0 |

0 |

1 |

|

1 |

1 |

1 |

1 |

1 |

Рис. 2.17

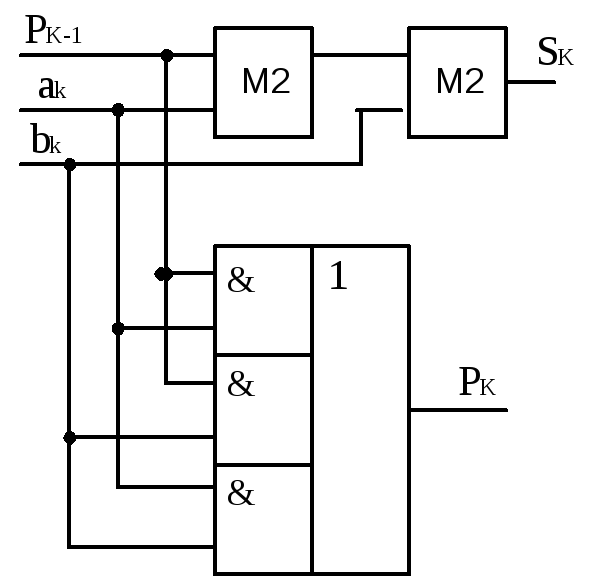

Рис.2.18

Для получения алгебраических выражений выходных функций сумматора приведены их карты Карно(рисунках 2.17, 2.18), анализ которых показывает, что функция поразрядного суммирования SK не минимизируется, а функция переноса PK может быть упрощена путем склеивания соседних клеток:

![]() (2.10)

(2.10)

или

![]() (2.11)

(2.11)

![]() (2.12)

(2.12)

Итоговое выражение для функции SK называется суммой по модулю 2 для трех переменных ( напомним, что сумма по модулю два для двух переменных адекватна функции “исключительное или” и обозначается как М2)

Выражение 2.12 отражает закон функционирования так называемого мажоритарного элемента, работающего по принципу два из трех: выходной сигнал истинен, если истинны по крайней мере два из и трех входных сигнала, что эффективно используется при резервировании устройства передачи цифровой информации.

Вариант реализации одноразрядного сумматора с использованием схем М2 и схемы 3-2И-ИЛИ показан на рисунке 2.19

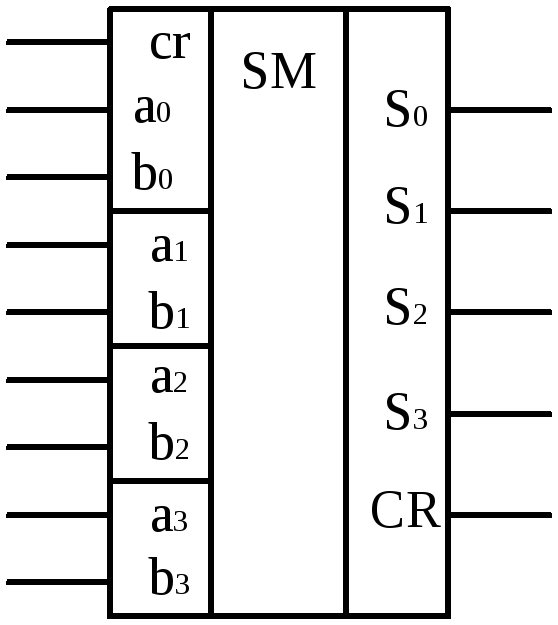

Рис.2.19 Рис.2.20

Многоразрядный сумматор состоит из нескольких одноразрядных сумматоров (условно изображен на рисунке 2.20 применительно к четырехразрядному сумматору). Входными сигналами здесь являются сигнал переноса “cr” от предыдущего сумматора ( или другой внешний сигнал), а также сигналы от одноименных разрядов двоичных чисел А и В. Результат сложения выделяется на выходе в виде многоразрядного слова CRS3S2S1S0 с разрядностью на единицу большую разрядности входных чисел. В свою очередь путем каскадного включения сумматоров конечной разрядности можно построить сумматор еще большей разрядности. Так , например, чтобы осуществить суммирование двух восьмиразрядных чисел, необходимо иметь два четырехразрядных сумматор и выход переноса “CR” первого из них соединить со входом “сr” второго.

Рассмотренный сумматор называется последовательным, поскольку операция сложения в нем выполняется последовательно разряд за разрядом, начиная с младшего, что вызывает задержку выходного сигнала переноса. Существуют и параллельные сумматоры с более сложным построением , когда выходной перенос каждого разряда вырабатывается независимо от переноса соседнего младшего разряда, но при этом существенно уменьшается время задержки на выходе сумматора.

Помимо суммирования сумматоры находят применение и при реализации ряда других функциональных и арифметических задач. В числе их преобразование двоично-десятичного кода в двоичный и обратно, компараторы (схемы сравнения чисел) и др. Покажем это на следующих примерах

1. Преобразователь двухразрядного двоично-десятичного кода в двоичный

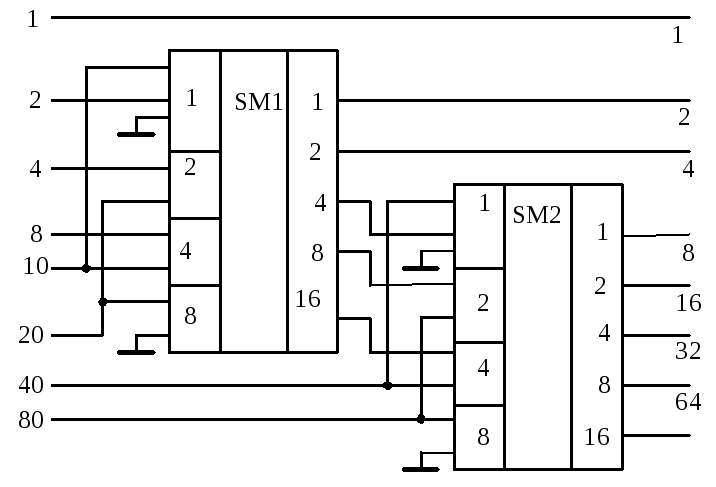

Схема этого преобразователя, состоящая из двух четырехразрядных сумматоров, изображена на рисунке 2.21

Рис.2.21

Вспомним, что в двоично-десятичной системе каждая десятичная цифра представляется двоичным эквивалентом. Например, двухразрядное десятичное число (его максимальное значение равно 99) запишется в виде двух байтов (тетрад) с четырьмя двоичными разрядами в каждом разряде: X2X1=x7x6x5x4 x3x2x1x0=x780+ x640+ x520+ x410+ x38+ x24+ x12+ x01 = x72310+ x62210+ x52110+ x420100+ x323+ x222+x121+ x020 где x7…..x0 принимают значения нуль или единица.. Двоичный же эквивалент числа будет иметь на один разряд меньше, то есть X2X1=y6y5y4y3y2y1y0= y626+ y525+ e424+ y323+ y222+ y121+ y020, где также y6……y0 равны нулю или единице.

Для перехода от двоично-десятичного представления числа к его двоичному эквиваленту заметим, что 80=26+24, 40=25+23, 20=24+22, 10=23+21, то есть все эти числа могут быть выражены через степени числа два. Легко видеть, что младший разряд (20) преобразуемых кодов совпадает. Другие же разряды двоичного кода получаются в результате суммирования одноименных двоичных разрядов из которых состоят числа 80, 40, 20, 10. Этот принцип и отражен в схеме рисунка 2.21.

2. Компаратор

Компаратор- это цифровое устройство, предназначенное для сравнения чисел, представленных в виде двоичных кодов. Здесь возможны следующие ситуации:

а) Двоичные числа А и В одинаковы.

Возьмем инверсию

от всех разрядов числа В, то есть создадим

новое число С=![]() ,

и просуммируем А и В. На всех выходах

сумматора, кроме выхода переноса,

окажутся единичные значения, что

позволяет установить равенство чисел.

,

и просуммируем А и В. На всех выходах

сумматора, кроме выхода переноса,

окажутся единичные значения, что

позволяет установить равенство чисел.

б) Число А>B

Сумма числа А и инверсии числа В вызовет на всех выходах сумматора появление единичных значений

в) Число А<В

Для установления этого неравенства достаточно убедиться, что не выполняются пункты а и б.

В заключение приведем примеры нескольких типов сумматоров: К155ИМ1- одноразрядный , К155ИМ2- двухразрядный , К564ИМ1- четырехразрядный двоичные сумматоры.

2.4.3 Контрольные вопросы к разделу 2.4

-

Изложите этапы синтеза комбинационных логических устройств

-

Что такое кодирующее устройство? Назовите известные типы кодирующих устройств

-

Какие функции выполняют дешифратор, шифратор, мультиплексор, демультиплексор?

4. Как осуществить повышение разрядности дешифрирующего устройства? Мультиплексора?

5. Поясните принцип построения преобразователя произвольного кода с помощью пары декодер-кодер.

6. Какие функции выполняют полусумматор, полный сумматор?

7. Поясните принцип построения много разрядного сумматора.

8. Поясните принцип построения преобразователя двоично-десятичного кода в двоичный.

9. Что такое компаратор? Поясните принцип его построения на основе сумматора.