Микроконтроллеры AVR

.pdfданных или устройств ввода/вывода, запрет/разрешение прерываний производится через этот бит, иначе – через специализированные команды запрета/разрешения прерываний. В некоторых процессорах прерывания по умолчанию (после рестарта) разрешены, в других (в том числе – в AVR) – запрещены.

-Индивидуальное маскирование прерываний – запрещает прерывания от определенного источника. Каждому источнику прерываний соответствует свой флаг маскирования. В некоторых процессорах эти флаги группируются в специальные регистры масок, в других (в том числе – в AVR) – "разбросаны" по различным регистрам управления периферией.

-Событие, вызывающее прерывание может быть кратковременным (например

– фронт логического сигнала). Для того, чтобы не потерять информацию о таком событии, если оно произошло в то время, когда прерывание было запрещено, существуют флаги прерываний. Каждому источнику прерывания соответствует свой флаг, который устанавливается при возникновении события. Сброс флага прерывания происходит при вызове подпрограммы его обслуживания. Как правило, флаги прерываний могут устанавливаться и сбрасываться программно, что позволяет имитировать те или иные прерывания, например, для целей отладки, либо отменять обработку каких-либо событий. В микроконтроллерах AVR возможно только сбрасывать флаги прерываний, причем, для сброса необходимо записать в соответствующий бит единицу. Аналогично флагам маскирования, флаги прерывания могут группироваться в специальные регистры, либо (в том числе – в AVR) могут быть разбросаны по различным регистрам.

-Приоритет прерываний определяет очередность, в которой будут обслуживаться два и более ожидающих обслуживания незамаскированных прерывания от разных источников. В некоторых процессорах приоритет может быть изменен программно. В AVR приоритет жестко фиксирован – чем меньше номер вектора прерывания, тем выше приоритет соответствующего ему источника: самый высокий приоритет – у внешнего прерывания INT0 (вектор №2) самый низкий – у прерывания от аналогового компаратора (вектор №11). (Обращение к вектору №1 происходит при рестарте микроконтроллера; этот вектор содержит команду перехода на начало основной программы).

-Для того, чтобы немедленно после начала одной подпрограммы обработки прерывания она не была прервана другим прерыванием, либо не возникла рекурсия прерывания сигнал прерывания может присутствовать постоянно (если, например, прерывание формируется при наличии на входе заданного уровня), при вызове обработчика прерывания автоматически производится глобальный запрет прерываний. В конце обработчика прерывания вместо команды ret используется команда reti, которая не только возвращает управление прерванной программе, но и выполняет глобальное разрешение прерываний.

31

Рассмотрим пример проектирования программы с использованием прерываний. Задача: для управления некоторым устройством требуется сформировать три периодических логических сигнала в соответствии с рисунком 6. Временные параметры сигналов приведены в таблице 4. Задача должна быть решена с помощью микроконтроллера At90S2313 с тактовой частотой 8МГц.

|

|

A |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tA |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

t |

|

|

B |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

C |

|

|

tB |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

t |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tC |

|

|

C |

|

|

|

|

|

|

|

|

|

t |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

Рисунок 6. Управляющие логические сигналы A, B и C |

||||||||||||||||||||||

Таблица 4. Временные параметры формируемых сигналов |

|

|

|||||||||||||||||||||

Параметр |

|

|

|

|

|

|

|

|

|

|

|

|

|

Обозн. |

Вариант I |

Вариант II |

Вариант III |

||||||

Задержка импульса A от начала периода |

|

tA |

0 мкс |

0 мкс |

0 с |

||||||||||||||||||

Длительность импульса А |

|

|

|

|

τA |

256 мкс |

200 мкс |

1 с |

|||||||||||||||

Задержка импульса B от начала периода |

|

tB |

256 мкс |

200 мкс |

1 с |

||||||||||||||||||

Длительность импульса B |

|

|

|

|

τB |

256 мкс |

200 мкс |

1 с |

|||||||||||||||

Задержка импульса C от начала периода |

|

tC |

512 мкс |

400 мкс |

2 с |

||||||||||||||||||

Длительность импульса C |

|

|

|

|

τC |

256 мкс |

200 мкс |

1 с |

|||||||||||||||

Для формирования временных последовательностей необходима временная база, в качестве которой используют таймеры. В состав At90S2313 входят два таймера. 8-разрядный таймер 0 способен формировать прерывания по переполнению (T0 Overflow Interrupt); 16-разрядный таймер 1 может формировать прерывания по переполнению (T1 Overflow Interrupt), по выходному сравнению (T1 Output Compare Interrupt) и по входу захвата (T1 Input Capture Interrupt). Очевидно, для наших целей может подойти одно из первых трех прерываний.

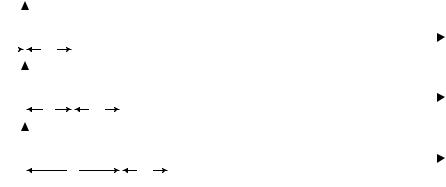

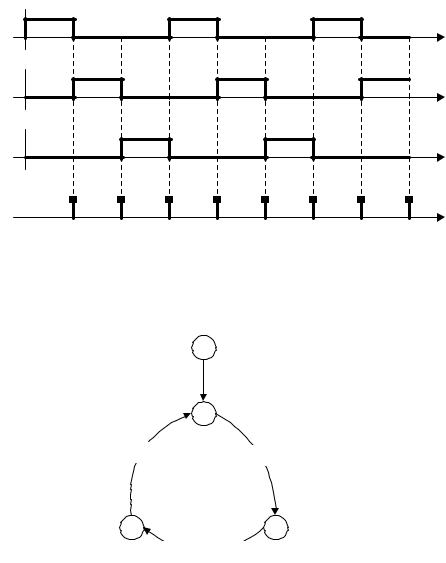

Период переполнения 8-разрядного таймера 0 определяется как TOVR 256/FT , где FT – частота синхронизации таймера. Частота синхронизации таймера может формироваться из тактовой частоты микроконтроллера FOSC с коэффициентом деления 1, 8, 64, 256, 1024. Для решения поставленной задачи в варианте I для формирования временной базы удобно использовать прерывание по переполнению таймера 0, с частотой синхронизации 1/8 от тактовой частоты микроконтроллера (1МГц). На рисунке 7 показана связь сигнала прерывания и формируемых временных последовательностей. На рисунке 8 в виде графа показан алгоритм работы программы.

32

A

t

B

t

C

t

Прерывания

t

Рисунок 7. Прерывание по переполнению таймера 0 и формируемые временные последовательности.

Инициализация

A=1

B=0

C=0

прерывание прерывание

A=0 |

A=0 |

|

B=1 |

||

B=0 |

||

C=0 |

||

C=1 |

||

прерывание |

Рисунок 8. Алгоритм программы формирования временных последовательностей.

Ниже приводится исходный текст программы, формирующей временные диаграммы согласно рисункам 6-8. В качестве выхода A используется PB.0, в качестве B – PB.1, в качестве C – PB.2. В разделе инициализации эти выводы микроконтроллера настраиваются в качестве выходов. Там же таймер 0 настраивается на синхронизацию с частотой 1/8 от тактовой и разрешается прерывание по его переполнению. Основная программа представляет собой пустой цикл. Временная диаграмма полностью реализуется в обработчике прерывания по переполнению таймера 0.

Микроконтроллер с этой программой фактически реализует простейший автомат Мура. Естественно, на базе микроконтроллеров можно реализовывать гораздо более сложные цифровые автоматы.

.INCLUDE "..\appnotes\2313def.inc" ;подключение файла со

.EQU A_LINE = |

0 |

;спецификацией регистров ввода/вывода |

;линия PORTB, соответствующая сигналу A |

||

.EQU B_LINE = |

1 |

;линия PORTB, соответствующая сигналу B |

33

.EQU C_LINE = 2 |

;линия PORTB, соответствующая сигналу C |

.DSEG

.ORG 0xc0

stack: .BYTE 0x10 ;область стека

.EQU sp_ini = stack+0x0f

.CSEG

;========= Таблица векторов прерываний ============================

.ORG 0x00

rjmp |

RESET |

;вектор прерывания RESET |

.ORG 0x06 |

OVR0_isr |

;вектор прерывания по переполнению Timer0 |

rjmp |

||

;========= Основная программа ===================================== |

||

RESET: |

|

;инициализация указателя стека |

ldi r16,sp_ini |

||

out SPL,r16 |

|

|

sbi PORTB,A_LINE |

;установить A в 1 |

|

ldi r16,0x07 |

;разрешить PB.0, PB.1, PB.2 как выходы |

|

out DDRB,r16 |

|

|

clr r16 |

|

;занести 0 в счетчик Timer0 |

out TCNT0,r16 |

|

|

ldi r16,0x02 |

;частота синхронизации Timer0 = Fosc/8 |

|

out TCCR0,r16 |

|

|

ldi r16,0x02 |

;разрешить прерывание по переполнению Timer0 |

|

out TIMSK,r16 |

||

sei |

|

;глобальное разрешение прерываний |

rjmp PC |

|

;пустой цикл (ожидание прерывания) |

;========== Обработчик прерывания по переполнению Timer0 ==========

OVR0_isr:

in r16,SREG ;сохранение в стеке регистра статуса push r16

sbis PORTB,A_LINE rjmp OVR0_m1

;1-е состояние: A==1, B==0, C==0 cbi PORTB,A_LINE ;A=0

sbi PORTB,B_LINE ;B=1 rjmp OVR0_end

OVR0_m1:

sbis PORTB,B_LINE rjmp OVR0_m2

;2-е состояние: A==0, B==1, C==0 cbi PORTB,B_LINE ;B=0

sbi PORTB,C_LINE ;C=1 rjmp OVR0_end

OVR0_m2: ;3-е состояние: A==0, B==0, C==1 cbi PORTB,C_LINE ;C=0

sbi PORTB,A_LINE ;A=1 OVR0_end:

pop r16 ;восстановление из стека регистра статуса out SREG,r16

reti ;конец обработчика прерывания

34

Для значений времен из варианта II можно модернизировать предыдущую программу, уменьшив период переполнения таймера 0. Для этого, в обработчик прерывания сразу после сохранения регистра статуса нужно добавить следующий фрагмент:

ldi |

r16,57 |

;занести 57 в счетчик Timer0 |

out |

TCNT0,r16 |

|

Врезультате, переполнение таймера 0 будет происходить не каждые 256, а каждые 200 его тактов синхронизации, т.е., 200мкс. (1 такт синхронизации таймера 0 в данном случае равен восьми тактам синхронизации микроконтроллера; на передачу управления обработчику и выполнение команд сохранения регистра SREG, и занесения в счетчик таймера 0 нового значения уходит, примерно, 16 процессорных тактов, или 2 такта синхронизации таймера 0, поэтому, в таймер 0 заносится значение 57, а не 55, как можно было бы ожидать).

Вварианте III используются значительно бόльшие временные интервалы. Можно было бы применить 16-разрядный таймер 1 аналогично таймеру 0 в варианте II (при частоте его синхронизацииFT FOSC /1024 8МГц/1024 период

переполнения составит TOVR 65536/FT 8.3с). Но воспользуемся этой задачей, чтобы показать возможность программного наращивания разрядности таймеров. Установим тактовую частоту таймера 0 FT FOSC /256. Одной секунде будут соответствовать 31250 тактов синхронизации таймера, или 122 цикла переполнения плюс 18 тактов таймера. Нам понадобится глобальная переменная Counter для хранения числа переполнений. Текст программы приводится ниже.

.include "..\Appnotes\2313def.inc"

.EQU NTau = 122

.EQU NRem = 18

.EQU A_LINE = 0

.EQU B_LINE = 1

.EQU C_LINE = 2

.DEF Counter = r17

.DSEG

.ORG 0xc0

stack: .BYTE 0x10

;число переполнений Timer0, соответствующее 1c ;число дополнительных тактов Timer0

;линия PORTB, соответствующая сигналу A ;линия PORTB, соответствующая сигналу B ;линия PORTB, соответствующая сигналу C

;счетчик переполнений

;область стека

.EQU sp_ini = stack+0x0f

.CSEG

;========= Таблица векторов прерываний ============================

.ORG 0x00

rjmp |

RESET |

;вектор прерывания RESET |

.ORG 0x06 |

OVR0_isr |

;вектор прерывания по переполнению Timer0 |

rjmp |

||

;========= Основная программа ===================================== |

||

RESET: |

|

;инициализация указателя стека |

ldi r16,sp_ini |

||

35

out SPL,r16 |

|

sbi PORTB,A_LINE |

;установить A в 1 |

ldi r16,0x07 |

;разрешить PB.0, PB.1, PB.2 как выходы |

out DDRB,r16 |

|

clr r16 |

;занести 0 в счетчик Timer0 |

out TCNT0,r16 |

;частота синхронизации Timer0 = Fosc/256 |

ldi r16,0x04 |

|

out TCCR0,r16 |

;разрешить прерывание по переполнению Timer0 |

ldi r16,0x02 |

|

out TIMSK,r16 |

|

clr Counter |

;обнулить счетчик переполнений |

sei |

;глобальное разрешение прерываний |

rjmp PC |

;пустой цикл (ожидание прерывания) |

;========== Обработчик прерывания по переполнению Timer0 ==========

OVR0_isr:

in r16,SREG ;сохранение в стеке регистра статуса push r16

inc Counter |

;увеличить счетчик переполнений |

cpi Counter,NTau |

;если Counter<NTau, завершить обработчик |

brlo OVR0_end |

|

brne OVR0_0 |

;если Counter>NTau, переключить выходы |

ldi r16,256-NRem ;если Counter==NTau, настроить переполнение

out TCNT0,r16 |

;через NRem тактов Timer0 |

rjmp OVR0_end |

|

OVR0_0:

sbis PORTB,A_LINE rjmp OVR0_m1

;1-е состояние: A==1, B==0, C==0 cbi PORTB,A_LINE ;A=0

sbi PORTB,B_LINE ;B=1 rjmp OVR0_end

OVR0_m1:

sbis PORTB,B_LINE rjmp OVR0_m2

;2-е состояние: A==0, B==1, C==0 cbi PORTB,B_LINE ;B=0

sbi PORTB,C_LINE ;C=1 rjmp OVR0_end

OVR0_m2: ;3-е состояние: A==0, B==0, C==1 cbi PORTB,C_LINE ;C=0

sbi PORTB,A_LINE ;A=1 OVR0_end:

pop r16 ;восстановление из стека регистра статуса out SREG,r16

reti ;конец обработчика прерывания

Задания:

1.Настройте Таймер 0 на синхронизацию с заданной частотой FCLK0, формируемой из тактовой частоты микроконтроллера FOSC. Обработчик прерывания по переполнению Таймера 0 должен формировать два периодических сигнала со скважностью S=2 и заданными периодами T (см. таблицу 5).

36

2.Настройте Таймер 1 на формирование прерывания от выходного сравнения и синхронизацию с заданной частотой FCLK1, формируемой из тактовой частоты микроконтроллера FOSC. Обработчик прерывания от выходного сравнения должен обеспечить формирование на выходе OC1 сигнала со скважностью S=4 и периодом T (см. таблицу 5).

Таблица 5. Исходные данные для заданий 1 и 2

Вариант |

Данные для задания 1 |

Данные для задания 2 |

|||

|

FCLK0 |

T для PB.3 |

T для PB.2 |

FCLK1 |

T для OC1 |

1 |

FOSC |

FOSC/256 |

FOSC/2560 |

FOSC/64 |

FOSC/6400 |

2 |

FOSC/8 |

FOSC/16384 |

FOSC/2048 |

FOSC/8 |

FOSC/20000 |

3 |

FOSC/64 |

FOSC/16384 |

FOSC/32768 |

FOSC |

FOSC/8000 |

4 |

FOSC/256 |

FOSC/262144 |

FOSC/65536 |

FOSC/8 |

FOSC/8000 |

5 |

FOSC/1024 |

FOSC/262144 |

FOSC/1048576 |

FOSC/64 |

FOSC/25600 |

3.Настройте Таймер 1 на работу в режиме 10-разрядного ШИМ с частотой синхронизации равной тактовой частоте микроконтроллера FOSC. Обработчик прерывания от выходного сравнения должен обеспечивать линейное изменение скважности ШИМ-сигнала.

4.Разработайте программу, которая с помощью периодического прерывания реализует динамическую индикацию для схемы на рисунке 5 – отображает в 16-ричном виде значение 8-разрядной переменной.

Контрольные вопросы и задания:

1.Способы организации реакции процессора на внешние события.

2.Механизм обслуживания прерывания.

3.Особенности подпрограмм обработки прерываний.

4.Приоритеты прерываний, маскирование прерываний, флаги прерываний.

5.Формирование циклических временных последовательностей с помощью микроконтроллеров.

6.Программное наращивание разрядности аппаратных таймеров.

7.Реализация автоматов Мура и Милли с помощью микроконтроллеров.

Приложение 1. Флаги регистра состояния процессора SREG

Бит |

Флаг |

Название |

Назначение |

0 |

C |

Carry flag |

Флаг переноса |

1 |

Z |

Zero flag |

Флаг нулевого результата |

2 |

N |

Negative flag |

Флаг отрицательного результата |

3 |

V |

Two’s complement oVerflow indicator |

Флаг переполнения |

4 |

S |

N V |

Флаг знака |

5 |

H |

Half Carry flag |

Флаг полупереноса |

6 |

T |

Transfer bit |

Пересылочный бит |

7 |

I |

Global Interrupt enable/disable flag |

Флаг глобального |

|

|

|

разрешения/запрета прерываний |

37

Приложение 2. Режимы адресации микроконтроллера At90S2313

Адресация |

Описание |

|

|

|

|

|

|

|

|

|

|

|

|

|

||

Прямая |

Операнд содержится в |

15 |

|

|

|

|

5 4 |

|

0 |

Регистровый |

||||||

регистровая |

регистре с номером d |

|

|

|

|

|

|

|

|

|

|

|

файл |

|||

|

OP |

|

|

|

d |

|

|

|

||||||||

адресация с |

(Rd) |

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

0 |

||||

одним |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

регистром |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

d |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

31 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Прямая |

Операнды содержатся в |

15 |

10 9 |

|

|

5 4 |

|

0 |

Регистровый |

|||||||

регистровая |

регистрах с номерами d |

|

|

|

|

|

|

|

|

|

|

|

файл |

|||

|

OP |

|

r |

|

d |

|

|

|

||||||||

адресация с |

(Rd) и r (Rr). Результат |

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

0 |

||||

двумя |

сохраняется в регистре |

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

регистрами |

d (Rd) |

|

|

|

|

|

|

|

|

|

|

|

|

d |

||

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

r |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

31 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Прямая |

Адрес операнда в |

15 |

|

|

|

|

5 |

|

0 |

Память устройств |

||||||

адресация |

пространстве устройств |

|

|

|

|

|

|

|

|

|

|

ввода/вывода |

||||

|

OP |

|

n |

|

P |

|

|

|||||||||

регистра |

ввода/вывода |

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

0 |

||||

ввода/вывода |

содержится в шести |

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

битах слова команды. |

|

|

|

|

|

|

|

|

|

|

|

|

P |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

Поле n обозначает |

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

адрес регистра- |

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

приемника или |

|

|

|

|

|

|

|

|

|

|

|

|

63 |

||

|

источника |

|

|

|

|

|

|

|

|

|

|

|

|

|

||

Прямая |

Адрес приемника или |

31 |

|

|

|

|

20 19 16 |

|

|

|

|

|||||

адресация |

источника в |

|

|

|

|

|

|

|

|

|

|

|

|

|

Память |

|

|

|

|

OP |

|

|

|

r/d |

|

|

|

||||||

памяти |

пространстве памяти |

|

|

|

|

|

|

|

|

|

данных |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

16 младших бит |

|

|

|

||||||||||

данных |

данных содержится в |

|

|

|

|

|

|

|

0x00 |

|||||||

|

|

|

|

|

|

|

||||||||||

|

16 младших битах 32- |

|

|

15 |

|

|

|

|

|

|

|

0 |

|

|

|

|

|

разрядного кода |

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

команды |

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0xDF |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

Косвенная |

Адрес операнда |

15 |

|

|

|

|

|

|

|

0 |

|

|

Память |

|||

адресация |

содержится в регистре |

|

|

|

|

|

|

|

|

|

|

|

|

данных |

||

|

|

Регистр X, Y или Z |

|

|

|

|||||||||||

|

X, Y или Z |

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0x00 |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0xDF

38

Приложение 2. Режимы адресации микроконтроллера At90S2313 (продолжение)

Адресация |

Описание |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Косвенная |

Адрес операнда |

15 |

|

|

|

|

|

|

|

0 |

|

|

|

|

|

Память |

||||||||||||||

адресация со |

вычисляется как |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

данных |

|||||

|

|

|

Регистр Y или Z |

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

смещением |

сумма содержимого |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0x00 |

||

|

регистра Y или Z с |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

+ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

адресом, |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

содержащемуся в 6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

битах кода команды |

15 |

|

11 10 6 5 |

|

|

0 |

|

|

|

|

|

|

|

|

|

|

0xDF |

||||||||||||

|

|

|

|

|

OP |

|

|

|

r |

|

|

|

a |

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

Косвенная |

Содержимое регистра |

15 |

|

|

|

|

|

|

|

0 |

|

|

|

|

Память |

|||||||||||||||

адресация с |

X, Y или Z |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

данных |

|||||

|

|

|

Регистр X, Y или Z |

|

|

|

|

|||||||||||||||||||||||

пре- |

уменьшается на |

|

|

|

|

|

|

|

||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0x00 |

||

декрементом |

единицу. Адресом |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

+ |

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

операнда является |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

уменьшенное |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

содержимое |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

-1 |

|

|

|

|

|

|

|

|

|

|

|

||||

|

соответствующего |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0xDF |

|||||

|

регистра |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Косвенная |

Регистр X,Y или Z |

15 |

|

|

|

|

|

|

|

0 |

|

|

|

|

Память |

|||||||||||||||

адресация с |

увеличивается на |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

данных |

|||||

|

|

|

Регистр X, Y или Z |

|

|

|

|

|||||||||||||||||||||||

пост- |

единицу после |

|

|

|

|

|

|

|

||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0x00 |

||

инкрементом |

выполнения команды. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

+ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

Адресом операнда |

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

является содержимое |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

соответствующего |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

регистра-указателя до |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0xDF |

|

инкрементирования |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Адресация |

Адрес байта в памяти |

15 |

|

|

|

|

|

|

|

1 0 |

|

|

|

|

|

Память |

||||||||||||||

констант с |

программ задаётся |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

программ |

|||||

|

|

|

|

Регистр Z |

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

использова- |

содержимым регистра |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0x00 |

||

нием |

Z. Его старшие 15 бит |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

команды |

определяют адрес |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

LPM |

слова, а младший бит |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

выбирает младший |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

байт (если равен 0) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0xDF |

|

или старший байт |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

слова (если равен 1) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

39

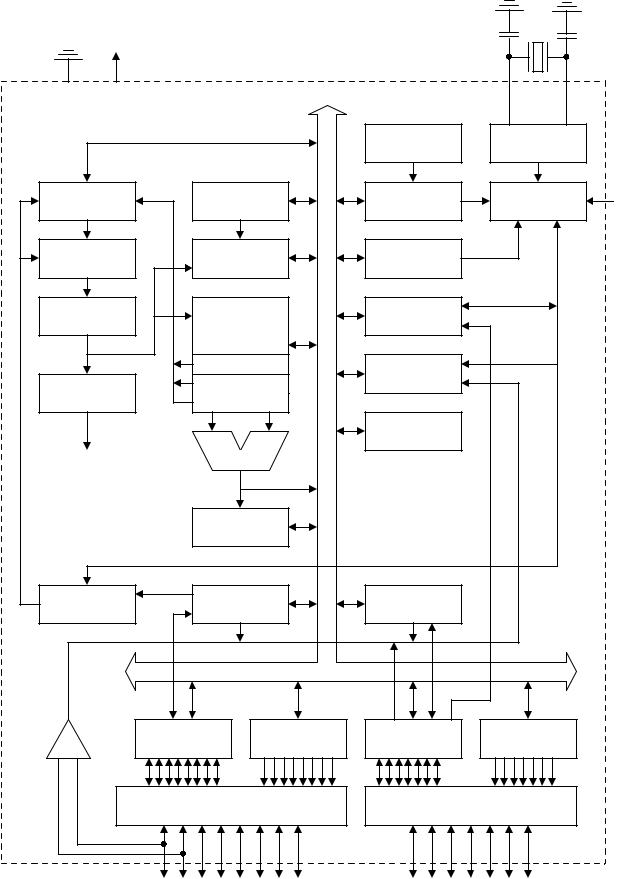

Приложение 3. Блок-схема микроконтроллера At90S2313 |

|

|||||

GND |

Vcc |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

XTAL1 |

XTAL2 |

|

|

|

8-РАЗРЯДНАЯ ШИНА ДАННЫХ |

|

|

|

|

|

|

|

ВНУТРЕННИЙ |

ГЕНЕРАТОР |

|

|

|

|

|

ГЕНЕРАТОР |

|

|

|

|

|

|

|

|

|

ПРОГРАММНЫЙ |

УКАЗАТЕЛЬ |

СТОРОЖЕВОЙ |

СИНХРОНИЗАЦИЯ |

/RESET |

||

|

||||||

СЧЕТЧИК |

СТЕКА |

ТАЙМЕР |

И УПРАВЛЕНИЕ |

|

||

FLASH-ПАМЯТЬ |

СТАТИЧЕСКОЕ |

РЕГИСТР MCU |

|

|

||

ПРОГРАММ |

|

ОЗУ |

CONTROL |

|

|

|

РЕГИСТР |

РЕГИСТРЫ |

ТАЙМЕРЫ- |

|

|

||

КОМАНДЫ |

СЧЕТЧИКИ |

|

|

|||

ОБЩЕГО |

|

|

||||

|

|

НАЗНАЧЕНИЯ |

|

|

|

|

|

|

|

X |

КОНТРОЛЛЕР |

|

|

ДЕШИФРАТОР |

|

Y |

ПРЕРЫВАНИЙ |

|

|

|

КОМАНДЫ |

|

Z |

|

|

|

|

|

|

|

|

EEPROM |

|

|

К ЛИНИЯМ |

|

АЛУ |

|

|

|

|

УПРАВЛЕНИЯ |

|

|

|

|

|

|

|

|

РЕГИСТР |

|

|

|

|

|

|

СТАТУСА |

|

|

|

|

УПРАВЛЕНИЕ |

|

|

|

|

|

|

ПРОГРАММИ- |

|

SPI |

UART |

|

|

|

РОВАНИЕМ |

|

|

|

|

|

|

+ - |

АНАЛОГОВЫЙ КОМПАРАТОР |

РЕГИСТР |

РЕГИСТР НАПР. |

РЕГИСТР |

РЕГИСТР НАПР. |

|

|

|

|

||||

|

|

ДАННЫХ PORTB |

ДАННЫХ PORTB |

ДАННЫХ PORTD |

ДАННЫХ PORTD |

|

|

|

ДРАЙВЕРЫ PORTB |

ДРАЙВЕРЫ PORTD |

|

||

40