Микроконтроллеры AVR

.pdfобозначается как -X, -Y или -Z), с пост-инкрементом указателя (второй операнд обозначается как X+, Y+ или Z+).

ld r5,x |

;загрузить в r5 содержимое ячейки памяти, чей адрес |

ld r10,x+ |

;хранится в регистре X |

;загрузить в r10 содержимое ячейки памяти, чей адрес |

|

st r2,-y |

;хранится в регистре X, после загрузки увеличить X на единицу |

;уменьшить содержимое регистра Y на единицу и загрузить |

|

|

;содержимое r2 в ячейку памяти, чей адрес хранится в регистре Y |

Команды LDD и STD работают только с регистрами Y и Z в качестве указателей, при этом реализуется косвенная адресация со смещением – адрес является суммой содержимого регистра-указателя и смещения, входящего в код команды. Значение смещения должно лежать в диапазоне от 0 до 63.

ldd r18,y+5 ;загрузить в r18 содержимое ячейки памяти, чей адрес ;равен сумме 5 и содержимого регистра Y

std Z+13,r15 ;сохранить содержимое r15 в ячейке, чей адрес равен ;сумме 13 и содержимого регистра Z

Команды LDS и STS реализуют прямую адресацию памяти данных – адрес ячейки памяти указывается непосредственно в коде команды.

lds r2,44 ;загрузить в r2 содержимое ячейки памяти данных с адресом 44 sts 0x20,r8 ;сохранить содержимое r8 в ячейке памяти данных с адресом 0x20

Единственным "мостом" от памяти программ к памяти данных служит команда LPM – она загружает в регистр r0 содержимое старшей или младшей половины ячейки памяти, чей адрес содержится в старших 15 разрядах регистра Z. Младший разряд Z при этом выбирает загрузку младшего (Z.0==0) или старшего (Z.0==1) байта из слова.

ldi r31,HIGH(0x0241*2)

ldi r30,LOW(0x0241*2) ;в регистр r0 заносится младший байт из ячейки

lpm |

;памяти программ с адресом 0x241 |

Две команды пересылок обеспечивают работу со стеком. Команда PUSH сохраняет в стеке содержимое регистра, после чего уменьшает значение указателя стека на единицу. Команда POP увеличивает значение указателя стека на единицу, после чего копирует данные из стека в регистр. Следующий фрагмент использует стек для обмена содержимого регистров r0 и r31 (о более "традиционном" применении стека см. в описании лабораторной работы №4).

ldi r16,0x70 ;начальная инициализация указателя стека адресом 0x70 out SPL,r16

push r0 ;содержимое r0 помещается в стек (ячейку 0x70), SPL<-0x6F mov r0,r31 ;содержимое r31 помещается в r0

pop r31 ;значение из вершины стека (ячейка 0x70) помещается

;в r31, SPL<-0x70

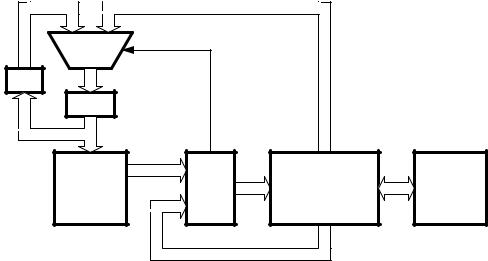

Предельно упрощенно процессор можно представить в виде дешифратора (DC), к выходу которого подключены исполнительные устройства, выполняющие те или иные действия. На входы дешифратора из ячеек памяти поступают коды команд. Адрес ячейки памяти, из которой берется текущая команда, содержится в специальном регистре, называемом программным счетчиком (англ.

11

Program Counter – PC). В том случае, если команды выполняются последовательно, одна за другой, адрес следующей исполняемой команды получается путем увеличения значения программного счетчика на размер исполняемой в данный момент команды (если все команды имеют длину в одно слово, увеличение счетчика ведется на единицу, как это показано на рисунке 1). Однако, исполняемая в данный момент команда может изменить адрес следующей исполняемой команды. Такого рода команды называются командами передачи управления. К ним относятся команды условных и безусловных переходов, вызова подпрограмм и возврата из подпрограмм.

При выполнении команды относительного безусловного перехода RJMP, адрес следующей исполняемой команды определяется значением смещения относительно текущего адреса. Под значение смещения в коде команды отведено 12 бит, что ограничивает радиус возможного перехода значениями от –2048 до +2047; для At90S2313, содержащего всего 1024 слова команд, RJMP перекрывает все адресное пространство. Кроме RJMP, At90S2313 поддерживает команду косвенного безусловного перехода IJMP (адрес следующей исполняемой команды определяется содержимым регистра Z). В других процессорах часто используются команды абсолютных переходов – в их коде содержится абсолютное значение адреса перехода.

Все команды передачи управления не изменяют значения флагов (исключение – RETI, которая устанавливает флаг глобального разрешения прерывания).

0 |

1 |

+1 |

|

|

PC |

Память |

DC |

Исполнит. |

Память |

|

программ |

устройства |

данных |

||

|

Рисунок 1. Процессор, как дешифратор команд

На языке Ассемблера во всех командах относительных переходов адрес перехода может задаваться:

1.В виде имени метки. Например:

m: inc r0 ;цикл повторяется, пока

lsr r18 ;из r18 не будет выдвинут 0

brcs m |

; |

2. В виде абсолютного значения адреса

rjmp 0 ;безусловный переход на начало памяти программ

12

3. В виде смещения относительно текущего положения программного счетчика:

label: |

;цикл повторяется, пока |

|

inc |

r0 |

|

lsl |

r18 |

;из r18 не будет выдвинут 0 |

brcs PC-2 |

; |

|

rjmp PC |

;”бесконечный” цикл |

|

В первом и втором случаях компилятор вычисляет смещение от адреса команды перехода до адреса перехода и подставляет его в код команды. В процессе исполнения программы по смещению и текущему содержимому программного счетчика вычисляется абсолютный адрес перехода.

Система команд At90S2313 содержит более десятка команд условных переходов, анализирующих значение флагов слова состояния процессора SREG. Все эти команды начинаются с символов BR (от англ. branch – переход,

ветвление) – BREQ (BRanch if EQual – переход, если равно), BRNE (BRanch if Not Equal – переход, если не равно) и т.п. Так же как и RJMP, эти переходы являются относительными. Под смещение в их коде отводится 6 разрядов, так, что радиус возможных переходов составляет от –64 до +63 ячеек памяти программ.

Команда CPSE (ComPare and Skip if Equal – сравнить и пропустить, если равно) комбинирует сравнение с условным переходом: сравниваются значения двух регистров; если они не равны, следующая команда выполняется; если значения равны – следующая команда пропускается. Аналогичным образом (рисунок 2) работают еще четыре команды тестирования битов (таблица 1).

...

Команда n

Условие |

|

истинно? |

|

Нет |

Да |

Команда n+1 |

|

Команда n+2 |

|

Рисунок 2. Алгоритм работы команд условного выполнения следующей команды (команда n – команда условного выполнения)

13

Таблица 1. Команды условного выполнения следующей команды

Команда |

Описание |

CPSE R1, R2 |

Сравнить содержимое регистров R1 и R2 и пропустить следующую |

|

команду в случае их равенства |

SBRC R, k |

Пропустить следующую команду, если бит k в регистре общего назначения |

|

R сброшен |

SBRS R, k |

Пропустить следующую команду, если бит k в регистре общего назначения |

|

R установлен |

SBIC IOR, k |

Пропустить следующую команду, если бит k в регистре ввода/вывода IOR |

|

сброшен |

SBIS IOR, k |

Пропустить следующую команду, если бит k в регистре ввода/вывода IOR |

|

установлен |

Конструкцию вида

if(бит k регистра R установлен) действие1; else действие2;

где каждое из действий включает более чем одну команду, можно реализовать так:

sbic R,k rjmp m1

действие 1 rjmp m2 m1:

действие 1 m2:

…

Время исполнения всех команд условного перехода и условного выполнения составляет один такт синхронизации, если последовательность выполнения команд не изменяется (т.е., переход не происходит) и два такта синхронизации, если происходит передача управления. Команды безусловных переходов выполняются за два такта.

Задания:

1.Пронаблюдайте работу программы из примера 3. Измените программу таким образом, чтобы она: а) подсчитывала число чётных чисел, б) число чисел кратных четырём.

2.Пронаблюдайте работу программы из примера 4. Измените программу так, чтобы она могла обрабатывать массив произвольной длины (задаются только адреса начала и конца массива).

3.Пронаблюдайте работу программы из примера 5.

4.В тексте программы из примера 5 используйте для задания каждого элемента массива констант отдельную директиву DB. Прокомментируйте полученный результат.

5.Напишите программу, реализующую операцию умножения 4-разрядных чисел с помощью таблицы.

14

6.Модифицируйте программу из примера 6 таким образом, чтобы она определяла число нулей в двоичном представлении 8-разрядной переменной.

7.Напишите программу, которая вычисляет модуль разности 16-разрядных переменных r1:r0 и r3:r2.

Пример 2:

Программа инициализирует массив переменных в ОЗУ нулями. Демонстрируется организация циклов, использование индексной адресации ОЗУ.

.INCLUDE "..\appnotes\2313def.inc" ;подключение файла со

;спецификацией регистров ввода/вывода

.CSEG |

|

;сегмент кода |

|

rjmp Reset |

|

;вектор прерывания, вызываемого по сбросу микроконтроллера |

|

Reset: |

|

|

;начало программы |

clr XH |

|

;r27<-0x00 |

|

ldi XL,0x60 |

|

;r26<-0x60 |

|

ldi |

r16,10 |

|

;указатель X проинициализирован значением 0x0060 |

|

;загрузка в счетчик цикла r16 числа 10 |

||

clr |

r0 |

|

;r0<-0x00 |

cycle: |

X+,r0 |

|

;копирование содержимого r0 в ячейку ОЗУ, на которую |

st |

|

||

dec |

r16 |

|

;указывает X с последующим увеличением X на единицу |

|

;r16<-(r16-1) |

||

cpi r16,0x00 |

;сравнение r16 с нулем |

||

brne cycle |

|

;повторение цикла, если не 0 |

|

rjmp PC |

|

;бесконечный цикл |

|

Пример 3:

Программа подсчитывает число нечётных чисел в массиве байт. Используется команда условного выполнения (sbrc).

.INCLUDE "..\appnotes\2313def.inc" ;подключение файла со

.DSEG |

|

;спецификацией регистров ввода/вывода |

|

|

|

.ORG 0x60 |

|

|

arr: .BYTE 10 |

|

|

.CSEG |

;сегмент кода |

|

rjmp Reset |

;вектор прерывания, вызываемого по сбросу микроконтроллера |

|

Reset: |

XH,HIGH(arr) |

;начало программы |

ldi |

;указатель X проинициализирован значением |

|

ldi |

XL,LOW(arr) |

;адреса начала массива arr |

ldi |

r16,10 |

;загрузка в счетчик цикла r16 числа 10 |

clr |

r1 |

;r1<-0x00 |

cycle: |

r0,X+ |

;копирование в r0 содержимого ячейки ОЗУ, на которую |

ld |

||

sbrc r0,0 |

;указывает X с последующим увеличением X на единицу |

|

;пропустить следующий оператор, если бит 0 регистра |

||

inc |

r1 |

;r0 равен нулю |

;инкремент счетчика нечетных чисел |

||

dec |

r16 |

;r16<-(r16-1) |

cpi |

r16,0x00 |

;сравнение r16 с нулем |

brne |

cycle |

;повторение цикла, если не 0 |

rjmp PC |

;бесконечный цикл |

|

15

Пример 4:

Программа переупорядочивает массив: меняются местами нулевой и последний элементы, первый и предпоследний и т.д.

.INCLUDE "..\appnotes\2313def.inc" ;подключение файла со

;спецификацией регистров ввода/вывода

.DSEG

.ORG 0x60 arr: .BYTE 10

.CSEG |

;сегмент кода |

||

rjmp Reset |

;вектор прерывания, вызываемого по сбросу микроконтроллера |

||

Reset: |

XH,HIGH(arr) |

;начало программы |

|

ldi |

;указатель X проинициализирован значением |

||

ldi |

XL,LOW(arr) |

;адреса начала массива arr |

|

ldi |

YH,HIGH(arr+10) |

;указатель Y проинициализирован значением |

|

ldi YL,LOW(arr+10) |

;адреса следующего за последним элементом |

||

ldi |

r16,5 |

|

;массива arr |

;загрузка в счетчик цикла r16 числа 5 |

|||

cycle: |

r0,X |

;копирование в r0 содержимого ячейки ОЗУ, на которую |

|

ld |

|||

ld |

r1,-Y |

;указывает X |

|

;копирование в r1 содержимого ячейки ОЗУ, на которую |

|||

st |

Y,r0 |

;указывает Y с предварительным уменьшением Y на единицу |

|

;копирование r0 в ячейку ОЗУ, на которую указывает Y |

|||

st |

X+,r1 |

;копирование r1 в ячейку ОЗУ, на которую указывает X |

|

dec |

r16 |

;с последующим увеличением X на единицу |

|

;r16<-(r16-1) |

|||

cpi |

r16,0x00 |

;сравнение r16 с нулем |

|

brne |

cycle |

;повторение цикла, если не 0 |

|

rjmp PC |

;бесконечный цикл |

||

Пример 5:

Программа инициализирует массив в ОЗУ из массива констант, размещающегося во Flash-памяти программ. Демонстрируется использование косвенной адресации памяти программ; задание массива констант во Flashпамяти.

.INCLUDE "..\appnotes\2313def.inc" ;подключение файла со

;спецификацией регистров ввода/вывода

.DSEG

.ORG 0x60 arr: .BYTE 10

.CSEG |

;сегмент кода |

|

rjmp Reset |

;вектор прерывания, вызываемого по сбросу микроконтроллера |

|

Reset: |

|

;начало программы |

ldi XH,HIGH(arr) |

;указатель X проинициализирован значением |

|

ldi XL,LOW(arr) |

;адреса начала массива arr |

|

ldi ZH,HIGH(arr_const*2);указатель Z проинициализирован значением ldi ZL,LOW(arr_const*2) ;адреса начала массива констант arr_const ldi r16,10 ;загрузка в счетчик цикла r16 числа 10

cycle: lpm

adiw ZL,1

st |

X+,r0 |

;копирование r0 в ячейку ОЗУ, на которую указывает X |

dec |

r16 |

;с последующим увеличением X на единицу |

;r16<-(r16-1) |

||

cpi |

r16,0x00 |

;сравнение r16 с нулем |

brne |

cycle |

;повторение цикла, если не 0 |

rjmp PC |

;бесконечный цикл |

|

arr_const: .DB 0x01, 0x02, 0x03, 0x04, 0x05, 0x06, 0x07, 0x08, 0x09, 0x0A

Пример 6:

Программа производит подсчёт числа единиц в четырех младших разрядах регистра, пользуясь таблицей числа единиц в тетраде.

.INCLUDE "..\appnotes\2313def.inc" |

;подключение файла со |

|

.CSEG |

;сегмент кода |

;спецификацией регистров ввода/вывода |

|

||

rjmp Reset |

;вектор прерывания, вызываемого по сбросу микроконтроллера |

|

Reset: |

;начало программы |

|

|

;r1 содержит анализируемое число |

|

ldi ZH,HIGH(num_of_ones*2) |

;указатель Z проинициализирован значением |

|

ldi ZL,LOW(num_of_ones*2) |

;адреса начала массива констант num_of_ones |

|

clr r2

ldi r17,0x0F

and r17,r1 ;младшая тетрада анализируемого числа

add ZL,r17 ;вычисление адреса требуемого элемента массива adc ZL,r2 ;

lpm |

;копирование в r0 |

содержимого ячейки Flash, на |

rjmp PC |

;которую указывает Z |

|

;бесконечный цикл |

|

|

;таблица содержит число единиц в двоичном представлении чисел от 0 до 15 num_of_ones:

.DB 0, 1, 1, 2, 1, 2, 2, 3, 1, 2, 2, 3, 2, 3, 3, 4

Контрольные вопросы:

1.Назначение директив ассемблера ORG и DB.

2.Косвенная адресация, косвенная адресация с пост-инкрементом и предекрементом, косвенная адресация со смещением.

3.Команды пересылок между регистрами и памятью данных.

4.Команда пересылок между памятью программ и регистрами.

5.Почему в примере 5 указатель Z инициализируется числом arr_const*2?

6.Какие режимы адресации используются в командах LDI, MOV, ST X+,r0?

7.Архитектуры процессоров CISC и RISC.

8.Соотношение понятий CISC, RISC, гарвардской и фон-неймановской архитектуры.

9.Последовательное и конвейерное выполнение команд.

10.Проблемы, возникающие при конвейерном выполнении команд.

11.Программный счетчик: назначение, модификация значения при последовательном выполнении команд и при выполнении команд передачи управления.

17

12.Объясните, почему время выполнения команд условных переходов различно для случаев, когда передача управления происходит и не происходит.

13.Радиус действия команд перехода. Способ расширения радиуса действия. 14.Команды условного выполнения следующей команды. Способ их

применения.

15.Архитектуры процессоров с использованием регистра-аккумулятора и регистрового файла.

16.Ортогональная и неортогональная системы команд.

17.Основные черты архитектуры процессорного ядра микроконтроллеров

AVR.

Лабораторная работа №3.

Система команд AVR: логические команды и команды сдвигов

Цель работы: знакомство с логическими командами At90S2313 и командами сдвигов At90S2313.

Порядок выполнения работы (п.п. 1-3 выполняются во внеаудиторное время):

1.Ознакомьтесь с теоретической частью лабораторной работы.

2.Разработайте блок-схемы программ для заданий 1-7.

3.Подготовьтесь к ответу на контрольные вопросы 1-10.

4.Выполните задания.

5.Защитите лабораторную работу.

Логические команды At90S2313: побитовое И двух регистров (AND), побитовое И регистра и константы (ANDI), побитовое ИЛИ двух регистров (OR), побитовое ИЛИ регистра и константы (ORI), побитовое исключающее ИЛИ двух регистров (EOR), побитовая инверсия регистра (COM).

Все логические команды всегда сбрасывают флаг V и не изменяют значения флагов H и C (за исключением команды COM, которая всегда устанавливает C). Эти команды устанавливают флаг Z в случае получения нулевого результата и флаг N, если 7-й (знаковый) разряд результата равен единице. Поскольку эти команды сбрасывают в ноль флаг V, то флаг S, принимающий значение N V, будет дублировать значение флага N.

Команды побитового И и ИЛИ с константой позволяют использовать любые 8- разрядные константы (от 0 до 0xFF), но поддерживают только старшую половину регистрового файла (r16…r31).

Команды установки (SBR) и сброса (CBR) битов регистра на самом деле реализуются с помощью команд побитового И и ИЛИ с константой: команда SBR R,K преобразуется компилятором в команду ORI R,K, а команда CBR R,K – в команду ANDI R,(0xFF-K). Соответственно, ограничения на использование регистров для SBR и CBR те же, что и для ORI и ANDI.

18

Команда обнуления содержимого регистра CLR реализуется компилятором через команду исключающего ИЛИ регистра с самим собой.

Команда установки всех разрядов регистра в единицу SER реализуется компилятором через команду загрузки константы LDI R,0xFF. Она работает только со старшей половиной регистрового файла (r16…r31) и как все команды пересылок данных не изменяет состояния флагов.

Команда дополнения до двух (NEG) изменяет значение регистра на противоположное по знаку (R←0–R). Значения флагов изменяются так же, как при выполнении команды вычитания.

Команда проверки содержимого регистра на равенство нулю TST реализуется компилятором через команду поразрядного И регистра с самим собой (значение регистра при этом не изменяется, а флаг нулевого результата Z установится только при равенстве анализируемого регистра нулю).

Таблица 2. Команды сдвигов и перестановки тетрад

Команда |

Описание |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

LSL R |

Логический сдвиг влево. Все разряды |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

сдвигаются влево. Старший бит |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

C |

|

|

|

b7......................... |

|

|

b0 |

|

|

|

0 |

|

||||||

|

копируется во флаг C, в младший |

|

|

|

|

|

|

|

|

|

|||||||||

|

заносится ноль. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

LSR R |

Логический сдвиг вправо. Все разряды |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

сдвигаются вправо. Младший бит |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

|

|

|

b7......................... |

|

|

b0 |

|

|

|

C |

|

||||||

|

копируется во флаг C, в старший заносится |

|

|

|

|

|

|

|

|

|

|||||||||

|

ноль |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ROL R |

Вращение через флаг C влево. Все разряды |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

сдвигаются влево. Старший бит |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

C |

|

|

|

b7......................... |

|

|

b0 |

|

|

|

C |

|

||||||

|

копируется во флаг C, в младший |

|

|

|

|

|

|

|

|

|

|||||||||

|

заносится предыдущее значение флага C. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ROR R |

Вращение через флаг C вправо. Все |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

разряды сдвигаются вправо. Младший бит |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

C |

|

|

|

b7......................... |

|

|

b0 |

|

|

|

C |

|

||||||

|

копируется во флаг C, в старший заносится |

|

|

|

|

|

|

|

|

||||||||||

|

предыдущее значение флага C. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ASR R |

Арифметический сдвиг вправо. Все |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

разряды сдвигаются вправо. Младший бит |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

b7 |

|

|

b0 |

|

|

|

C |

|

||||||

|

копируется во флаг C. Старший бит |

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

сохраняет свое предыдущее значение. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SWAP R |

Команда SWAP меняет местами старшую |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

b7 |

b4b3 |

b0 |

|

|

|

|

|

|

|

|

||||||||

|

и младшую тетрады регистра. |

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

b3........ |

b0b7........ |

b4 |

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

В систему команд входят пять команд сдвигов, описанных в таблице 2. Каждая команда производит сдвиг на один разряд. Все команды помещают в флаг C значение выдвинутого бита, как это показано в таблице. Флаг Z устанавливается при равенстве результата нулю. Флаг N устанавливается при

19

наличии 1 в 7-м разряде результата (исключение – команда LSR всегда обнуляет флаг N). Флаг переполнения V принимает значение N C; поскольку флаг S всегда содержит значение N V, при операциях сдвига он будет дублировать флаг C.

В силу тождеств R<<1 R 2 R+R команды LSL R и ROL R реализуются компилятором через команды ADD R,R и ADC R,R, соответственно. Поэтому, эти команды сдвигов изменяют значение флага H. Остальные команды сдвигов флаг H не изменяют.

Еще одна пара команд обеспечивает работу с отдельными битами регистров общего назначения через флаг T. Команда BST копирует заданный бит заданного регистра во флаг T. Команда BLD копирует флаг T в заданный бит заданного регистра. Следующий фрагмент показывает копирование 0-го бита регистра r16 в 7-й бит регистра r17:

bst r16,0 bld r17,7

Задания:

1.Модифицируйте программу из примера 6 таким образом, чтобы она подсчитывала число единиц в 8-разрядной переменной (используйте команду SWAP).

2.Измените программу из примера 7 таким образом, чтобы она подсчитывала число нулей.

3.Измените программу из примера 7 таким образом, чтобы содержимое r1 после её работы не изменялось. При этом запрещается использовать резервное копирование r1 в память, другие регистры, стек.

4.Напишите программу, выполняющую логический сдвиг 16-разрядной переменной на 3 разряда а) влево, б) вправо.

5.Напишите программу, выполняющую вращение 16-разрядной переменной на 4 разряда а) влево, б) вправо.

6.Напишите программу, выполняющую зеркальную перестановку разрядов 8- разрядного регистра.

7.Напишите программу, выполняющую умножение двух 8-разрядных чисел без знака, используя команды сдвигов и сложения.

Пример 7:

Программа подсчитывает число единиц в двоичном представлении байта, используя команду логического сдвига.

.INCLUDE "..\appnotes\2313def.inc" ;подключение файла со

.CSEG |

;спецификацией регистров ввода/вывода |

;сегмент кода |

|

rjmp Reset |

;вектор прерывания, вызываемого по сбросу микроконтроллера |

Reset: |

;начало программы |

20