Контрольная работа 1 АПз-310 / Электроника Ч2

.pdf

201

ключается в состояние Q = 0. Во время действия третьего синхроимпульса J = 0; K = 0. Триггер не меняет своего состояния.

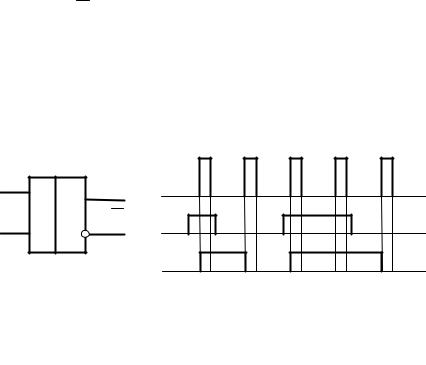

Счетный Т-триггер реализует только четвертую строку таблицы рис.31.3, а. Таким свойством обладает JK-триггер, когда его входы J = K = 1. При таком включении входов триггер переключается в момент среза каждого тактового импульса. Отсюда следует, что счетный триггер имеет один такто- вый вход, который обозначают символом «Т». Обозначение Т-триггера приве- дено на рис. 31.4, а. На рис.31.4, б приведены временные диаграммы, пояс- няющие его работу. Из диаграмм видно, что частота повторения импульсов на выходе Q триггера в два раза меньше частоты повторения импульсов на входе Т, т. е. Т-триггер делит частоту входных импульсов на 2. Счетные триггеры широко применяются в счетчиках, распределителях и делителях частоты.

D-триггер запоминает входную информацию в момент фронта синхроим- пульса и хранит ее до следующего тактового импульса. D-триггер может быть вы-

202

полнен на основе JK-триггера при включении на входе элемента "НЕ", обеспечи-

вающего условие J = K = D . Отсюда следует, что D-триггер имеет тактовый вход С и вход D. Его работа описывается второй и третьей строкой таблицы рис. 31.3, а, т. е. Qn+1 = D . Поэтому D-триггер является элементом памяти и находит широкое применение, в том числе в регистрах. Условное обозначение D-триггера и времен- ные диаграммы, поясняющие его работу, приведены на рис. 31.5.

В микросхемном исполнении триггеры выпускаются в составе многих серий цифровых интегральных микросхем. Для условного обозначения им присвоены следующие индексы:

RS-триггеры – ТР;

JK-триггеры – ТВ;

D-триггеры – ТМ.

Например, микросхема К555 ТР2 содержит 4 RS-триггера. Микросхе- мы К555 ТВ6 и К555 ТВ9 включают в свой состав по два JK триггера каж- дая. Микросхемы позволяют путем внешних коммутационных изменений получить схемы, выполняющие функции RS, D и Т-триггеров.

КОНТРОЛЬНЫЕ ВОПРОСЫ И ЗАДАЧИ

31.1. Перечислите основные признаки классификации триггеров. Как разделяются триггеры по функциональному назначению?

203

31.2.Чем отличаются статические входы триггеров от динамических?

31.3.Можно ли управлять RS триггером, воздействуя управляющим сигналом только на один вход?

31.4.Чем отличаются RS триггеры на элементах ИЛИ – НЕ от RS триггеров на элементах И – НЕ?

31.5.Приведите таблицу истинности RS триггера. Какая из строк таблицы определяет свойства триггера как память?

31.6.В чем состоит суть синхронизации триггера и для чего она применяется?

31.7.Чем отличается JK триггер от RS триггера?

31.8.Нарисуйте схемы Т и D триггеров, реализованных на базе JK триггеров. Проведите анализ их работы по графикам напряжений на входе и выходе.

31.9.На рис 31.6, а приведена схема синхронного двухступенчатого RS триггера. Проведите анализ работы этой схемы. В чем заключается достоинство такого триггера?

31.10.На рис. 31.6, б приведена схема синхронного двухступенчатого RS триггера

сперекрестными обратными связями. Какие функции выполняет такая схема?

ЛЕКЦИЯ 32. ПОСЛЕДОВАТЕЛЬНОСТНЫЕ УСТРОЙСТВА

В сложных электронных устройствах вместе с комбинационными схе- мами применяются и такие, у которых есть "память". Значения их выходных сигналов зависят не только от того, какие сигналы действуют в данный мо- мент времени на входе, но и от того, каково было внутреннее состояние схемы ранее. В качестве элементов памяти, как правило, используются триг-

204

геры. Схемы, содержащие и логические элементы, и элементы памяти, на-

зываются последовательностными.

1. СЧЕТЧИКИ ИМПУЛЬСОВ

Одной из наиболее распространенных операций в устройствах дис- кретной обработки информации является счет импульсов (таймеры, ЭСЧ, цифровые измерительные приборы, АЦП и т. п.). Эту операцию выполняют счетчики, которые по назначению делятся на простые (выполняющие опе- рацию суммирования и вычитания) и реверсивные.

Простые счетчики осуществляют переходы от предыдущего состояния к последующему только в одном направлении, т. е. могут или суммировать или вычитать импульсы. Реверсивные счетчики имеют переходы в двух на- правлениях – прямом и обратном.

Взависимости от системы счисления счетчики делятся на двоичные и десятичные. Синхронизация счета бывает двух типов – синхронная (по фронту импульса) и асинхронная (по импульсу).

Воснову построения счетчиков положено применение Т-триггеров.

Максимальное число, которое может быть записано в счетчике, равно

N = (2n − 1), где n – число разрядов счетчика. Каждый разряд двоичного счетчика представляет собой триггер.

Схема четырехразрядного счетчика на сумму приведена на рис. 32.1, а. На рис. 32.1, б приведены графики напряжений на входе Т и на выходах триггеров Q1 ÷ Q4, поясняющие принцип его работы. На схеме введены сле- дующие обозначения:

–"Т" – счетный вход счетчика,

–"Q1"÷"Q4 " – выходы разрядов,

205

– "УСТ" – установка состояния.

Связь между триггерами выполнена по прямым входам. Перед нача- лом счета все триггеры устанавливаются в нулевое состояние – Q1 = Q2 = Q3 = Q4 = 0. Для этого достаточно подать единичный потенциал по шине "УСТ". Счетные импульсы поступают на вход "Т" первого триггера и пере- ключают его срезом каждого импульса (график Q1 рис. 32.1, б). Срезом им- пульсов на выходе Q1 переключается триггер Т2 (график Q2 рис. 32.1, б). Триггеры Т3 и Т4 переключаются по аналогичному алгоритму.

Все состояния триггеров счетчика отражаются таблицей состояний 32.1. Нетрудно видеть, что состояния разрядов счетчика представляют собой запись двоичного числа импульсов, поступивших на его вход на данный момент. После записи максимального числа N = (2n − 1) счетчик автомати-

чески обнуляется, т. е. устанавливается исходное состояние: Q1 = Q2 = Q3 = Q4 = 0. Далее начинается новый цикл счета. При необходимости увеличить число N достаточно подключить к выходу счетчика дополнительные разря- ды (триггеры).

Аналогично суммирующему счетчику строится счетчик на вычитание. Схема такого счетчика приведена на рис. 32.1, в. В этой схеме связь между

206

триггерами выполнена по инверсным выходам, а шина "УСТ" объединяет установочные входы триггеров "S".

Перед началом счета все триггеры устанавливаются в состояние Q1 = Q2 = Q3 = Q4 = 1. С поступлением на вход Т счетных импульсов проис-

ходит изменение состояний триггеров на вычитание. Все состояния тригге- ров приведены в таблице 32.2. Таблица представляет собой двоичную за- пись линейно убывающих чисел.

Таблица 32.1

№ им- |

Q4 |

Q3 |

Q2 |

Q1 |

|

пульса |

|||||

|

|

|

|

||

|

|

|

|

|

|

0 |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

1 |

0 |

0 |

0 |

1 |

|

|

|

|

|

|

|

2 |

0 |

0 |

1 |

0 |

|

|

|

|

|

|

|

3 |

0 |

0 |

1 |

1 |

|

|

|

|

|

|

|

4 |

0 |

1 |

0 |

0 |

|

|

|

|

|

|

|

5 |

0 |

1 |

0 |

1 |

|

|

|

|

|

|

|

6 |

0 |

1 |

1 |

0 |

|

|

|

|

|

|

|

7 |

0 |

1 |

1 |

1 |

|

|

|

|

|

|

|

8 |

1 |

0 |

0 |

0 |

|

|

|

|

|

|

|

9 |

1 |

0 |

0 |

1 |

|

|

|

|

|

|

|

10 |

1 |

0 |

1 |

0 |

|

|

|

|

|

|

|

11 |

1 |

0 |

1 |

1 |

|

|

|

|

|

|

|

12 |

1 |

1 |

0 |

0 |

|

|

|

|

|

|

|

13 |

1 |

1 |

0 |

1 |

|

|

|

|

|

|

|

14 |

1 |

1 |

1 |

0 |

|

|

|

|

|

|

|

15 |

1 |

1 |

1 |

1 |

|

|

|

|

|

|

|

16 |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

№ |

Q4 |

Q3 |

Q2 |

Q1 |

|

ульса |

|||||

|

|

|

|

||

|

|

|

|

|

|

0 |

1 |

1 |

1 |

1 |

|

|

|

|

|

|

|

1 |

1 |

1 |

1 |

0 |

|

|

|

|

|

|

|

2 |

1 |

1 |

0 |

1 |

|

|

|

|

|

|

|

3 |

1 |

1 |

0 |

0 |

|

|

|

|

|

|

|

4 |

1 |

0 |

1 |

1 |

|

|

|

|

|

|

|

5 |

1 |

0 |

1 |

0 |

|

|

|

|

|

|

|

6 |

1 |

0 |

0 |

1 |

|

|

|

|

|

|

|

7 |

1 |

0 |

0 |

0 |

|

|

|

|

|

|

|

8 |

0 |

1 |

1 |

1 |

|

|

|

|

|

|

|

9 |

0 |

1 |

1 |

0 |

|

|

|

|

|

|

|

10 |

0 |

1 |

0 |

1 |

|

|

|

|

|

|

|

11 |

0 |

1 |

0 |

0 |

|

|

|

|

|

|

|

12 |

0 |

0 |

1 |

1 |

|

|

|

|

|

|

|

13 |

0 |

0 |

1 |

0 |

|

|

|

|

|

|

|

14 |

0 |

0 |

0 |

1 |

|

|

|

|

|

|

|

15 |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

16 |

1 |

1 |

1 |

1 |

|

|

|

|

|

|

207

Часто возникает необходимость в счетчиках, которые могли бы по- очередно выполнять сложение и вычитание поступающих импульсов. Такие счетчики называются реверсивными. Реверсивные счетчики снабжаются системой коммутации связей между триггерами (с прямых на инверсные и обратно), а также одним или двумя счетными входами.

В качестве примера рассмотрим реверсивные счетчики с двумя счет- ными входами, реализованные в микросхемах К555ИЕ6 и К555ИЕ7. Услов- ное графическое обозначение ИС К555ИЕ6 приведено на рис. 32.2, а. Ин- дексами С1 и С2 обозначены счетные входы счетчика. При прямом счете на входе С2 должно быть напряжение высокого уровня. Для обратного счета напряжение высокого уровня необходимо подать на вход С1. Входы D0 – D3 информационные. Они необходимы для предварительной установки счетчика. Информация с этих входов передается на выходы Q0 – Q3 при низком уровне напряжения на входе V . Для сброса информации достаточно подать низкий уровень напряжения на вход R .

В ряде случаев возникает необходимость вернуть счетчик в исходное состояние Q1 = Q2 = Q3 = Q4 = 0 после записи некоторого числа

M < N = (2n − 1). Для создания такого счетчика достаточно ввести в него цепь ОС. Например, декадные счетчики выполняются на основе четырех- разрядных двоичных счетчиков. Но счет необходимо выполнять от 0 до 9, т. е. после записи цифры 9 необходимо возвратить триггеры в исходное со- стояние. Значит, цепь ОС должна выделить двоичную комбинацию числа 10. Наиболее просто она может быть образована с использованием логиче- ского элемента "И" (рис. 32.2, б).

Промышленность выпускает счетчики в виде интегральных микросхем, в том числе двоичные (на сложение и вычитание), двоично-десятичные (дека- ды), реверсивные, с программируемым коэффициентом счета. Например,

208

К555 ИЕ6; ИЕ7 – двоично-десятичный и двоичный реверсивные четы- рехразрядные счетчики.

|

|

|

|

Q1 |

Q2 |

Q3 |

Q4 |

C1 |

СТ10 |

|

Q1 |

T |

|

|

|

C2 |

|

|

|

|

|

||

|

1 |

|

T T1 |

T T2 |

T T3 |

T T4 |

|

V |

|

Q2 |

|||||

D0 |

|

2 |

|

|

|

|

|

D1 |

|

4 |

Q3 |

R |

R |

R |

R |

D2 |

|

||||||

D3 |

|

8 |

Q4 |

|

|

|

|

|

|

|

|

|

|

& |

|

R |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

а) |

|

|

|

|

б) |

|

Рис. 32.2. Условное обозначение реверсивного счетчика а) и схема декадного счетчика б)

2. РЕГИСТРЫ

Регистрами называют функциональные узлы, предназначенные для хранения n-разрядных двоичных чисел (слов). Основными видами регистров являются параллельный и последовательный.

Схема четырехразрядного параллельного регистра приведена на рис. 32.3. В этой схеме четыре D триггера объединены по входам С. Входами ре- гистра являются входы D-триггеров. Выходы регистра могут иметь ключе- вую развязку посредством логических элементов "И".

209

В регистр информация поступает в виде параллельного кода по n про- водам. Входы обозначены по разрядам кодовой комбинации x1, x2 , x3 , x4 .

Одновременно на входы С всех триггеров подается логический сигнал "1" – "Запись". Все триггеры срабатывают по переднему фронту импульса С, при- нимая состояние входов. Для считывания информации достаточно на входы 1 всех логических элементов "И" подать уровень логической "1". Информа- ция присутствует на выходах Q1 = x1 ; Q2 = x2 ; Q3 = x3 ; Q4 = x4 в виде па-

раллельного кода на интервале длительности импульса "Считывание". Схема четырехразрядного последовательного (сдвигающего) регистра

приведена на рис. 32.4, а. На рис. 32.4, б приведены временные диаграммы, поясняющие его работу.

Для построения регистра применяются D-триггеры. Схема имеет один вход – "x" и выходы каждого разряда – Q1, Q2 , Q3 , Q4 . Тактовые входы всех триггеров объединены по шине "СС" – сигнал сдвига. На вход первого разряда регистра поступает цифровой сигнал записываемого числа (кодовая комбинация). На вход каждого следующего разряда регистра поступает сиг- нал с выхода предыдущего разряда. Работой схемы управляет тактовая по-

210

следовательность импульсов СС. Важно, чтобы период следования импуль- сов СС был равен длительности разряда кодовой комбинации.

Пусть перед записью все D-триггеры находятся в состоянии Q1 = Q2 = Q3 = Q4 = 0 . Пусть также на вход х последовательно во времени, по-

ступают разряды кодовой комбинации 1011 (диаграмма Х). С поступлением пер- вого импульса СС по его фронту в первый D-триггер записывается первый разряд кодовой комбинации – "1". Во все остальные D-триггеры регистра будет записан "0". Эта информация будет храниться до прихода следующего импульса СС.

К моменту поступления второго импульса СС на вход первого D-триггера воздействует второй разряд кодовой комбинации. Он равен "0". На вход второго D-триггера воздействует сигнал Q1 = 1. На вход третьего и четвертого D- триггеров воздействует "0". По фронту второго импульса СС эта информация и записывается в соответствующий триггер. Первый разряд кодовой комбинации сдвинулся во второй разряд регистра, а в первый разряд регистра записан вто- рой разряд кодовой комбинации. Далее процессы повторяются.

Каждый импульс СС продвигает записываемую информацию по раз- рядам регистра от входа к выходу. Поэтому последовательный регистр часто называют регистром сдвига. Фронтом четвертого импульса СС все разряды кодовой комбинации расположатся в разрядах регистра, как показано на рис. 32.4. б. В общем случае для записи n разрядов кодовой комбинации по- требуется п импульсов СС.

Поступивший на вход Х последовательный код может быть считан с выходов Q1 Q4 как параллельный, т. е. последовательный регистр позво-

ляет преобразовать последовательный код в параллельный. Информация, записанная в последовательном регистре, может быть считана с выхода старшего разряда в виде последовательного кода. Для этого достаточно по- дать n импульсов СС.