- •7. Система памяти

- •7.1. Базовые концепции

- •7.2. Быстродействие, объем и стоимость

- •7.3.1. Функция отображения

- •7.3.2. Алгоритмы замещения

- •7.3.3. Примеры технологий отображения

- •7.3.4. Организация кэша в коммерческих процессорах

- •7.4. Производительность

- •7.4.1. Чередование операций

- •7.4.2. Частота попаданий и накладные расходы при промахах

- •7.4.3. Кэши на микросхеме процессора

- •7.4.4. Другие способы увеличения быстродействия

- •7.5. Виртуальная память

- •7.5.1. Преобразование адресов

- •7.6. Требования к управлению памятью

7.5. Виртуальная память

В большинстве современных компьютерных систем физическая основная память не так велика, как используемое процессором адресное пространство. Например, адресное пространство процессора, генерирующего 32-разрядные адреса, имеет размер 4 Гбайт. Размер основной памяти типичного компьютера варьируется от нескольких сотен мегабайтов до гигабайта. Если программа не помещается в основную память, то те ее части, которые в данный момент не выполняются, хранятся во вторичном запоминающем устройстве, чаще всего на магнитном диске. Безусловно, перед выполнением необходимая часть программы должна быть перемещена в основную память. Если основная память заполнена, новый сегмент программы должен заменить какой-нибудь из старых сегментов. В современных компьютерах перемещение программы и данных между основной памятью и вторичными запоминающими устройствами выполняется операционной системой автоматически. При этом прикладному программисту не нужно беспокоиться об ограничениях, налагаемых доступным объемом основной памяти.

Технологии автоматического перемещения в основную память сегментов программ и данных, потребовавшихся для выполнения программы, называются технологиями управления виртуальной памятью программы, а в ходе их выполнения и процессор, ссылаются на пространство команд и данных, не зависимое от реального физического пространства основной памяти. Генерируемые процессором двоичные адреса команд и данных называются виртуальными или логическими адресами. Объединенными усилиями соответствующих аппаратных и программных компонентов они транслируются в реальные физические адреса. Если виртуальный адрес указывает на часть пространства программы или данных, расположенную в физической памяти, доступ к нему выполняется немедленно, но если этот адрес указывает не на основную память, соответствующий сегмент программы или данных сначала должен быть перемещен в основную память.

На рис. 7.14 проиллюстрирована типичная организация виртуальной памяти. Трансляцию виртуальных адресов в физические выполняет специальный аппаратный блок, называемый модулем управления памятью или же диспетчером памяти (Memory Management Unit, MMU). Когда нужные данные (или команды) отсутствуют в основной памяти, диспетчер перемещает их туда с диска. Для перемещения данных используется механизм ПДП.

Рис. 7.14. Организация виртуальной памяти

7.5.1. Преобразование адресов

Простейший метод преобразования виртуальных адресов в физические основывается на предположении, что все программы и данные состоят из сегментов фиксированной длины, называемых страницами, которые, в свою очередь, состоят из блоков слов, последовательно расположенных в памяти. Размер страницы обычно варьируется от 2 до 16 Кбайт. Страница является базовой единицей информации, перемещаемой между основной памятью и диском по требованию механизма преобразования адресов. Страницы не должны быть слишком маленькими, поскольку время доступа к магнитному диску (составляет несколько миллисекунд) намного больше времени доступа к основной памяти. Значительная часть этого времени уходит на поиск данных на диске. Найденные данные пересылаются со скоростью несколько мегабайт в секунду. С другой стороны, если страница слишком велика, большая ее часть, скорее всего, не будет использована, но место в основной памяти она, конечно же, будет занимать

Все это напоминает концепции кэш-памяти, рассмотренные в разделе 7.3. Кэш сглаживает разницу в быстродействии процессора и основной памяти, а механизм управления виртуальной памятью делает то же самое в отношении основной памяти и вторичного запоминающего устройства. Концептуально технологии управления виртуальной памятью и кэшем очень близки, а их различия связаны главным образом со спецификой реализации.

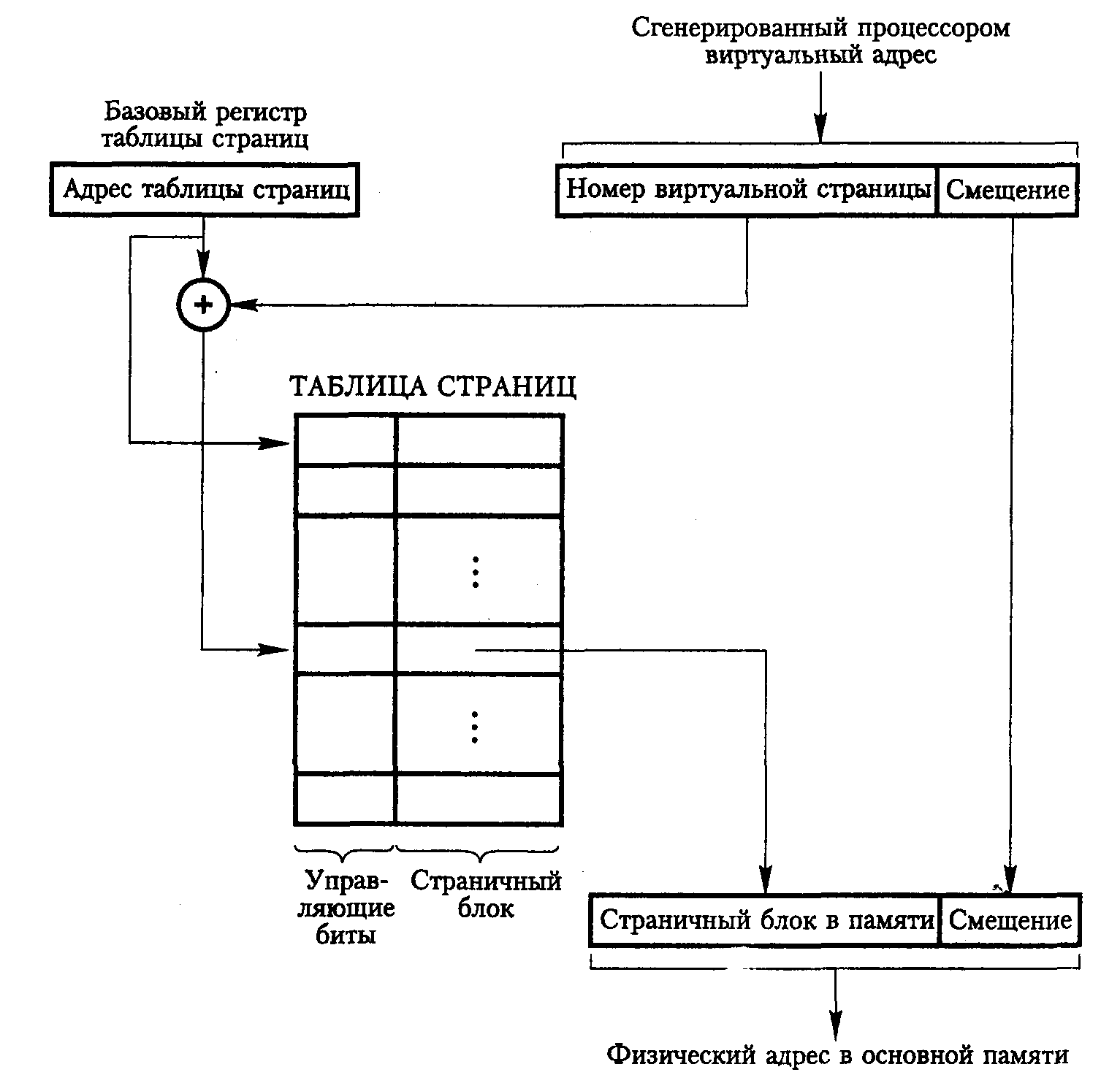

Итак, метод преобразования адресов основывается на концепции страниц фиксированной длины, схематически представленной на рис. 7.15. Каждый сгенерированный процессором виртуальный адрес, будь то адрес для операции выборки команды или для чтения и записи операнда, интерпретируется как номер виртуальной страницы (старшие разряды) и смещение (младшие разряды) байта или слова от начала страницы. Информация о местонахождении каждой страницы в основной памяти содержится в таблице страниц. Она включает адрес основной памяти, по которому хранится страница, и данные о ее текущем состоянии. Область основной памяти, где может находиться одна страница, называется страничным блоком. Начальный адрес таблицы страниц хранится в базовом регистре таблицы страниц. Добавив номер виртуальной страницы к содержимому этого регистра, вы получите адрес нужного элемента таблицы страниц. А в самом этом элементе хранится начальный адрес страницы, если, конечно, она имеется в основной памяти.

Рис. 7.15. Преобразование адресов виртуальной памяти

Кроме адреса страницы каждый элемент таблицы страниц содержит несколько управляющих битов, которые определяют состояние страницы, находящейся в основной памяти, и еще один бит, указывающий, хранится ли страница в памяти. Последний бит позволяет операционной системе пометить страницу как отсутствующую в памяти, не удаляя ее на самом деле. Еще один бит указывает, была ли страница модифицирована за то время, пока она находилась в основной памяти. Как и в случае кэш-памяти, на основании этой информации принимается решение о том, записывать ли страницу снова на диск перед ее удалением из основной памяти (когда нужно освободить место для другой страницы). Остальные управляющие биты действуют в соответствии с различными ограничениями, налагаемыми на доступ к странице. Например, программе могут быть предоставлены полные права на чтение и запись страницы или же только на ее чтение.

Диспетчер памяти, то есть MMU, использует информацию из таблицы страниц для выполнения каждой операции чтения или записи. Поэтому было бы целесообразно хранить эту таблицу прямо в нем. Но, к сожалению, она слишком велика, а блок управления памятью обычно интегрирован в микросхему процессора (вместе с кэшем первого уровня), куда невозможно добавить такой большой фрагмент памяти. Поэтому таблица страниц содержится в основной памяти. Диспетчер памяти может хранить небольшую ее часть, которая включает элементы, соответствующие недавно использовавшимся страницам. Практически это маленький кэш, обычно называемый буфером быстрого преобразования адреса (Translation Lookaside Buffer, TLB). У него то же назначение и такой же принцип действия, как и у любой другой кэш-памяти. Кроме элемента таблицы страниц в TLB должен содержаться виртуальный адрес этого элемента. На рис. 7.16 показан один из вариантов организация TLB на основе ассоциативного отображения. Существуют и TLB с множественно-ассоциативной организацией.

Исключительно важно, чтобы содержимое TLB соответствовало содержимому таблицы страниц в памяти. Когда операционная система изменяет содержимое таблицы страницы, она должна одновременно пометить соответствующие элементы TLB как недостоверные. Для этого в каждом таком элементе имеется специальный управляющий бит. Если элемент помечается как недостоверный, он обновляется в ходе обычной операции, выполняемой MMU, когда нужных данных в TLB не оказывается.

Преобразование адресов осуществляется следующим образом. Получив виртуальный адрес, MMU ищет в TLB заданную страницу. Если нужная запись находится в TLB, из нее тут же извлекается физический адрес страницы. В случае промаха, то есть отсутствия записи в TLB, она считывается из таблицы страниц в основной памяти, и TLB обновляется.

Когда программа генерирует запрос на доступ к странице, отсутствующей в основной памяти, происходит ошибка страницы. В этом случае перед продолжением операции вся страница должна быть перемещена с диска в основную память. Для этого MMU обращается к операционной системе, генерируя исключение (прерывание). В результате выполнение активной задачи прерывается, а управление передается операционной системе. Операционная система копирует запрошенную страницу с диска в основную память и возвращает управление прерванной задаче. Поскольку на пересылку страницы уходит довольно много времени, операционная система может приостановить выполнение задачи, вызвавшей ошибку страницы, и активизировать другую задачу, страницы которой имеются в основной памяти.

Важно, чтобы после приостановки задачи ее выполнение было продолжено. Поскольку ошибка страницы происходит при обращении некоторой команды к операнду, отсутствующему в основной памяти, прерывание производится до завершения выполнения этой команды. Когда выполнение задачи возобновляется, выполнение команды нужно продолжить либо с той точки, где оно было прервано, либо начать сначала. Выбор определяется архитектурой конкретного процессора.

Рис. 7.26. Принцип действия TLB с ассоциативным отображением

Если с диска нужно переместить новую страницу, а память уже заполнена, приходится удалять одну из страниц, уже имеющихся в памяти. Правильный выбор удаляемой страницы так же важен, как правильный выбор заменяемого блока в кэше, и здесь, конечно же, учитывается тот факт, что большую часть времени выполнение программы ограничивается несколькими локализированными областями. Поскольку основная память значительно больше кэш-памяти, в ней можно держать очень большие фрагменты программы. Поэтому частота обмена информацией с диском может быть сравнительно невысокой. К операции замены страниц применимы концепции, подобные применяемым в алгоритме LRU, а индикаторами использования страниц могут служить управляющие биты в таблице страниц. В одном из простейших алгоритмов замены задействован единственный управляющий бит, устанавливаемый при обращении к соответствующей странице в 1. Время от времени операционная система очищает этот бит во всех записях таблицы страниц, отмечая таким образом все эти страницы как давно не использовавшиеся.

Перед удалением из основной памяти модифицированная страница опять должна быть записана на диск. Однако протокол сквозной записи, который может успешно использоваться в кэш-памяти, для виртуальной памяти совершенно не подходит. Время доступа к диску настолько велико, что нет смысла часто обращаться к нему при необходимости записать небольшой объем данных.

Процесс преобразования адресов в диспетчере памяти сам требует некоторого времени, основная часть которого уходит на поиск записей в TLB. Поскольку принцип локализации ссылок действует и в этом случае, велика вероятность того, что в ряде последовательных преобразований будет использоваться адрес одной и той же страницы. Особенно часто так бывает при выборке команд. Поэтому среднее время преобразования адресов можно сократить, добавив в процессор один или несколько специальных регистров для хранения номера виртуальной страницы и адреса физического страничного блока, применявшихся в последнем преобразовании. Доступ к информации из этих регистров будет осуществляться даже быстрее, чем доступ к TLB.