- •7. Система памяти

- •7.1. Базовые концепции

- •7.2. Быстродействие, объем и стоимость

- •7.3.1. Функция отображения

- •7.3.2. Алгоритмы замещения

- •7.3.3. Примеры технологий отображения

- •7.3.4. Организация кэша в коммерческих процессорах

- •7.4. Производительность

- •7.4.1. Чередование операций

- •7.4.2. Частота попаданий и накладные расходы при промахах

- •7.4.3. Кэши на микросхеме процессора

- •7.4.4. Другие способы увеличения быстродействия

- •7.5. Виртуальная память

- •7.5.1. Преобразование адресов

- •7.6. Требования к управлению памятью

7. Система памяти

Программы и обрабатываемые ими данные хранятся, как известно, в памяти компьютера. В этой главе мы поговорим о том, как функционирует эта жизненно важная часть компьютерной системы. Читатель уже знает, что скорость выполнения программ напрямую зависит от скорости передачи данных между процессором и памятью и что для выполнения больших программ, обрабатывающих огромные массивы данных, необходима память очень большого объема.

В идеале память должна быть быстрой, большой и недорогой. Однако удовлетворить всем трем требованиям одновременно, к сожалению, невозможно. Чем больше память и чем быстрее она работает, тем дороже она стоит. Поэтому проектировщики компьютерных систем трудятся над разработкой и усовершенствованием технологий, позволяющих создавать для компьютера видимость большой и быстрой памяти.

Мы начнем эту главу с рассказа о наиболее распространенных компонентах и структурах, используемых для реализации памяти, а затем поговорим о быстродействии памяти и о том, как ее можно увеличить за счет кэширования. Далее речь пойдет о концепции виртуальной памяти, позволяющей представить память, как ее видит процессор, то есть большей, чем на самом деле. А напоследок мы расскажем вам о вторичных запоминающих устройствах, емкость которых значительно больше емкости основной памяти.

7.1. Базовые концепции

Максимальный размер памяти, который может использоваться компьютером, определяется его системой адресации. К примеру, 16-разрядный компьютер, генерирующий 16-разрядные адреса, может иметь память объемом до 216 = 64 Кбайт адресуемых единиц хранения, компьютер, команды которого генерируют 32-разрядные адреса, может использовать память объемом до 232 = 4 Гбайт адресуемых единиц, а для компьютеров с 40-разрядными адресами доступная память объемом до 240 = 1 Тбайт адресуемых единиц. Количество адресуемых единиц памяти определяет размер ее адресного пространства.

Большинство современных компьютеров, как вы знаете, адресуют память по байтово. На рис. 4.8 показано возможное назначение адресов в 32-разрядном компьютере с байтовой адресацией. При этом в процессорах Intel используется прямой порядок байтов, а в процессоре 68000 — обратный. Архитектура процессор ARM позволяет использовать обе схемы. С точки зрения структуры памяти между этими схемами нет существенных различий.

Обычно память разрабатывается с учетом того, что данные извлекаются и считываются не байтами, а словами. Само понятие длины слова чаще всего определяется как количество битов, сохраняемых или считываемых за одно обращение к памяти. Возьмем, к примеру, компьютер с байтовой адресацией, команды которого генерируют 32-разрядные адреса. Когда процессор генерирует 32-разрядны адрес основной памяти, старшие 30 разрядов определяют слово, к которому производится доступ. Если задано и количество байтов, два младших разряда определяют его положение в слове. В байтовой операции чтения из памяти могут быть извлечены и другие байты, но они игнорируются процессором. Если же выполняется байтовая операция записи, управляющие схемы памяти должны гарантировать, что остальные байты слова останутся неизменными.

Современные схемы реализации компьютерной памяти довольно сложны. Чтобы упростить для вас процесс знакомства со структурами памяти, мы сначала обсудим традиционную архитектуру, и только после этого перейдем к современным подходам и технологиям.

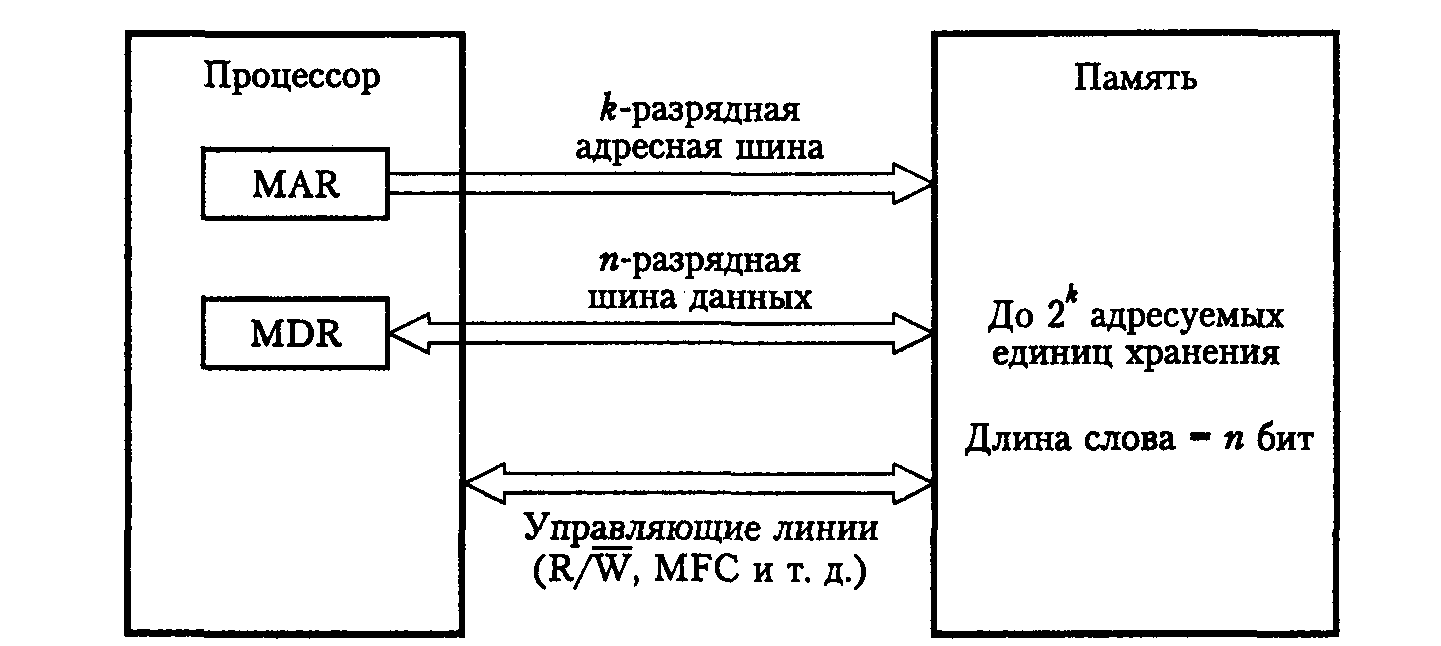

Со стороны системы

запоминающее устройство можно

рассматривать как черный ящик. Пересылка

данных между памятью и процессором

выполняется, как вы помните из раздела

3.3, с помощью двух регистров процессора,

обычно называемых MAR

(Memory

Address

Register

— регистр адреса) и MDR

(Memory

Data

Register

— регистр данных). Если регистр MAR

содержит k

битов, а регистр MDR -n

битов, память может содержать до 2k

адресуемых единиц хранения. За один

цикл обращения к памяти между нею и

процессором пересылается n

бит

данных. Данные передаются по шине

процессора, имеющей k

адресных линий и n

линий данных. Кроме того, шина содержит

линии для управления передачей данных

![]() (READ/

(READ/![]() )

иMFC

( Memory

Function

Compelled).

Могут использоваться и другие линии, с

помощью которых задается количество

пересылаемых данных Соединение между

процессором и памятью схематически

показано на рис. 7.1.

)

иMFC

( Memory

Function

Compelled).

Могут использоваться и другие линии, с

помощью которых задается количество

пересылаемых данных Соединение между

процессором и памятью схематически

показано на рис. 7.1.

Чтобы считать

данные из памяти, процессор сначала

загружает адрес в регистр MAR

и устанавливает линию

![]() в 1. В ответ память помещает данные на

линии данных и подтверждает это действие

активизацией сигнала MFC.

После получения сигнала MFC

процессор загружает данные с адресных

линий в регистр MDR.

в 1. В ответ память помещает данные на

линии данных и подтверждает это действие

активизацией сигнала MFC.

После получения сигнала MFC

процессор загружает данные с адресных

линий в регистр MDR.

Для того чтобы

записать данные в память, процессор

загружает адрес в регистр MAR,

а данные в регистр MDR и устанавливает

линию

![]() в

0, указывая таким образом, что выполняется

операция записи.

в

0, указывая таким образом, что выполняется

операция записи.

Если в операциях чтения производится обращение по последовательным адресам, может быть выполнена операция блочной пересылки, при которой памяти передается только один адрес — адрес первого байта блока данных.

Доступ к памяти может синхронизироваться тактовым генератором или специальными сигналами, управляющими пересылкой по шине. Управление операциями чтения из памяти и записи в память осуществляется так же, как и управление операциями ввода и вывода по шине.

Рис. 7.1. Организация связи системы памяти с процессором

Например, Intel 80286 поддерживал адресацию до 1Mb (220) при размере слова 16 Бит. Т.е. шина адреса была 20 разрядная, а шина данных 16 разрядная. В архитектуре IA-32 размер слова 32 бита, адресная шина 32 бита, адресация до 4Gb (232) (может быть и больше в серверных системах), а шина данных может быть 32 и 64 бита.

Быстродействие памяти характеризуется интервалом времени между инициированием операции и ее завершением, например временем между сигналами чтения и MFC. Это время определяют как время доступа к памяти. Еще одной важной характеристикой быстродействия памяти является цикл памяти — минимальный промежуток времени между моментами начала двух последовательных операций с памятью, например, между двумя последовательными операциями чтения. Цикл памяти обычно немного больше времени доступа (это зависит от особенностей реализации запоминающего устройства).

В запоминающем устройстве, называемом памятью с произвольным доступом (Random Access Memory, RAM), на обращение по любому адресу уходит одно и то же время. Этим RAM-память отличается от запоминающих устройств с последовательным или частично-последовательным доступом, таких как магнитные диски или ленты. Время доступа последних зависит от адреса или местоположения данных.

Для реализации основной памяти компьютера используются полупроводниковые интегральные схемы.

Обычно процессор обрабатывает команды и данные быстрее, чем они выбираются из памяти. Поэтому цикл доступа к памяти является узким местом системы. Одним из способов сокращения времени доступа к памяти может стать использование кэш-памяти. Это быстрая память небольшого объема, расположенная между сравнительно медленной основной памятью компьютера и процессором. В ней хранятся текущие фрагменты программы и ее данных.

Еще одной важной концепцией, связанной с организацией памяти, является концепция виртуальной памяти. До сих пор мы предполагали, что генерируемые процессором адреса полностью соответствуют физическим ячейкам памяти. Однако на практике это не всегда так. По определенным причинам, о которых мы поговорим далее в этой главе, данные могут храниться не по тем адресам, которые заданы в программе. Схемы управления памятью преобразуют указанный в программе адрес в другой адрес, используемый для доступа к физической памяти. В таком случае сгенерированный процессором адрес называют виртуальным или логическим. Виртуальное адресное пространство определенным образом отображается на физическую память, в которой хранятся данные. Отображение выполняется с помощью специальных управляющих схем памяти, часто называемых блоком управления памятью. В ходе выполнения программы функция отображения может меняться в соответствии с системными требованиями.

Виртуальная память предназначена для увеличения видимого компьютером объема физической памяти. Виртуальное адресное пространство и объем расположенных в нем данных могут быть настолько большими, насколько позволяют возможности адресации используемого процессора. Причем в каждый конкретный момент только часть этого адресного пространства отображается на физическую память. Остальные виртуальные адреса соответствуют устройствам массовой памяти — как правило, магнитным дискам. Когда выполняющейся программе требуется доступ к данным, адреса которых не отображаются на реальную память, блок управления памятью изменяет функцию отображения и пересылает данные с диска в основную память. Поэтому в каждом цикле обращения к памяти система обработки адресов определяет, находится ли адресуемая информация в основной памяти компьютера. Если да, происходит обращение к соответствующему слову памяти и выполнение программы продолжается. Если нет, с диска в память пересылается страница, содержащая нужное слово (см. раздел 7.7.). Эта страница заменяет в памяти какую-нибудь другую страницу, которая пока не нужна программе. Поскольку на пересылку страниц между памятью и диском уходит некоторое время, при частом перемещении страниц скорость работы компьютера снижается. Но если выбор заменяемых страниц выполняется продуманно, вероятность того, что необходимые страницы окажутся в основной памяти, возрастет.

В этом разделе будет коротко рассказано о нескольких важнейших функциях организации системы памяти. Их назначение заключается в обеспечении компьютерной системы настолько большой и быстрой памятью, насколько это возможно с учетом общей стоимости системы. Мы не ждем, что читатель сразу же усвоит все концепции организации памяти и их следствия, поэтому к этим вопросам мы еще вернемся в данной главе. Пока же мы лишь ввели основные понятия указанной области в их взаимосвязи, поскольку это так же важно, как изучение каждой отдельной функции и концепции.