ЭБНЭ_full

.pdfЭтапы технологического процесса при производстве микросхем

Механическая обработка полупроводниковых пластинХимическая обработка (предшествующую всем термическим операциям)Эпитаксиальное наращивание слоя полупроводникаФотолитография

Введение электрически активных примесей в пластину для образования отдельных p- и n-областейТермическая диффузияИонное легирование

Получение омических контактов и создание пассивных элементов на пластине

Добавление дополнительных слоев металла

Пассивация поверхности пластины.Тестирование неразрезанной пластины.Разделение пластин на кристаллы

Сборка кристалла и последующие операции монтажа кристалла в корпус и герметизацияЭлектрические измерения и испытанияВыходной контроль

Маркировка, нанесение защитного покрытия, упаковка

Технологический процесс производства интегральных схем

С 1994 года Международной ассоциации производителей полупроводников (ITRS) создает «дорожную карту» на следующие 15 лет.

3 мкм..1,5..0,8..0,5..0,35..0,25..0,18..0,13 ..(130 нм)..90..60..45..32..22..16 нм...

Материалом для производства чипов сейчас является кремний - Si.

монокристаллический сверхчистый кремний, с содержанием вредных

(посторонних) примесей на уровне менее 0,00000001%.

монокристаллы диаметром D = 30, 60, 90, 150, сейчас 300 мм и планируется увеличение до 450 мм.

Процесс - планарный

Технологический процесс производства интегральных схем

С 1994 года Международной ассоциации производителей полупроводников (ITRS) создает «дорожную карту» на следующие 15 лет.

3 мкм..1,5..0,8..0,5..0,35..0,25..0,18..0,13 ..(130 нм)..90..60..45..32..22..16 нм...

3 мкм 1975 году Zilog (Z80) и в 1979 году Intel (Intel 8086).

Al или polySi затворы, изоляция обратносмещенным pn-переходом, напряжение питания 5 В,Al металлизация. 1,5 мкм Intel 80286

Возможность снизить напряжение питания, polySi затворы.

0,8 мкм Intel 80486 (1989 год) MicroSPARC I (1992 год) первые Intel P5 Pentium на частотах 60 и 66 МГц (1993 год)

LOCOS, многослойная металлизация. Возможность снизить напряжение питания, самосовмещающиеся polySi

затворы.

0,5 мкм Intel и IBM в 1994—1995 годах. Intel Pentium на частотах 75, 90 и 100 МГц

LOCOS (модифицированный), планаризация поверхности многослойная металлизация. Возможность снизить напряжение питания, самосовмещающиеся polySi затворы.

350 нм (0,35 мкм) 1997 год ведущими компаниями-производителями микросхем, такими как Intel, IBM, и TSMC. Intel Pentium MMX (P55)

Intel Pentium Pro

Pentium II (Klamath)

Понижение напряжения питания, LOCOS (модифицированный) или SOI/STI, планаризация поверхности многослойная металлизация. самосовмещающиеся polySi затворы, технологии тонких пленок

Технологический процесс производства интегральных схем

250 нм Используется до 6 слоёв металла, минимальное количество литографических масок 22. Pentium II (Deschutes)

Pentium III (Katmai)

SOI/STI, Понижение напряжения питания, планаризация поверхности многослойная металлизация. самосовмещающиеся polySi затворы, технологии тонких пленок

180 нм Соответствует удвоению плотности размещения по отношению к предыдущему техпроцессу 0,25 мкм. Содержит до 6-7 слоёв металла. Минимальное количество литографических масок около 22., SOI/STI, Понижение напряжения питания, планаризация поверхности, многослойная металлизация/медная металлизация. самосовмещающиеся polySi затворы, технологии тонких пленок

AMDAthlon XP (Palomino)

Intel Pentium III (Coppermine)

130 нм 2000—2001 года удвоению плотности размещения элементов по отношению к предыдущему техпроцессу 0,18 мкм. SOI/STI, Понижение напряжения питания, планаризация поверхности, медная металлизация. Ме затворы, технологии тонких пленок

Intel Celeron Tualatin-256 — октябрь 2001 Intel Pentium 4 Northwood — январь 2002 AMDAthlon XPThoroughbred,Thorton и Barton

AMDAthlon 64 Clawhammer и Newcastle — сентябрь 2003 AMD Opteron Sledgehammer — июнь 2003

МЦСТ Эльбрус 2000 (1891BM4Я) — июль 2008

Технологический процесс производства интегральных схем

90 нм 2002—2003 годам. соответствует удвоению плотности размещения элементов по отношению к предыдущему техпроцессу 0,13 мкм.

Технологический процесс с проектной нормой 90 нм часто используется с технологиями напряженного кремния, медных соединений с меньшим сопротивлением, чем у ранее применяемого алюминия, а также c новыми диэлектрическими материалами с низкой диэлектрической проницаемостью.

Intel Pentium4 (Prescott)

AMD Turion 64 X2 (мобильный)

Эльбрус-S – 2010

толщина оксидной пленки затвора 1,2 нм (самая тонкая пленка в индустрии)

изначальная длина затвора 50 нм, в ближайшие два года будет еще уменьшена (сравните с 70 нм длиной затвора на первых 0,13 мкм чипах, и 60 нм длина - на нынешних)

использование нового low-k кремний-примесногооксидного диэлектрика для уменьшения емкостного сопротивления провод-провод (так достигается уменьшение мощности)

65 нм 2004 год соответствует удвоению плотности размещения элементов по отношению к предыдущему техпроцессу 90 нм.

Intel Celeron

Intel Core AMDAthlon 64

Для микроэлектронной промышленности стал революционным, так как это был первый техпроцесс, использующий технологию high-k/metal gate (HfSiON/TaN в технологии компании Intel), для замены физически себя исчерпавших

SiO2/poly-Si

45 нм / 40 нм 2006—2007 соответствует удвоению плотности размещения элементов по отношению к предыдущему техпроцессу 65 нм.

Для микроэлектронной промышленности стал революционным, так как это был первый техпроцесс, использующий технологию high-k/metal gate (HfSiON/TaN в технологии компании Intel), для замены физически себя исчерпавших

SiO2/poly-Si

Intel Core 2 Duo

Intel Core 2 Quad

Технологический процесс производства интегральных схем

32 нм / 28 нм 2009—2010 года соответствует удвоению плотности размещения элементов по отношению к предыдущему техпроцессу 45 нм.

Многоядерные процессоры Мобильные процессоры

AMD Steamroller (третье поколение Bulldozer, ожидается к середине 2014 года)[16][17]

Для микроэлектронной промышленности стал революционным, так как это был первый техпроцесс, использующий технологию high-k/metal gate (HfSiON/TaN в технологии компании Intel), для замены физически себя исчерпавших

SiO2/poly-Si

22 нм / 20 нм 2009—2012 гг. Соответствует удвоению плотности размещения элементов по отношению к предыдущему техпроцессу 32 нм.

22-нм элементы формируются путем фотолитографии, в которой маска экспонируется светом с длиной волны 193 нм

транзисторов типа FinFET, которые, в свою очередь, выполняются по прогрессивной технологии high-k/metal gate (затворы транзистора изготавливаются не из кремния, а из гафния), площадью всего 0,128 мкм² (0,58×0,22 мкм)[23].

Первые работоспособные тестовые образцы регулярных структур (SRAM) представлены публике компанией Intel в 2009 году. 22-нм тестовые микросхемы представляют собой память SRAM и логические модули. SRAM-ячейки размером 0,108 и 0,092 мкм² функционируют в составе массивов по 364 млн бит. Ячейка площадью 0,108 мкм² оптимизирована для работы в низковольтной среде, а ячейка площадью 0,092 мкм² является самой миниатюрной из известных сегодня ячеек SRAM.

14 нм / 16 нм FinFET По состоянию на сентябрь 2014 TSMC продолжает разработки 16 нм техпроцесса на транзисторах с вертикально расположенным затвором (fin field effect transistor, FinFET)

потребовалось применение масок с технологией Inverse Lithography (ILT) и SMO (Source Mask Optimization)

Поперечное сечение ИС

Металл8

Металл8

Металл7

Металл7

Металл6

Металл5 Металл4 Металл3

Металл2 Металл1 Поликремний

Шины питания и защита

Коммутация внутри логических блоков

Логические  элементы

элементы

Как делают интегральные схемы

Фотолитография - процесс избирательного травления поверхностного слоя с использованием защитного фотошаблона.

Технология построена по принципу «свет-шаблон-фоторезист» и проходит следующим образом:

-На кремниевую подложку наносят слой материала, из которого нужно сформировать рисунок. На

него наносится фоторезист - слой полимерного светочувствительного материала, меняющего свои физико-химические свойства при облучении светом. - Производится экспонирование (освещение фотослоя в течение точно установленного промежутка времени) через фотошаблон. - Удаление отработанного фоторезиста. Нужная структура рисуется на фотошаблоне - как правило, это пластинка из оптического стекла, на которую фотографическим способом нанесены непрозрачные области. Каждый такой шаблон содержит один из слоев будущего процессора, поэтому он должен быть очень точным и практичным.

Как делают интегральные схемы

Иной раз осаждать те или иные материалы в нужных местах пластины просто невозможно, поэтому гораздо проще нанести материал сразу на всю поверхность, убрав лишнее из тех мест, где он не нужен - на изображении выше синим цветом показано нанесение фоторезиста.

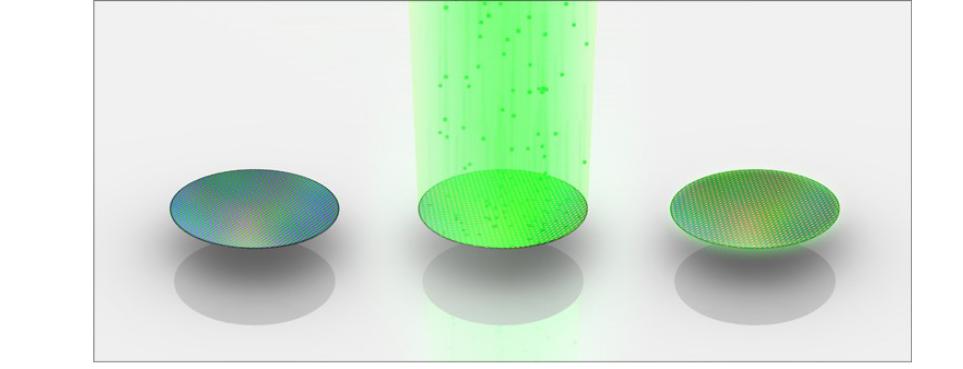

Пластина облучается потоком ионов (положительно или отрицательно заряженных атомов), которые в заданных местах проникают под поверхность пластины и изменяют проводящие свойства кремния (зеленые участки — это внедренные чужеродные атомы).

Как делают интегральные схемы

Как изолировать области?

Перед литографией на поверхность кремниевой пластины (при высокой температуре в специальной камере) наносится защитная пленка диэлектрика.