- •Введение

- •Раздел 1. Анализ существующих структур дешифраторов

- •1.1 Линейный дешифратор

- •1.2 Каскадные дешифраторы с принципом построения на много выходов из микросхем дешифраторов с меньшим числом выходов

- •Прямоугольный дешифратор

- •Анализ рассмотренных типов дешифраторов

- •Раздел 2. Разработка функциональной схемы каскада дешифраторов

- •2.1 Функциональная схема dc и её описание

- •Выбор элементов и интегральных микросхем

- •2.4 Описание работы базового элемента ттлш серии 1533

- •Раздел 3. Разработка функциональной и принципиальной электрической схемы каскада дешифраторОв и временные диаграммы его работы

- •Раздел 4. РасчеТы: бЫстродействия, потребляеМой мощности, помехоустойчивости, нагрузочной способности, рабочего значения плотности тока в проводниках на печатной плате, надежности

- •4.1. Расчет быстродействия

- •Раздел 5. Конструктивная часть

- •5.1. Технология изготовления печатной платы

- •5.2. Конструкция узла

- •5.3. Размещение элементов на плате

- •Заключение

- •Список используемой литературы

Раздел 3. Разработка функциональной и принципиальной электрической схемы каскада дешифраторОв и временные диаграммы его работы

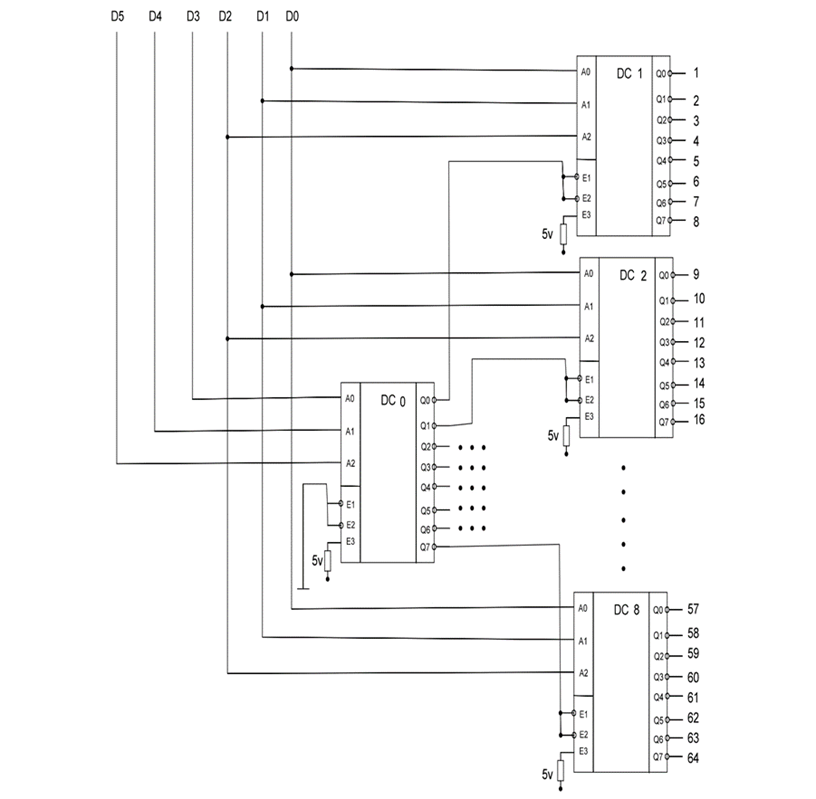

Особенности схемы, изображённой на рисунке 3.1: дешифратор не является синхронным. Это не является недостатком схемы: так как подключенный к выходам дешифратора функциональный элемент можно разработать с разрешением считывания управляющего сигнала. Обоснование выбора схемы: Данный дешифратор является линейным. Линейный дешифратор наиболее подходит для реализации, так как он экономичен по оборудованию и имеет минимальную задержку.

Рисунок 3.1 – Функциональная электрическая схема каскада дешифраторов

ИМС дешифраторов имеют ограниченное число адресных входов и информационных выходов. Увеличение их возможно путем наращивания (каскадирования), которое можно осуществлять двумя способами: объединением нескольких дешифраторов в пирамидальную схему, или последовательным соединением разрешающих входов через внешние логические элементы или непосредственно друг с другом. При наращивании дешифраторов разряды двоичного адресного кода разделяются на старшие (СРА) и младшие (МРА) разряды адреса. СРА с помощью дешифратора DD0 входов стробирования, разрешают функционирование одного из основных дешифраторов DD1...DD8). МРА подаются параллельно на адресные входы всех выходных дешифраторов. Однако активируется только один соответствующий выход выбранного СРА дешифратора.

Дешифраторы этой схемы можно включить различными способами и получить, например, дешифратор 6→64 со входом стробирования.

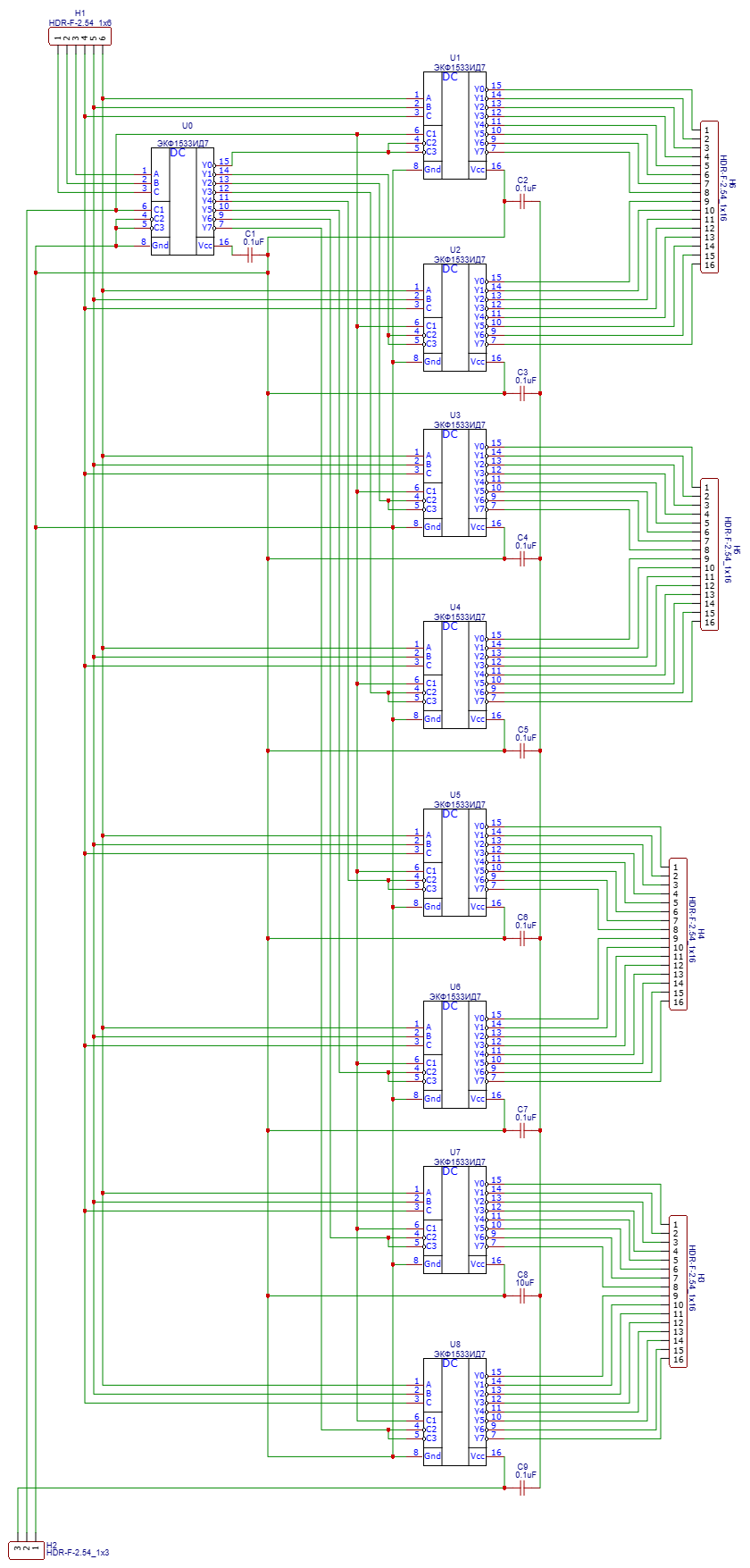

Разрабатываемый двоичный дешифратор 6→64 состоит из девяти ИМС ЭКФ1533ИД7 и девяти тантаповых конденсаторов емкостью 0,1 мкФ, в SMD корпусе. Необходимость использования которых обусловлена следующими соображениями:

Значение порога у элементов технологии ТТЛ (ТТЛШ) близко к уровню земли, вследствие чего все это логическое семейство в известной степени подвержено влиянию помех. Так как эти логические семейства являются быстродействующими, они воспринимают короткие всплески по шине земли.

Такие всплески часто возникают при быстрой смене состояний на выходах, что еще более осложняет проблему. Биполярные элементы предъявляют высокие требования к источнику питания: +5В±5% при относительно высокой мощности рассеяния. Наличие токовых всплесков в шинах питания, которые вырабатываются схемами с активной нагрузкой, как правило, требует шунтирования источника питания, в идеальном случае один конденсатор емкостью 0,1 мкФ на каждый корпус ИМС.

При разработке принципиальной схемы каскада дешифратора использовался онлайн конструктор EasyEDA. EasyEDA - это кросс-платформенная веб-ориентированная среда автоматизации, включающая в себя редактор принципиальных схем, редактор топологии печатных плат, SPICE-симулятор, облачное хранилище данных, систему управления проектами, а также средства заказа изготовления печатных плат.

EasyEDA - это мощный инструмент для создания и тестирования электронных схем. Он предлагает широкий спектр функций, которые помогают инженерам и энтузиастам электроники в проектировании и тестировании своих проектов.

С помощью редактора принципиальных схем можно легко создавать сложные электронные схемы, а редактор топологии печатных плат помогает в проектировании печатных плат. SPICE-симулятор позволяет проводить точное моделирование и анализ электронных схем.

Облачное хранилище данных обеспечивает безопасное и удобное хранение всех ваших проектов и файлов.

Кроме того, EasyEDA предлагает средства для заказа изготовления печатных плат прямо из приложения, что значительно упрощает процесс изготовления прототипов и массового производства.

Схема собрана на девяти ИМС ЭКФ1533ИД7 в DIP-16 корпусе и девяти конденсаторах SMD корпусе. Четыре 16 пиновых разъемов составляют 64 пиновую выходную шину. Шести пиновый разъем является адресным входом дешифратора. Трех пиновый - разъем питания.

ИМС U0, U1, U2, U3, U4, U5, U6, U8, собраны в выходной каскад на 64 выхода. Микросхема U0 используется для перехода в старший разряд. Она управляет разрешающими входами восьми ИМС, включает или выключает одну из них. Так реализован дешифратор 6→64 на ИМС ЭКФ1533ИД7 с тремя адресными и тремя разрешающими входами.

На рисунке 3.2 показана принципиальная схема каскада дешифратора 6→64 собранная на ИМС ЭКФ1533ИД7.

Рисунок 3.2 – Принципиальная схема каскада дешифраторов 6→64

Временная диаграмма представлена на рисунке 3.3.

Рисунок 3.3 – Временная диаграмма работы дешифратора ЭКФФ1533ИД7

Таким образом в этом разделе была разработана принципиальная и функциональная схема каскада дешифраторов, а также построена временная диаграмма работы дешифратора.