- •Структура (архитектура) однокристального восьмиразрядного микропроцессора мп580вм80

- •Принцип работа мп

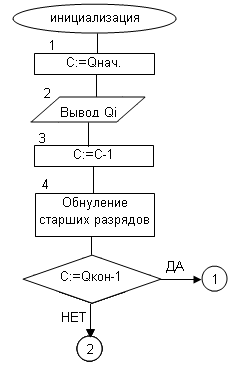

- •Алгоритм программы (основной) формирователя сигналов сложной формы

- •Программа формирователя сигналов сложной формы

- •Организация интерфейса ввода/вывода данных

- •Организация прерывания работы микропроцессоров Классификация прерываний в микропроцессоре

- •Организация прерываний в мп кр 580вм80 (симулятор Avsim85)

- •Интерфейс мп кр58вм80

- •Структура системного микроконтроллера.

- •Перспектива развития микропроцессорной техники Современные микроконтроллеры (мк). Определение и классификация микроконтроллеров.

- •Особенности построения мк avr фирмы «Atmel»

- •Память микроконтроллера

- •Особенности разработки и отладки программ для микроконтроллеров avr

- •2.1. Ассемблер

- •2.2. Формат программ на ассемблере

- •2.3. Система команд микроконтроллеров avr

- •2.4. Директивы транслятора ассемблера

- •2.5. Средства разработки программ avr – mk

- •Программируемые логические интегральные схемы (плис) Определения и история разработки плис.

Г ОУ

ВПО СПб ГУТ им. проф. М.А. Бонч-Бруевича

ОУ

ВПО СПб ГУТ им. проф. М.А. Бонч-Бруевича

2012 г.

Распределение времени на изучение дисциплины:

Лекции: 28час, лабораторные занят. – 22час., курсовая работа – 6час.

Отчетность: Зачет и защита курсовой работы с оценкой.

Лекция №1: Общие принципы организации и работы микропроцессорной системы

Учебные вопросы:

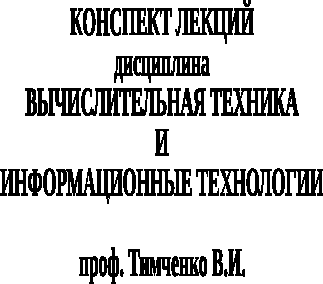

1. Структура (архитектура) микропроцессорной системы (МПС).

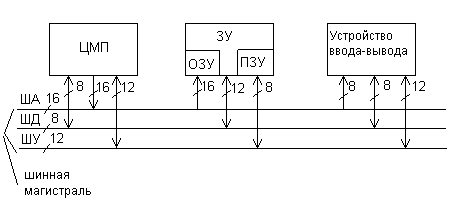

2. Структура, архитектура однокристального восьмиразрядного микропроцессора (МП) КР580ВМ80.

Литература:

Основнаялитература

1. Цифровая и вычислительная техника. Под ред. Евреинова Э.В М.,. р\св, 1991г.

2. Яковлев Л.А. , Тимченко В.И. «Вычислительная техника»: Методические указания к лабораторным работам СПбГУТ, 2006г.

3. Методические указания по курсовому проектированию по дисциплинам цифровой, вычислительной и микропроцессорной техники. СПбГУТ, 1997г.

4. Гольденберг Л.М. и др. «Цифровые устройства и микропроцессорные системы». Задачи и упражнения. СПбГУТ, 1992г.

Дополнительная литература

1. Белов А.В. Самоучитель разработчика устройств на микроконтроллерах AVR. Наука и техника, СПБ, 2010г. Имеется в продаже (~300руб.) и на сайте интернета.

Вопросы к экзамену:

1.Назначение, структура (архитектура) МПС (с учетом интерфейса шины данных и шины управления).

2. Назначение, структура (архитектура) 8-ми разрядного МП КР580 ВМ80 на примере выполнения команд пересылки данных MOV, MVI.

3. Способы адресации команд МП КР580 ВМ80.

4.Структура команды МП КР580 ВМ80.

5.Назначение, структура (архитектура) 8-ми разрядного МП КР580 ВМ80 на примере выполнения арифметических команд ADD r, ADD M, ADI, SUB r, SUI.

6. Назначение, структура (архитектура) 8-ми разрядного МП КР580 ВМ80 на примере выполнения арифметических команд INR r, INR M, INX rr, DCR r, DCRM, DCX rr.

7. Назначение, структура (архитектура) 8-ми разрядного МП КР580 ВМ80 на примере выполнения команд ввода/вывода данных IN, OUT.

8. Назначение, структура (архитектура) 8-ми разрядного МП КР580 ВМ80 на примере выполнения команд условного и безусловного перехода JMP, JM, JNZ, JZ.

9. Назначение, структура (архитектура) 8-ми разрядного МП КР580 ВМ80 на примере выполнения команд сдвига RRC, RLC и инвертирования CMA; HLT, NOP.

10. Назначение, структура (архитектура) 8-ми разрядного МП КР580 ВМ80 на примере выполнения команд логических операций ANI, ANA M, ANA r, ORA r, ORA M, ORI, XRI, XRA.

11. . Назначение, структура (архитектура) 8-ми разрядного МП КР580 ВМ80 на примере выполнения команд логического сравнения CMP r, CPI.

12. Назначение, структура (архитектура) 8-ми разрядного МП КР580 ВМ80 на примере выполнения команд со стеком LXI SP, SPHL, PUSH, POP.

13. Назначение, структура (архитектура) 8-ми разрядного МП КР580 ВМ80 на примере выполнения команд обращения к подпрограммам CALL, RET.

14. Принцип построения, алгоритм и программа счетчика с произвольным порядком смены состояний.

15. Назначение и структура 2-у направленного ШФ и буферного регистра.

16. Организация прерывания работы микропроцессора: назначение прерываний, сущность выполнения запроса на прерывание, понятие вектора прерывания, классификация прерывания, структура слова прерывания (RIM), команды организации прерывания.

17. Микроконтроллеры: определение, классификация и архитектура.

Задачи:

Алгоритм и программа n-разрядного счетчика с заданными Q0 и QN. и сигналами управления «установка нач.состояния», «останов счетчика» в разрядах аккумулятора Аi и Аj;

Алгоритм и программа счетчика с произвольным порядком смены состояний и сигналами управления «установка нач.состояния», «останов счетчика» в разрядах аккумулятора Аi и Аj;

Алгоритм и программа временной задержки.

1-й учебный вопрос

Структура (архитектура) микропроцессорной системы (МПС)

Определение МПС: комплекс аппаратных и программных средств, которые выполняют определённый набор арифметических и логических операций, таких как: сложение, умножение, сравнение, запись, чтение и другие.

К МПС относят компьютеры, микроконтроллеры и другие цифровые устройства, которые включают программное обеспечение.

Описание операции, которую должна выполнять МПС, называется командой.

Каждая команда кодируется условным обозначением, которое называется кодом операции (КОП).

Исходные данные, которые обрабатываются в МПС, называются операндами.

Пример:

Команда на языке ассемблер MOV B,C; комментарий (B) (C)

Команда в машинном коде 01000001b - 41 h

MOV B,C – команда.

MOV – код операции в мнемонической форме.

B, C – операнды.

Совокупность операций (команд), выполняемых в данной МПС, называется системой команд. В 8-ми разрядном МП свыше сотни команд, в 32-х разрядном МП (персональный компьютер) около1000 команд.

Структура и принцип функционирования МПС

Любая МПС включает следующие устройства:

1. Центральный микропроцессор (ЦМП). Он занимается обработкой информации

Запоминающее устройство (ЗУ), которое состоит из оперативного запоминающего устройства (ОЗУ) и постоянно запоминающего устройства (ПЗУ). ОЗУ – энергетически зависящие устройство, т.е. хранит информацию, только пока к нему подается питание. В ПЗУ информация может храниться постоянно.

Устройства ввода, вывода. К ним относятся: клавиатура, мышка, винчестер, дисплей и т.д.

Все устройства соединены между собой шинами, а именно:

шина адреса (ША),

шина данных (ШД),

шина управления (ШУ).

В совокупности перечисленные шины образуют системную магистраль.

Принцип работы МПС состоит в выполнении заранее разработанной программы, которая определяет последовательность выполнения команд (операций).

Выполнение программы осуществляется последовательным считыванием с ЗУ команды, её дешифрированием и выполнением.

Выполнение команды осуществляется в 2 этапа:

Считывание и дешифрирование команды: ЦМП выставляет на шину адреса (ША) адрес очередной выполняемой команды. Этот адрес по ША поступает в ЗУ. Кроме того, в ЗУ по шине управления (ШУ) подается сигнал чтения содержимого ячейки памяти (ЯП). Содержимое ЯП с кодом команды (операции) по шине данных (ШД) поступает в ЦМП .

В ЦМП содержимое ЯП дешифрирования формируются сигналы для выполнения команды

По результатам дешифрирования МП осуществляется выполнение команды.

По окончании выполнения команды на ША выставляется адрес очередной команды и далее выполняется очередная команда.

2-й учебный вопрос

Структура (архитектура) однокристального восьмиразрядного микропроцессора мп580вм80

Определение МП – программно-управляемое устройство, реализуемое на одном или нескольких чипах, которое осуществляет процесс цифровой обработки информации и управление им.

Структура МП

МП состоит из трех блоков:

1 .

Блок обработки информации ( ).

.

Блок обработки информации ( ).

2. Блок управления

( ).

2. Блок управления

( ).

3. Блок хранения

информации ( ).

3. Блок хранения

информации ( ).

Блок обработки информации включает восьмиразрядный регистр – аккумулятор, предназначенный для хранения одного из операндов команды и результата операции (выполнения команды).

MOV B,C ; (B)←(C)

АЛУ – арифметическое логическое устройство, которое выполняет необходимые арифметические и логические действия над операндами и результат записывает в аккумулятор.

Восьмиразрядный регистр признаков (регистр флагов) необходим для хранения признаков выполнения действий в АЛУ.

7 6 5 4 3 2 1 0

|

S |

Z |

0 |

AC |

0 |

P |

1 |

CY |

|

|

|

|

|

|

|

|

|

S – признак отрицательного результата (S=1).

Z – признак нулевого результата (Z=1).

0 – не используется.

AC – признак переноса между полубайтами (АС=1).

Р – признак четного числа единиц в байте результата, т.е. в аккумуляторе (Р=1).

СY – признак переноса старшего разряда результата (СY=1).

Блок управления включает восьмиразрядный регистр команд, предназначенный для хранения КОП-а.

Дешифратор команд дешифрирует КОП и выдает управляющие сигналы на устройство управления.

Устройство управления осуществляет управление процессом выполнения команд.

Блок хранения информации включает шесть восьмиразрядных регистров (регистры общего назначения – РОН) – В, С, D, E, H, L. Они предназначены для временного хранения информации в МП (в КЭШ памяти).

Регистры РОН могут использоваться как по отдельности (восьмиразрядные), так и парами (шестнадцатиразрядные).

Только такие пары регистров могут быть В-С, D-E, H-L .

Указатель стека (SP) – шестнадцатиразрядный регистр, предназначенный для хранения адреса стековой памяти.

Стековая память – выделенная память ОЗУ, в которой реализуется принцип: «первый записал, последний прочитал».

Счетчик команд – шестнадцатиразрядный регистр, предназначенный для хранения адреса выполняемой команды.

Принцип работа мп

Работу МП рассмотрим на примере выполнения команды арифметического сложения.

Команда на языке ассемблера (пользователя):

ADD B; (А)←(А)+(В)

Комнда в машинном коде (микропроцессора):

Команды программы предварительно записаны в ЗУ (ОЗУ или ПЗУ).

Все команды в МП выполняются в два этапа:

выборка (чтение из ЗУ) и дешифрование команды;

выполнение команды.

На первом этапе выполнения команды адрес выполняемой команды, записанной в счетчике команд (PC), под воздействием сигнала управления выставляется на 16-ти разрядную шину адреса (ША) и по ША поступает в ЗУ. В ЗУ ячейка памяти (ЯП) с указанным адресом под воздействием сигналов управления инициализируется на чтение. Содержимое ЯП по шине данных (ШД) поступает в регистр команд и далее на дешифратор команд. Содержимое регистра команд (КОП) хранится в течение выполнения команд. В результате дешифрования команды формируется управляющие сигналы для устройства управления. выполнения команды

На втором этапе осуществляется выполнение команды по микротактам под воздействием сигналов управления. В нашем примере ADD B: содержимое регистра В (РОН) по внутренней шине данных МП поступает в АЛУ, где суммируется с содержимым аккумулятора в АЛУ, т.е. арифметическое сложение содержимого регистров А+В. Результат сложения записывается в аккумулятор. Кроме того, в регистр признаков заносятся признаки выполняемой операции (Z=1, если 0-й результат; S=1, если отрицательное значение результата операции записывается в Ак). После выполнения арифметической операции (в нашем примере) в счетчике команд (PC) будет записан адрес очередной выполняемой команды.

Лекция 2

Система команд восьмиразрядного микропроцессора КР580ВМ80

(Int 8085 или Z80)

Учебные вопросы:

Структура команд и режимы адресации.

Система команд.

Структура команд и режимы адресации.

Команды по занимаемой памяти делятся на:

однобайтные;

двухбайтные;

трёхбайтные.

В однобайтной команде хранится код операции и операнды. Например:

MOV B,C; в регистр В записывается содержимое регистра С: (В)←(С),

где В и С – операнды.

Помни!!!: Код операции (команды), в нашем примере хранится только в 1-м байте любой команды (одно, двух, трех байтной).

В двухбайтной команде: в первом байте записывается код операции и один из операндов (операнда может и не быть), во втором – только операнд.

Примеры двухбайтных команд:

|

Б1 Б2 |

OUT A |

|

FB |

([FB])←(A). Из аккумулятора пересылаются данные в порт, адрес которого (FB) во 2-м байте команды (Б2).

Где:

OUT – код операции, А – первый операнд и FB – второй операнд.

Из аккумулятора (А) вывести информацию на устройство вывода с адресом FB.

Круглые скобки (…) - содержимое ЯП или устройства вывода/ввода;

Квадратные скобки [..] – адрес ЯП или устройства вывода/ввода.

|

Б1 Б2 |

MVI B |

|

7Bh |

(В)←7Вh. В регистр В заносится 8-ми разрядная (однобайтная) константа 7Вh 16-й системы счисления

.

В трехбайтной команде: в первом байте команды записывается код операции (КОП), во втором и третьем байтах операнды.

Пример:

|

Б1 Б2 Б3 |

LDA |

|

7F | |

|

8A |

(А)←([8A7F]).

Команда чтения из памяти (ЗУ). В аккумулятор записывается информация, которая храниться в ячейке памяти, адрес которой указан во втором и третьем байтах.

Помни!!!!: Только в первом байте любой команды (одно, двух, трех байтной)

записан КОП (код операции).

Исходная программа на языке ассемблер состоит из последовательности команд, которые называют также ассемблерными строками. Запись строки осуществляется в соответствии с некоторыми формальными правилами (как синтаксис и орфография в русском и др. языках).

Строка (предложение) делятся на несколько полей, разделенных одним и более пробелами:

поле метки;

поле мнемоники кода операции;

поле операнда;

поле комментария.

Таким образом, строка (команда) имеет следующий формат:

[метка] <мнемоника КОП> [операнд] ; [комментарий]

Где […] – необязательный элемент конструкции (команды).

<…..> - обязательный элемент конструкции (команды).

Поле метки начинается с первой позиции строки и представляет мнемоническую запись адреса команды.

Поле мнемоники КОП начинается после первого пробела строки и заканчивается одним или более пробелами. Является обязательным в команде (конструкции строки).

Поле операнда определяет информацию, над которой производятся действия.

Поле комментария начинается после символа ; Присутствие поля комментария в команде необязательно. Комментарии не влияют на результат трансляции.

Режимы адресации в МП

В МП используются четыре режима адресации:

Прямая адресация – код адреса в команде является исполнительным адресом обращения к памяти или устройству ввода вывода. Примеры:

|

STA |

|

79 |

|

8F |

В аккумулятор заносятся данные из ЯП, адрес которой во 2-м и 3-м байтах команды.

|

Б1 Б2 |

IN |

|

8B |

(A)←([8B])

В аккумулятор заносятся данные из устройства ввода, адрес которого во 2-м байте команды.

Регистровая адресация – это адресация, при которой операнд содержится в одном из регистров МП.

MOV A,B (A)←(B)

Содержимое 8-ми разрядного регистра В пересылается по внутренней шине данных МП в аккумулятор (А).

Непосредственная адресация – это адресация, при которой операнд находится в самой команде.

|

Б1 Б2 |

ADI |

|

7Eh |

(A)←(A)+7Eh

Константа во 2-м байте команды (7Eh) складывается с содержимым аккумулятора и результат сложения записывается в аккумулятор.

Регистровая косвенная адресация – это адресация, при которой адрес ячейки памяти с операндом хранится в регистровой паре H-L.

MOV A,M; (A)←([H-L])

В аккумулятор пересылается содержимое ячейки памяти, адрес которой храниться в регистровой паре H-L.

Помни: Скобки (….) обозначают содержимое ячейки памяти или регистра РОН и аккумулятора. Скобки […] адрес ячейки памяти или устройства ввода/вывода.

2-й учебный вопрос

Система команд

Рассмотрим систему команд на языке ассемблера.

Ассемблер - это программа, которая переводит последовательность команд с языка пользователя (ассемблера) в машинный код (код микропроцессора).

Система команд включает в себя следующие группы команд:

Команды пересылки данных.

Команды арифметических операций.

Команды логических операций.

Команды управления (безусловные и условные переходы).

Команды ввода и вывода данных.

Другие (вспомогательные) команды.

1. Команды пересылки данных

регистровая пересылка

|

Б1 |

MOV rd, rs |

Где: Б1 – байт команды (команда содержится в 1-м байте ЗУ);

rd – все регистры (B, C, D, E, H, L) и аккумулятор (A);

rs – все регистры (B, C, D, E, H, L) и аккумулятор (A).

Cодержимое регистра rs переносится в регистр rd, при этом содержимое регистра rs остается неизменным.

Пример команды на языке ассемблер:

MOV D, E ; (D)←(E)

пересылка константы

|

Б1 Б2 |

MVI r |

|

константа |

r – все регистры (B, C, D, E, H, L) и аккумулятор (A)

Пример команды на языке ассемблер:

MVI B, 8Dh ; (B)←8Dh

В регистр В пересылается константа 8Dh.

загрузка константы в пару регистров

|

Б1 Б2 Б3 |

LXI rr |

|

младший разряд, const | |

|

старший разряд, const |

rr – регистровая пара (B-C, D-E, H-L; PSW-аккумулятор и регистр признаков).

|

Б1 Б2 Б3 |

LXI B |

|

9A | |

|

8B |

Помни!!!: Если в коде операции команды (КОП) присутствует символ Х – команда «работает» с регистровой парой.

Если в коде операции команды (КОП) присутствует символ I – команда «работает» с константой.

Например:

КОП LXI – команда работает с регистровой парой и константой.

косвенная регистровая пересылка данных

|

Б1 |

MOV r, M |

|

Б1 |

MOV M , r |

Где: r- аккумулятор и РОН (регистр общего назначения);

М – мнемоническое обозначение регистровой пары H-L, в которой записан адрес ячейки памяти ЗУ;

(..) – содержимое 8- разрядной (однобайтной) ячейки памяти;

[..] – содержимое 16-ти разрядного (2-х байтного) адреса команды.

прямая загрузка

Пересылка из запоминающего устройства в аккумулятор.

|

Б1 Б2 Б3 |

LDA | |

|

младший разряд |

адрес ячейки памяти ЗУ | |

|

старший разряд | ||

загрузка памяти ЯП ЗУ прямая

|

Б1 Б2 Б3 |

STA | |

|

младший разряд |

адрес ячейки памяти ЗУ | |

|

старший разряд | ||

Арифметические и логические операции. Инкрементные и декрементные команды

2.1. Сложение содержимого аккумулятора с регистром r , где r регистры A, B, C, D, E, H, L.

|

Б1 |

ADD r |

Помни!!!: В командах арифметических и логических операций, а также инкрементных и декрементных командах формируются значения регистра признаков.

В этой команде изменяются признаки S, Z, P, AС, СY.

Например:

ADD A ; (A)←(A)+(A)

Разновидность команды:

Сложение содержимого аккумулятора с содержимым ЯП (косвенная адресация):

|

Б1 |

ADD M |

(A)←(A)+([H-L]), S, Z и др.

Сложение аккумулятора с константой:

|

Б1 Б2 |

ADI |

|

8-разрядная константа |

Например: ADI 7Bh ; (A)←(A)+7Bh, S, Z и др.

Помни: Символ «I» в командах означает работу с константой.

Вычитание содержимого регистра из аккумулятора

|

Б1 |

SUB r |

(A)←(A) - (r), S, Z и др.

В этой команде изменяются признаки S, Z и др.

SUB A; (A)←(A)-(A) в аккумуляторе ноль, следовательно, появляется нулевой признак (Z=1).

|

Б1 |

SUB M |

(A)←(A)- ([H-L]), S, Z и др.

|

Б1 Б2 |

SUI |

|

8-разрядная константа |

Декрементные команды (аналогично вычитающему двоичному счетчику)

|

Б1 |

DCR r |

|

Б1 |

DCR M |

|

Б1 |

DCX rr |

rr – регистровая пара (B-C, D-E, H-L).

Например:

DCX B; (B-C)←(B-C)-1

Помни: Символ «Х» в команде означает работу с регистровой парой.

Инкрементные команды (аналогично суммирующему двоичному счетчику).

Инкремент регистра

|

Б1 |

INR r |

Например: INR А; (A)←(A)+1 S, Z и др.

|

Б1 |

INR M |

Инкремент регистровой пары

|

Б1 |

INX rr |

Например: INX D; (D-E)←( D-E)+1

Логические операции (AND, OR, NOT,

).

).

3.1. Логическое умножение содержимого аккумулятора с константой

|

Б1 Б2 |

ANI |

|

константа |

Логические операции осуществляются поразрядно и без переноса в старший разряд.

Пояснение на примере.

ANI 0: (A)←(A)^ (0) В аккумулятор записывается ноль.

ANI FF ; В аккумуляторе остается содержимое аккумулятора.

|

Б1 |

ANA r |

|

Б1 |

ANA M |

Логическое сложение

|

Б1 Б2 |

ORI |

|

константа |

Рассмотрим примеры:

ORI FF; (A)←(FF)V(A)

ORI 0 (A)←(A)V0

|

Б1 |

ORA r |

|

Б1 |

ORA M |

Инверсия содержимого всех разрядов аккумулятора

|

Б1 |

CMA |

Рассмотрим пример: Пусть А=0. Что будет в аккумуляторе после выполнения команды CMA?

Сложение по модулю два константы с аккумулятором

|

Б1 Б2 |

XRI |

|

константа |

|

Б1 |

XRA r |

Например:

XRA

A ; (A)←(A)![]() (A)

В аккумулятор записываетсяноль.

(A)

В аккумулятор записываетсяноль.

3.5. Логическое сравнение аккумулятора с регистром (команды логического сравнения применяются перед командами условного перехода)

|

Б1 |

СMP r |

Арифметическое вычитание и формирование только признаков в регистре признаков (S, Z, P и др.).

Логическое сравнение аккумулятора с константой

|

Б1 Б2 |

СРI |

|

константа |

Помни:

Команды логического сравнения применяются, чтобы сформировать только признаки (S, Z, P, AС ) в регистре признаков перед выполнением команд условных переходов. Содержимое аккумулятора при этом не изменяется!

Команды управления (безусловный и условные переходы)

4.1. Команда безусловного перехода

|

Б1 Б2 Б3 |

JMP | |

|

младшие разряды |

Адрес перехода | |

|

старшие разряды | ||

Пример: JMP 8105h ; (Счетчик команд РС)←8105h

4.2. Команды условных переходов (JM, JNM, JZ, JNZ)

Все команды условного перехода 3-х байтные: в 1-м байте КОП, в 3- м и 2-м байтах команды адрес перехода.

Последовательность выполнения команды условного перехода: если условие КОП выполняется, то в PC заносится адрес перехода из 3-го и 2-ого байтов команды. Если условие КОП не выполняется, то к значению PC прибавляется 3, т.е. МР переходит к выполнению очередной команды.

Команда перехода, если минус:

|

Б1 Б2 Б3 |

JM | |

|

младшие разряды |

адрес перехода | |

|

старшие разряды | ||

(PC)←(РС)+3, если S=0

Команда перехода, если минус, т.е. если предыдущий результат отрицательный (S=1), то в PC заносится адрес 3- и 2- ого байтов команды и происходит переход по этому адресу. Если условие КОП не выполняется (S=0), то к значению PC прибавляется 3, т.е. МР переходит к выполнению очередной команды.

Пример команды:

Команда перехода, если ноль:

|

Б1 Б2 Б3 |

JZ | |

|

младшие разряды |

адрес перехода | |

|

старшие разряды | ||

(PC)←(РС)+3, если Z=0

Команда перехода, если не ноль:

|

Б1 Б2 Б3 |

JNZ | |

|

младшие разряды |

адрес перехода | |

|

старшие разряды | ||

(PC)←(РС)+3, если Z=1

Команды ввода и вывода данных.

Ввод и вывод данных организуется двумя способами:

Ввод и вывод данных только через аккумулятор. Данный способ обычно используется в восьмиразрядных системах. Он прост в технической реализации МП. В изучаемом нами МП применяется данный способ обмена.

Прямой доступ к памяти (ПДП). Тогда обмен информации между устройствами ввода, вывода и запоминающего устройства может осуществляться напрямую, минуя аккумулятор. Все персональные компьютеры и многие микроконтроллеры используют этот принцип. Он сложен в технической реализации, но обеспечивает большую пропускную способность.

5.1. Команда ввода данных

|

Б1 Б2 |

IN |

|

Адрес устройства ввода |

Пример команды:

IN INPORT1; (A)←([INPORT1]), где INPORT1символический адрес порта ввода.

Команда вывода данных

|

Б1 Б2 |

OUT |

|

Адрес устройства вывода |

OUT OUTPORT2 ; ([OUTPORT2])←(A)

Другие команды

6.1 Команды работы со стеком (стековой памятью).

Стековая память – область ОЗУ, предназначенная для временного хранения данных, в том числе и адресов возврата в основную программу при обращении к подпрограмме.

Обмен со стековой памятью осуществляется только парами регистров (В-С, D-E, H-L, PSW).

Для организации стековой памяти необходимо определить начальный адрес (вершину стека).

Примечание: в некоторых МПС начальный адрес стека определяется автоматически.

Для задания вершины стека используются два варианта команд:

1-ый вариант:

|

Б1 Б2

Б3 |

LXI | |

|

младший разряд |

Адрес регист- ровой пары | |

|

старший разряд | ||

SP – шестнадцатиразрядный указатель стека, т.е. в указателе стека

2-ой вариант:

|

Б1 |

SPHL |

(SP)←(H-L)

Запись содержимого регистровой пары в стековую память:

Команда записи регистровой пары в стековую память

-

PUSH rr

где rr – В-C, D-E, H-L, PSW.

Например:

PUSH В; Содержимое пары регистров В-С записывается в стековую память по адресу SP-1 и SP-2. После выполнения команды записи содержимого в стековую память в указателе стека (SP) изменяется адрес стековой памяти (уменьшается его значение на два: SP=SP-2).

Команда чтения содержимого стека в регистровую пару (чтение из стековой памяти)

-

РОР rr

где rr – В-C, D-E, H-L, PSW.

По этой команде содержимое стековой памяти (два байта) из ОЗУ записываются в одну из регистровых пар РОН или PSW. После выполнения команды содержимое указателя стека увеличивается на два SP=SP+2.

Например:

РОР B; Содержимое двух ячеек стековой памяти по адресу SP+1 и SP+2 записывается в пару регистров B-C, а указатель вершины стека после выполнения команды принимает значение SP=SP+2.

Команда обращения к подпрограмме (CALL).

Сложные программы, как правило, включают в себя подпрограммы, т.е. создается алгоритм основной программы и в основной программе используются команды обращения к подпрограмме.

Синтаксис команды обращения к подпрограмме

|

Б1 Б2

Б3 |

CALL | |

|

младшие разряды |

адрес ячейки памяти ЗУ с командой подпрогрпммы | |

|

старшие разряды | ||

([SP-2]) ←(CPH)возвр.

(SP)←(SP)-2 ; измен. адр. вершины стека.

(CP)←([< Б3>< Б2>]).

Последовательность выполнения команды обращения к подпрограмме CALL.

В стековую память записывается 16-ти разрядный адрес ячейки памяти возврата после выполнения подпрограммы (CPL)возвр. , (CPH)возвр.

В указатель счетчика команд (PC) заносится адрес первой ЯП команды подпрограммы с КОП ([<Б3><Б2>]). . Поскольку стековая память использована для хранения адреса возврата из подпрограммы в основную программу, то изменяется значение указателя вершины стека (уменьшается на 2, т.е. SP=SP-2).

Команда возврата из подпрограммы

|

Б1 |

RET |

(CPL) ← ([SP+1]), (запись в счетчик команд PC адреса

(CPH) ← ([ SP+2]) возврата в основную программу)

(SP)←(SP)+2, (изменяется адрес вершины стека )

В счетчик команд PC записывается содержимое стековой памяти по адресу ([SP+1]) и ([SP+2]), т.е. адрес возврата в основную программу.

После выполнения команды значение указателя стека SP увеличивается на 2, т.е. SP=SP+2.

Команда HLT – останов выполнения программы

|

Б1 |

HLT |

МП прекращает выполнение программы и ждет указаний.

Пустая команда

|

Б1 |

NOP |

Эта команда используется для резервирования ячеек при написании программы. МП никаких действий не выполняет, но осуществляет первый этап (чтение и дешифрование). Кроме того, команда может применяться при написании программы временной задержки (для изучаемого симулятора AVSIM85 время выполнения 1-ого этапа команды четыре секунды).

Работа с имитатором (симулятором) процессора Intel I8085.

Построение программы.

Этапы создания программы:

Разработка алгоритма программы и ее написание на языке ассемблер. Набор программы осуществляется только!!! в Блокноте или с использованием симулятора. Сохраняется программа в формате «все файлы» и имя программы – с расширением .asm. Например, testr3.asm.

Примечание: В редакторе Word или Word Pad программу не набирать, а только в Блокноте

Трансляция программы – перевод программы с языка ассемблера в код микропроцессора. В результате появляется файл с расширением .hex, т.е. файл с цифрами в шестнадцатеричной системе счисления.

Компоновка программы. Результат компоновки – объединение нескольких оттранслированных программ в одну, в результате мы получаем файл с расширением .obj.

Отладка программы.

Структура программы

Программа состоит из предложений. Каждое предложение имеет следующую структуру:

[метка] <мнемоника команды> [операнды]; [комментарии]

[] – не обязательное включение содержимого скобок в предложение

<> - обязательное наличие содержимого скобок в предложение

Поле метки: метка записывается с первой позиции и начинается обязательно с буквы.

Поле мнемоники: код операции (КОП) записывается после первой позиции.

Поле операнда: в этом поле записываются данные, которые обрабатываются в МП.

Поле комментария: комментарии записываются обязательно после точки с запятой (;). Если комментариев нет, точку с запятой ставить не обязательно. Если точка с запятой стоит в первой позиции, то строка транслятором воспринимается как комментарий.

Программа начинается с комментария, в котором записывается автор программы, название программы, какие микропроцессоры, микроконтроллеры и тактовая частота используются. Далее следуют директивы к транслятору.

В директивах записываются символические имена портов ввода и вывода, констант, команд присоединения и других команд.

Include – директива и после нее записываются имена файлов с расширением .asm.

Тело программы включает строки предложений, рассмотренные ранее.

Трансляция программы.

Для трансляции программы необходимо командной в строке, например, FAR или Total Commander, записать:

avmac85 <имя исходного файла.asm> si allpublic

Помни уголки < > не использовать при написании команды.

В результате формируются объектный файл и листинг:

<имя исходного файла>.obj

< имя исходного файла >.prn

Для проверки программы на наличие в ней ошибок необходимо раскрыть файл с расширением .prn , и в нем будет показано, в какой строке находится ошибка. Исправлять ошибки только в файле с расширением .asm.

Компоновка программы.

Для компоновки программы пользователю необходимо создать командный файл компоновки. После создания командного файла компоновки в командной строке набрать команду:

avlink @<имя файла>.lnk

В результате компоновки формируется файл с расширением .hex.

Подготовка файлов выходных данных.

Для ввода данных (имитация ввода данных) формируется файл исходный данных. Для организации файла создать файл с именем indat.ad. Для создания файла используют следующее сочетание клавиш – Shift+F4. Значения входных данных записываются в десятичной системе. Цифры разделяются либо пробелом, либо переводом строки. Для перевода десятичной системы счисления в шестнадцатеричную в командной строке записывают команду:

iotran db indat.dat indat.ad

Лекция

Особенности разработки программ двоичных счетчиков

Учебные вопросы:

1. Двоичные счетчики с заданной разрядностью, начальным (Qнач) и конечным (Qкон) значениями счета.

2. Построение счетчиков на двух регистрах.

3. Построение программы с управляющими сигналами.

4. Разработка программы счетчика табличным методом.

Двоичные счетчики с заданной разрядностью, начальным (Qнач) и конечным (Qкон) значениями счета.

Постановка задачи: разработать вычитающий четырехразрядный двоичный счетчик с параметрами:

Qнач.=5, Qкон=8

m – разрядность счетчика

Сmax=

![]()

Примечание: в аккумуляторе восемь разрядов. В четырехразрядном счетчике используются только четыре младших разряда, следовательно, необходимо отсечь старшие разряды. Для этого используется команда ANI 0Fh.

Алгоритм программы

Фрагмент программы:

Begin:

MVI C,Qn ; C=Qn Бл.1

M 2: MOV

A,C ; A=CБл.2

2: MOV

A,C ; A=CБл.2

OUT outport2 ; вывод Qi

DCR C ; C=C-1 Бл.3

MOV

A,C

MOV

A,C

ANI 0Fh Бл.4

MOV C,A

CPI

Qk

; (A-Qk)

в этой

CPI

Qk

; (A-Qk)

в этой

команде только меняются Бл.5

признаки S, Z, P

JZ Begin

JMP M2

END

В рассмотренной программе Cmax=![]() ,

,

где m=8, следовательно, Сmax не более 255 .

На практике применяются счетчики с Сmax> 255. Тогда могут применяться счетчики на двух регистрах.

Построение счетчиков на двух регистрах.

МП обладает аппаратной возможностью формирования признака нулевого результата только для одного регистра, а не для регистровой пары. Поэтому пользователю (разработчику программ) необходимо формировать признак нулевого результата на программном уровне.

Алгоритм программы

Фрагмент из программы

Delay:

LXI B, DEL ; пересылается константа

в регистровую пару В-С

M3:

NOP ; пустая команда для увеличения

времени цикла

NOP

MOV A,C

ORA B ; (A)←(A)V(B)

JNZ M3

JMP Mi ; метка основной программы

END

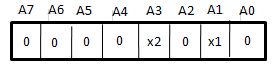

3.Построение программы с управляющими сигналами

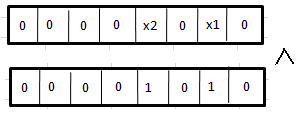

Если МПС управляет устройством, то на вход МПС поступает сигнал, по результатам которого формируется управляющий сигнал. Пусть двоичный счетчик управляется двумя сигналами, а именно, сигнал Х1 – сброс счетчика в нулевое состояние (начальное) и Х2 – останов счетчика.

Примечание: Эти сигналы используются в программной реализации проектируемого устройства в курсовой и лабораторной работах.

Управляющий сигнал обеспечивает сброс счетчика в начальное состояние, если Х1=0 в разряде регистра А1 (аккумулятор), а Х2=0 в разряде регистра А3 (аккумулятор) : обеспечивает останов счета. Cигналы управления вводятся в аккумулятор МП побайтно.

Рассмотрим последовательность применения управляющих сигналов.

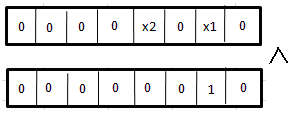

а) выделение сигнала Х1. Для этого применим команду логического умножения (конъюнкция) АNI X, где Х – число (соnst), позволяющее выделить любой разряд (ы) регистра (аккумулятора). В нашем примере константа 02 (ANI 02), которая позволяет выделить разряд сигнала Х1.

![]()

![]()

б) определение значения разряда (1 или 0) управляющего сигналаХ1: применяем команды JZ или JNZ.

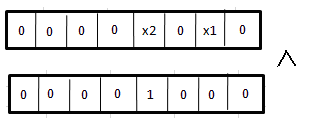

Аналогично для сигнала Х2:

а) выделение сигнала Х2 (сонстанта 08):

![]()

б) определение значения разряда сигнала Х2: применяем команды JZ или JNZ.

Пусть Х1 =Х2=1, то есть рассмотрим ситуацию, когда счетчик работает без воздействия управляющих сигналов:

![]()

![]()

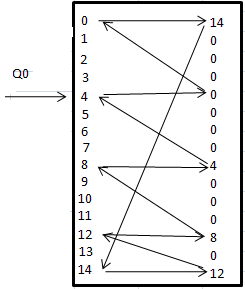

4.Разработка программы счетчика табличным методом.

Сущность метода построения счетчика: в памяти МПС на программном уровне формируется таблица (одномерная), в которой по адресу, соответствующему текущему состоянию, записано число (в памяти), которое соответствует следующему состоянию счетчика.

Пример: разработать счетчик табличным методом с произвольным порядком смены состояний.

Пусть счетчик имеет начальное состояние Q0 = 4

4 →0 →14→12 →8

NAT какой-нибудь адрес.

NAT +

Фрагмент программы:

MOV A,C ;(А)← (C)

OUT OUTPORT ;вывод значений счетчика

LXI H,NAT ;загружаем данные таблицы

MVI B,0 ;обнуляем регистр В

DAD B ;(H-L) ← (H-L)+(B-C)

MOV A,M ;(A) ←([H-L])

MOV C,A ;(C) ←(A)

JMP M1

NAT: db 0Еh,0h,0h,0h,0h,0h,0h,0h,4h,0h,0h,0h,8h

include stack.asm

end