- •2. Элементная база микроэвм

- •2.1. Состав элементов для построения микроЭвм

- •2.2. Однокристальные микропроцессоры к1810вм86/к1810вм88

- •2.2.1. Аппаратный интерфейс

- •2.2.2. Функциональный смысл внешних сигналов

- •2.2.3. Структура и принцип действия

- •2.2.4. Временные диаграммы функционирования

- •2.2.5. Логическая организация памяти

- •2.2.6. Вычисление физического адреса памяти

- •2.2.7. Сегментная структура памяти

- •2.3. Генератор тактовых импульсов к1810гф84

- •2.4. Шинные буферы к1810ва86

- •2.5. Элементы памяти

- •2.5.1. Элементы постоянной памяти

- •2.5.2. Элементы оперативной памяти

- •2.6. Порты ввода/вывода

- •2.6.1. Порт ввода/вывода к1810ир82

- •2.6.2. Порт ввода/вывода к589ир12

- •2.6.3.Программируемый параллельный интерфейс кр580вв55а

- •Режим 0

- •Режим 1

- •Режим 2

2.2.5. Логическая организация памяти

В связи с использованием механизма сегментации памяти в МП ВМ86/ВМ88 положение каждой ячейки определяется сегментом, в котором она находится, а также смещением относительно начала этого сегмента (см. рис.2.3). Следовательно, с логической точки зрения положение ячейки может быть описано базовым адресом сегмента segment и смещением относительно начала этого сегмента offset. Эта пара чисел называется логическим адресом ячейки памяти и записывается в виде segment:offset. База сегмента segment всегда хранится в сегментном регистре, а смещение offset чаще всего берется из регистров указателей адреса IP, SP, BP, SI, DI, либо вычисляется в соответствии со способом адресации операндов, указанным в команде.

Таким образом, логический адрес состоит из двух беззнаковых 16-битных значений и является двойным словом.

Программа всегда оперирует логическими адресами. При обращении к памяти шинный интерфейс из заданного логического адреса ячейки памяти вычисляет ее физический адрес, который и выдается на шину адреса.

.

2.2.6. Вычисление физического адреса памяти

Физический адрес представляет собой 20-битное число в диапазоне 0...FFFFFh, которое однозначно определяет положение каждого байта в пространстве памяти объемом 1 мбайт.

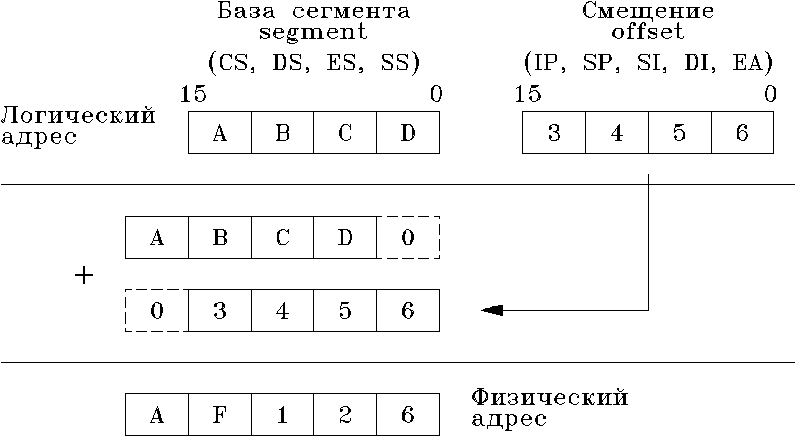

При вычислении физического адреса база сегмента segment сдвигается влево на 4 бита и складывается со смещением offset в соответствии со схемой, приведенной на рис.2.5.

Рис. 2.5. Вычисление физического адреса

Перенос из старшего разряда, возникающий при суммировании, игнорируется. Это приводит к кольцевой организации памяти, при которой за ячейкой с максимальным адресом FFFFFh следует ячейка с нулевым адресом. Аналогичную кольцевую организацию имеет и каждый сегмент.

Кроме того, на рис.2.5 указаны различные источники компонент логического адреса, которые могут использоваться для вычисления физического адреса. При этом обозначение EA соответствует эффективному адресу, вычисляемому в соответствии с указанным в команде способом адресации операндов.

При различных типах обращения к памяти компоненты логического адреса выбираются из различных источников. Допустимые варианты источников приведены в табл. 2.3.

Из анализа этой таблицы следует, что команды всегда выбираются из текущего сегмента программного кода по логическому адресу CS:IP, стековые операции всегда выполняются в текущем сегменте стека по логическому адресу SS:SP, а при обращении к данным возможны различные варианты.

Таблица 2.3

Источники компонент логического адреса.

-

Тип обращения к памяти

Сегмент

(по умолчанию)

Вариант

сегмента

Смещение

Выборка команды

CS

Нет

IP

Стековая операция

SS

Нет

SP

Обращение к данным

DS

CS,ES,SS

EA

Обращение к

цепочкеисточнику

DS

CS,ES,SS

SI

Обращение к

цепочкеприемнику

ES

Нет

DI

Обращение к данным

через регистр BP

SS

CS,DS,ES

EA

Как правило, по умолчанию считается, что данные находятся в основном сегменте данных, и обращение к ним осуществляется по логическому адресу DS:EA. Однако, путем явного указания сегмента в описании операнда можно обратиться к данным и из любого другого сегмента.

Разновидностью данных, обрабатываемых МП ВМ86/ВМ88, являются цепочки (строки). При обработке таких данных, одна команда может оперировать с целой цепочкой элементов. При этом элементы цепочки-источника по умолчанию выбираются из основного сегмента данных по логическому адресу DS:SI, но могут выбираться и из любого другого сегмента. Цепочкаприемник может находиться только в дополнительном сегменте данных, и обращение к ее элементам осуществляется по логическому адресу ES:DI.

Если в описании операнда используется регистр BP, то по умолчанию считается, что этот операнд находится в сегменте стека. Однако, в этом случае стековый принцип выборки данных игнорируется, и обращение к сегменту стека осуществляется как к ОЗУ с произвольным доступом. Это обеспечивает большую гибкость при обращении к данным, находящимся в стеке.