- •8)Фотоэлектрические чувствительные элементы

- •12. Магнитный усилитель

- •14.Электронные усилители

- •Структура усилителя

- •15.Тса типа электромагнит.Виды эм. Принцип действия.

- •Другие классификации

- •16. Основные характеристики электромагнитов. Свойства эм статические и динамические .

- •17. Тса оптоэлектронного вида

- •18. Бесконтактные устройства обработки информации

- •19. Транзисторы в системах автоматики . Виды, обозначения.

- •Биполярный транзистор

- •20. Цифровые устройства в системах автоматики.

- •21. Элементы логики

- •Логические функции двух переменных

- •22.23 Триггеры. Виды, обозначение. Классификация.

- •24.Rs-триггер

- •Rs-триггер синхронный

- •25. Jk-триггер

- •26. D-триггер d-триггеры

- •D-триггер синхронный

- •27.T-триггер t-триггеры

- •Т-триггер асинхронный

- •T-триггер синхронный

- •28.Регистры.

- •29.Счетчики

- •30.Шифраторы дешифраторы

- •31. Ацп и цап

- •1)Коммутационные аппараты ручного ввода информации

- •1.1. Аппараты для коммутации силовых цепей

- •1.2. Аппараты для коммутации цепей управления

- •33)Контрольные устройства (датчики)

- •34. Выходные устройства автоматики

- •35. Контактные узлы.

- •36. Программируемый контроллер. Классификация (общая).

- •6.2. Особенности плк в сравнении с традиционными тса и эвм

- •6.3. Классификация плк, как основных компонентов птк

- •37. Контроллеры на базе персональных компьютеров (пк)

- •38. Локальные программируемые контроллеры.

- •39. Сетевые комплексы контроллеров.

- •40. Плк для маломасштабных распределенных систем управления.

- •41. Плк для полномасштабных распределенных асу тп.

- •42. Структурная схема пк. Основные элементы пк.

- •43. Функционально-конструктивная схема модульного плк.

- •44. Архитектура и общая организация модульного плк

- •45.Устройства программирования плк (программаторы)

- •46. Архитектура взаимодействия открытых систем osi (Уровни модели взаимодействия).

- •7. Прикладной уровень

- •48-49. Микропроцессор и флаги

30.Шифраторы дешифраторы

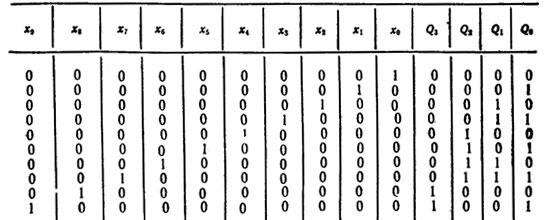

Шифраторы и дешифраторы. Шифратором, или кодером называется комбинационное логическое устройство для преобразования чисел из десятичной системы счисления в двоичную. Входам шифратора последовательно присваиваются значения десятичных чисел, поэтому подача активного логического сигнала на один из входов воспринимается шифратором как подача соответствующего десятичного числа. Этот сигнал преобразуется на выходе шифратора в двоичный код. Согласно сказанному, если шифратор имеет n выходов, число его входов должно быть не более чем 2n. Шифратор, имеющий 2n входов и n выходов, называется полным. Если число входов шифратора меньше 2n, он называется неполным.

Рассмотрим работу шифратора на примере преобразователя десятичных чисел от 0 до 9 в двоично-десятичный код. Таблица истинности, соответствующая этому случаю, имеет вид

Так как число входов данного устройства меньше 2n = 16, имеем неполный шифратор. Используя таблицу для Q3, Q2, Q1 и Q0, можно записать следующие выражения:

Полученная

система ФАЛ характеризует работу

шифратора. Логическая схема устройства,

соответствующая системе приведена на

рисунке ниже.

Полученная

система ФАЛ характеризует работу

шифратора. Логическая схема устройства,

соответствующая системе приведена на

рисунке ниже.

Логическая схема шифратора десятичных чисел

Нетрудно

заметить, что в шифраторе рассматриваемого

типа сигнал, подаваемый на входхо,

не используется. Поэтому отсутствие

сигнала на любом из входов хо,

... , х1 трактуется

схемой как наличие на входе нулевого

сигнала.

Нетрудно

заметить, что в шифраторе рассматриваемого

типа сигнал, подаваемый на входхо,

не используется. Поэтому отсутствие

сигнала на любом из входов хо,

... , х1 трактуется

схемой как наличие на входе нулевого

сигнала.

Основное применение шифратора в цифровых системах — это введение первичной информации с клавиатуры. При нажатии любой клавиши на соответствующий вход шифратора подается сигнал лог. 1, который и преобразуется на выходе в двоично-десятичный код. Вариант устройства ввода информации показан на рисунке ниже.

Устройство ввода информации с клавиатуры

Дешифратором, или декодером называется комбинационное логическое устройство для преобразования чисел из двоичной системы счисления в десятичную. Согласно определению дешифратор относится к классу преобразователей кодов. Здесь также понимается, что каждому входному двоичному числу ставится в соответствие сигнал, формируемый на определенном выходе устройства. Таким образом,

дешифратор выполняет операцию, обратную шифратору.

Если число адресных входов дешифратора n связана с числом его выходов mсоотношением m = 2n, то дешифратор называют полным. В противном случае, т.е. еслиm < 2n, дешифратор называют неполным.

Поведение дешифратора описывается таблицей истинности, аналогичной таблице истинности шифратора (см.табл. выше), только в ней входные и выходные сигналы меняются местами. В соответствии с данной таблицей, так как выходной сигнал равен 1только на одном единственном наборе входных переменных, т.е. для одной конституенты единицы, алгоритм работы дешифратора описывается системой уравнений вида

и

так далее, где Qi —

значение логической переменной на i-м

входе устройства.

В общем виде эта система имеет вид

xi = ( Q3Q2Q1Q0 ) i

где xi — сигнал на i-м выходе дешифратора; (Q3Q2Q1Q0) i — конституента единицы, соответствующая двоичному коду i-й десятичной цифры.

Нетрудно заметить, что ФАЛ дешифратора

отличается

от ФАЛ мультиплексора

отличается

от ФАЛ мультиплексора

только

наличием в последней дополнительного

множителя, соответствующего значению

сигнала на информационном входе D.

Поэтому при D =

1 демультиплексор функционирует как

дешифратор. Обратное преобразование

дешифратора в демультиплексор требует

введения вспомогательных ЛЭ 2И, выполняющих

операцию логического умножения между

общим сигналом информационного входа D и

соответствующим логическим произведением

адресных сигналов (Q3Q2Q1Q0).

Схема построенного таким образом

демультиплексора приведена на

рисунке ниже, а.

Реализация демультиплексора (а) и мультиплексора (б) с использованием дешифратора

Используя

дешифратор, можно построить и схему

мультиплексора.

Для этого схему (см.рис.

, а)

необходимо дополнить выходным ЛЭ4 ИЛИ

(рис.

,б).

Используя

дешифратор, можно построить и схему

мультиплексора.

Для этого схему (см.рис.

, а)

необходимо дополнить выходным ЛЭ4 ИЛИ

(рис.

,б).

При разработке ИС нашло применение несколько логических структур дешифратора. Их основное отличие состоит в быстродействии и числе используемых элементарных ЛЭ.

Наиболее быстродействующим и в то же время самым сложным является дешифратор, непосредственно реализующий систему ФАЛ. Такой дешифратор называетсяодноступенчатым или параллельным. Его структурная схема аналогична схеме демультиплексора (см. рис. выше, б) при условии D = 1.

Полагая, что для реализации обработки одного входного логического сигнала требуется некоторая условная единица аппаратных средств, число единиц этих аппаратных средств для n-разрядного дешифратора определяется выражением

N1 = n2n

Условное графическое изображение дешифратора

Условное

графическое изображение дешифратора

соответствует ИС двоично-десятичного

дешифратора типа 564ИД1.

Если при проектировании основным требованием является простота схемного решения, находят применение другие структуры дешифраторов. Однако упрощение структуры достигается за счет падения быстродействия.

Микросхемы дешифраторов часто снабжаются входом разрешения работы Е (входом стробирования). Наличие этого входа позволяет на основе готовых ИС при необходимости увеличения разрядности входного кода строить структуры дешифраторного дерева.

Используя структуру, приведенную ниже, на основе двоично-десятичных дешифраторов можно построить полный дешифратор 4-разрядного двоичного кода.

Схема полного двоичного дешифратора на базе двух двоично-десятичных дешифраторов