Министерство образования и науки РФ

Федеральное агентство по образованию

Саратовский государственный технический университет

ИЗУЧЕНИЕ СХЕМ,

ПОСТРОЕННЫХ С ИСПОЛЬЗОВАНИЕМ

ЛОГИЧЕСКОГО ЭЛЕМЕНТА «И-НЕ»

Методические указания

к лабораторной работе по курсу

"Физические основы электроники"

для студентов специальности 180500

направления 654500

Электронное издание локального распространения

Одобрено

редакционно-издательским советом

Саратовского государственного

технического университета

Саратов 2006

Все права на размножение и распространение в любой форме остаются за разработчиком.

Нелегальное копирование и использование данного продукта запрещено.

Составители: Фурсаев Михаил Александрович,

Беляев Виктор Иванович

Под редакцией М.А.Фурсаева

Рецензент А.А.Гурьянов

410054, Саратов, ул. Политехническая, 77, Научно-техническая

библиотека СГТУ

тел.: 52-63-81, 52-56-01

http://lib.sstu.ru

Регистрационный

номер 060253Э

© Саратовский государственный

технический университет, 2006

Целью лабораторной работы является изучение возможных состояний логического элемента «И-НЕ» и схем, построенных с использованием этого элемента.

ОСНОВНЫЕ ПОНЯТИЯ

Современная информатика оперирует двумя видами переменных: числом и логическими переменными. Числа дают информацию о количественных показателях объекта. Над ними производят арифметические операции. Логические переменные показывают принадлежность объекта к определённому классу состояния. Они могут принимать одно из двух состояний: «истинно» или «ложно», т.е. «1» или «0» при использовании двоичного способа представления информации. Такая информация представляется в виде импульсных сигналов положительной полярности двух уровней: низкого («0») и высокого («1»). Её отработка осуществляется с помощью логических операций при использовании электрических схем, называемых логическими элементами. В современной информационной технике они выполняются в виде микросхем. Наименование логического элемента определяется операцией, которую он производит.

Имеются три основные логические операции

-

Операция «ИЛИ» - логическое сложение.

F=x1+x2+…….+xn.

Функция F=1, если хотя бы одна из независимых переменных (x1 ,x2 ,……. xn.) равна единице.

-

Операция «И» - логическое умножение.

F=x1*x2*…….*xn.

Функция F=1, если все независимые переменные равны единице.

-

Операция «НЕ» - логическое отрицание или инверсия.

F = x.

= x.

Функция F=1 при x=0 и F=0 при x=1.

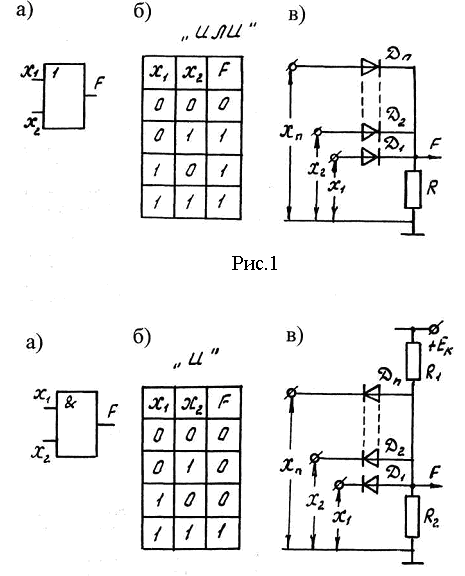

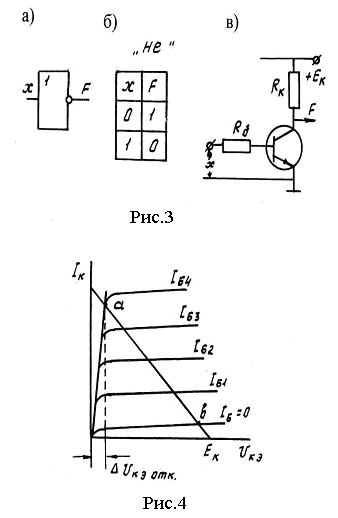

На рис. 1 – 3 представлены условные обозначения логических элементов «ИЛИ», «И», и «НЕ», таблицы истинности соответствующих операций, а также электрические схемы на диодах и биполярном транзисторе, с помощью которых реализуются эти операции. Для простоты на рис. 1 и 2 условные обозначения и таблицы истинности приведены для двухвходовых элементов.

Рис. 2

Нетрудно показать, что приведённые схемы обеспечивают выполнение перечисленных выше операций. Действительно, при отсутствии на входах схемы рис. 1.в сигнала все диоды будут находиться в закрытом состоянии и на резисторе R падение напряжения равно нулю. F=0. При подаче хотя бы на один вход схемы сигнала положительной полярности диод, установленный на этом входе, перейдёт в открытое состояние, через него и последовательно включённый с ним резистор R будет протекать ток, падение напряжения на резисторе будет отличаться от нуля, F=1.

В схеме рис.2.в через резистор R2 будет протекать ток, и с этого резистора будет сниматься напряжение ER2 / (R1+R2), то есть F=1, когда катоды всех диодов будут под положительным потенциалом, а, следовательно, все диоды будут закрыты. Если хотя бы на одном входе схемы сигнал отсутствует, соответствующий диод открывается, и через него будет протекать ток в обход резистора R2, поскольку сопротивление резистора много больше сопротивления открытого диода. Падение напряжения на R2 равно нулю, F=0.

Транзистор типа n-p-n в схеме рис. 3.в работает в ключевом режиме. При подаче на вход схемы сигнала положительной полярности он будет находиться в открытом состоянии, т.е. в точке «а» на его выходной характеристике, представленной рис. 4. Этой точке соответствует очень малая величина напряжения коллектор – эмиттер, которое является выходным схемы, F=0. При отсутствии на входе сигнала транзистор закрывается. Этому режиму соответствует точка «в» на выходной характеристике. С выхода схемы снимается напряжение, практически равное +Eк, т.е. F=1.

Логические элементы выпускаются в виде серий. Элементы каждой серии, выполняющие различные операции, могут сопрягаться в сложную схему комбинационного логического устройства. Элементы серии создаются на базе схемы основного элемента, который обычно выполняет операции «ИЛИ-НЕ» или «И-НЕ».

F =x1+x2+…….+x4,

=x1+x2+…….+x4,

F =x1*x2*…….*x4.

=x1*x2*…….*x4.

Условное обозначение элементов «ИЛИ-НЕ» и «И-НЕ» и их таблицы истинности представлены на рис. 5 и 6. Схемы, реализующие эти логические операции, по существу представляют собой последовательное соединение схем, выполняющих операции соответственно, «ИЛИ» - «НЕ» и «И» - «НЕ».

При построении комбинационных логических устройств используется алгебра логики. Она определяет следующий порядок действий: сначала выполняется операция “НЕ”, затем “И” и, наконец, “ИЛИ”. Операций вычитания и деления в алгебре логики нет, а для логических сложения и умножения действуют переместительный и сочетательный законы. Например, для логических переменных X, Y, Z.

X + Y + Z = X + Z + Y = Y + X + Z.

XYZ = XZY = YXZ.

X + Y + Z = X + (Y + Z) = (X + Y) + Z.

XYZ = X (YZ) = (XY) Z.

В случае одной переменной можно осуществлять операции при использовании следующих тождеств, которые легко проверяются.

X + X = X; (1) X · X = X; (5)

X

+

![]() = 1; (2) X

·

= 1; (2) X

·

![]() = 0; (6)

= 0; (6)

X + 0 = X; (3) X · 0 = 0; (7)

X + 1 = 1; (4) X · 1 = X; (8)

![]() = Х (9).

= Х (9).

Весьма полезными являются тождества, называемые формулами де Моргана

![]() ,

(10)

,

(10)

![]() .

(11)

.

(11)

Логические элементы «ИЛИ-НЕ» и «И-НЕ» считаются основными, поскольку при их соединении по определённой схеме можно обеспечить выполнение простейших логических операций. В результате существенно сокращается номенклатура логических элементов. На рис. 7 представлены схемы на элементах «И-НЕ», реализующие операции «НЕ», «И» и «ИЛИ», что проверяется с помощью приведённых выше тождеств.

Для схемы рис. 7.а последовательное использование (10) и (11) даёт

F = хх = х + х = х,

т.е. эта схема реализует операцию «НЕ».

Для схемы рис.7.б согласно (9)

F = х1х2 = х1х2 = х1х2.

Схема реализует операцию «И».

Для схемы рис.7.в последовательное использование (10) и (9) даёт

F

=

![]() = х1

+ х2.

= х1

+ х2.

Схема реализует операцию «ИЛИ».

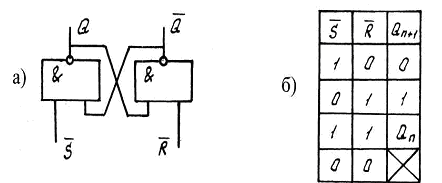

С использованием элементов «И-НЕ» и «ИЛИ-НЕ» можно построить триггеры, устройства, имеющие два устойчивых состояния: «1» и «0». Перевод из одного устойчивого состояния в другое осуществляется при подаче определённого входного сигнала. Благодаря этому свойству триггер является устройством для хранения одного бита информации.

Триггеры

характеризуются большим разнообразием.

Однако, как правило, они имеют два выхода:

прямой - Q

и инверсный -

![]() .

Состояние триггера определяется по

информации на прямом выходе: состояние

«1» соответствует Q

= 1,

.

Состояние триггера определяется по

информации на прямом выходе: состояние

«1» соответствует Q

= 1,

![]() = 0; состояние «0» соответствует Q

= 0,

= 0; состояние «0» соответствует Q

= 0,

![]() = 1.

= 1.

Простейшим является асинхронный RS-триггер, схема которого с использованием элементов «И-НЕ» приведена на рис.8.а. Он имеет два информационных входа S и R. По входу R осуществляется установка триггера в состояние «1», по входу S происходит его перевод в состояние «0». Триггер переходит из одного состояние в другое непосредственно после подачи входного сигнала. Поэтому он называется асинхронным. Возможные состояния асинхронного RS – триггера представлены в таблице на рис.8.б. Символ Qn означает состояние триггера до поступления входной информации, Qn + 1 - его состояние после поступления этой информации.

Рис. 8

Таблица состояний асинхронного RS – триггера на элементах «И-НЕ» проверяется при использовании таблицы истинности этого элемента, из которой видно, что при логическом «0» хотя бы на одном входе элемента «И-НЕ» на его выходе устанавливается логическая «1». Поэтому, при появлении «0» на выходе одного из логических элементов триггера на выходе этого элемента и соответствующем выходе триггера создаётся «1». Легко убедиться, что при логических «1» на обоих входах триггера (третья строка таблицы состояний) может быть как состояние «1», так и состояние «0». Из этого следует, что при подаче такой информации состояние триггера сохраняется. Например, если до подачи двух логических «1» триггер находится в состоянии «0», то и после их подачи его состояние не изменится.

Асинхронный RS – триггер на элементах «И-НЕ» не допускает наличия логических «0» одновременно на обоих входах. Действительно, в данном случае в соответствие с таблицей истинности элемента «И-НЕ» на каждом входе триггера должны установиться две логических «1», а это состояние не совпадает ни с одним из устойчивых состояний, о которых говорилось выше. Запрещение наличия входной информации S = R = 0 в таблице состояния отмечено соответствующим знаком.