- •Оглавление

- •Часть 1

- •Введение

- •Современные плис фирмы xilinx:серия virtex

- •Введение

- •Краткая классификация современных микросхем фирмы xilinx

- •Плис fpga

- •Отличительными системными особенностями являются:

- •Процесс конфигурации

- •Потребление энергии

- •Корпуса933

- •Серия Virtex

- •Серия virtex

- •Семейство Virtex-II

- •Семейство Virtex-II Pro

- •Семейство Virtex-4

- •Семейство Virtex-5

- •Серия Spartan

- •Семейство SpartanXl

- •Семейство Spartan-II

- •Семейство Spartan-iie

- •Семейство Spartan-3/3l

- •Плис фирмы Xilinx: семейство SpartanTm-3

- •Обзор архитектурных особенностей

- •Блоки ввода/вывода (бвв)

- •Конфигурируемые Логические Блоки (клб)

- •Блочная память

- •Блоки умножителей

- •Цифровые блоки управления синхронизацией

- •Линии связи

- •Конфигурирование в устройстве

- •Архитектура плис Spartan-6

- •Slice Spartan-6

- •Блочная память. (Block ram)

- •Потребляемая мощность плис. Эксперимент.

- •Практический эксперимент

- •Расчет потребляемого тока плис. Xilinx Power Estimator (xpe)

- •Xilinx xPower

- •Результат

- •Xilinx Documentation Navigator

Серия Virtex

Выпуск микросхем серии Virtex начат в октябре 1998 года.

Первое семейство микросхем (Семейство Virtex2.5В) серии Virtex включает в себя кристалл ёмкостью 1 млн. системных вентилей. В кристалл встроены блоки памяти, каждый ёмкостью 4кБит, и блоки управления синхронизацией (DLL). Микросхемы поддерживают большинство однополюсных сигнальных стандартов ввода-вывода (до 17 стандартов). По сравнению с предыдущей серией (XC4000) КЛБ в ПЛИС семейства Virtex в 2 раза больше. Системные частоты до 200 МГц

Второе поколение ПЛИС серии Virtex - семейство Virtex-Eбыло выпущено в октябре 1999 года. В семейство входят кристаллы ёмкостью до 3.2 млн. системных вентилей, добавлена поддержка дифференциальных стандартов ввода-вывода, в 2 раза увеличено количество блоков памяти. Увеличено быстродействие: ПЛИС семейства Virtex-E могут работать на системных частотах до 320 МГц.

Третье поколение ПЛИС серии Virtex - семейство Virtex-IIбыло выпущено в начале 2000 года. ПЛИС семейства Virtex-II реализуют новую идеологию Platform FPGA, подразумевающую что ПЛИС становится основным компонентом цифрового устройства. На одной микросхеме семейства возможно создать систему, содержащую все основные элементы цифрового устройства - простая "логика" + память + процессор, логической ёмкостью до 8 млн. системных вентилей. В отличии от предыдущих семейств серии Virtex, в серии Virtex-II блок памяти имеет ёмкость 18кБит, имеются встроенные блоки умножителей 18x18 и цифрового контроля импеданса блоков ввода-вывода. Увеличено количество поддерживаемых стандартов ввода-вывода, расширена функциональность модулей управления синхронизацией, увеличена в 2 раза логическая ёмкость КЛБ. Кристаллы способны работать в системах с частотой до 420 Мгц.

Четвёртое поколение ПЛИС серии Virtex - семейство Virtex-II Pro. Архитектура основана на архитектуре семейства Virtex-II, но добавились блоки процессора PowerPC-405, а также блоки трансиверов со скоростью передачи данных 3.125 ГБит/с. Повышено внутреннее быстродействие элементов кристалла.

Семейство Virtex-4– ПЛИС фирмы Xilinx с архитектурой FPGA последнего поколения. Инновационная ASMBL-архитектура (Advanced Silicon Modular Block) является уникальной в индустрии программируемой логики. Основу архитектуры кристалла Virtex-4 составляют улучшенные конфигурируемые логические блоки (КЛБ), которые можно найти во всем семействе Virtex: Virtex, Virtex-E, Virtex-II, Virtex-II Pro, Virtex-II ProX, что обеспечивает совместимость существующих проектов снизу-вверх. Комбинируя широким многообразием свойств, семейство Virtex-4 расширяет возможности программируемой логики и является мощной альтернативой заказным СБИС (ASIC).

Семейство Virtexпредставлено девятью типами кристаллов, содержащими от 384 до 6 144 конфигурируемых логических блоков (соответственно от 50 000 до 1 000 000 системных вентилей), которые производятся по технологии 0,22 мкм с пятислойной металлизацией.

Характерными особенностями семейства Virtexявляются:

высокая производительность, допускающая реализацию проектов с системными частотами до 200 МГц;

применение четырех специальных схем цифровой автоподстройки задержек (DLL), выполняющих функции умножения, деления и сдвига фаз тактовых частот, обеспечивает расширенные возможности управления синхронизацией;

использование четырех глобальных сетей предоставляет возможность распределения сигналов синхронизации внутри кристаллов с малыми разбегами фронтов;

наличие двух видов внутренней оперативной памяти: распределенной DistributedRAM, реализуемой на базе четырехвходовых таблиц преобразования(LookUp Table -LUT) конфигурируемых логических блоков (ConfigurableLogicBlock-CLB), и встроенной блочной памятиBlockSelectRAM, которая может быть организована как синхронное двухпортовое ОЗУ;

возможность реализации быстрых внутренних интерфейсов к внешним высокопроизводительным элементам памяти (ОЗУ или ПЗУ);

применение специальной логики ускоренного переноса для выполнения высокоскоростных арифметических операций;

специальная поддержка реализации умножителей;

наличие цепочек каскадирования обеспечивает возможность реализации функций с большим количеством входных переменных;

наличие внутренних шин с тремя состояниями;

полная поддержка протокола периферийного сканирования в соответствии со стандартом IEEEStd1149.1;

совместимость со стандартами PCI3,3 В 66 МГц;

поддержка функции Hoti-swap.дляCompactPCI;

неограниченное количество циклов загрузки конфигурируемых данных;

четыре режима конфигурирования ПЛИС (Slave-serial, Master-serial, SelectMAP, Boundaiy-scan mode);

напряжение питания ядра кристалла составляет 2,5В.

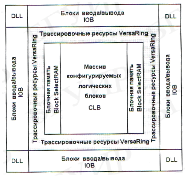

Основу архитектуры кристаллов Virtexсоставляет массив конфигурируемых логических бликовCLB, окруженных программируемыми бликами ввода/вывода ЮВ. Кроме того, в нее входят схемы цифровой автоподстройки задержекDLLи блоки выделенной памятиBlockSelectRAM. Все соединения между основными архитектурными элементами ПЛИС осуществляются с помощью иерархической структуры трассировочных ресурсов. Архитектура кристаллов семействаVirtexпредставлена на рисунке.

Рисунок 4

Конфигурируемый логический блок ПЛИС семейства Virtexсостоит из двух секций, каждая из которых включает в себя две однотипные логические ячейки (Logic,Cell,LC). В состав логической ячейки входит четырехвходовый функциональный генератор (таблица преобразований), триггерный элемент и логика ускоренного переноса. Кроме того, конфигурируемый логический блок содержит дополнительную логику, позволяющую конфигурировать функциональные генераторы для реализации функций пяти и шести переменных.

Основными элементами иерархической структуры трассировочных ресурсов являются: трассировочные ресурсы общего назначения, включающие главные трассировочные матрицы (GeneralRoutingMatrix-GRM) и коммутационные цепи различного типа, локальные трассировочные линииVersaBlock, окружающие каждый конфигурируемый логический блок, и дополнительные трассировочные ресурсы для коммутации блоков ввода/выводаVersaRing.