- •Оглавление

- •Часть 1

- •Введение

- •Современные плис фирмы xilinx:серия virtex

- •Введение

- •Краткая классификация современных микросхем фирмы xilinx

- •Плис fpga

- •Отличительными системными особенностями являются:

- •Процесс конфигурации

- •Потребление энергии

- •Корпуса933

- •Серия Virtex

- •Серия virtex

- •Семейство Virtex-II

- •Семейство Virtex-II Pro

- •Семейство Virtex-4

- •Семейство Virtex-5

- •Серия Spartan

- •Семейство SpartanXl

- •Семейство Spartan-II

- •Семейство Spartan-iie

- •Семейство Spartan-3/3l

- •Плис фирмы Xilinx: семейство SpartanTm-3

- •Обзор архитектурных особенностей

- •Блоки ввода/вывода (бвв)

- •Конфигурируемые Логические Блоки (клб)

- •Блочная память

- •Блоки умножителей

- •Цифровые блоки управления синхронизацией

- •Линии связи

- •Конфигурирование в устройстве

- •Архитектура плис Spartan-6

- •Slice Spartan-6

- •Блочная память. (Block ram)

- •Потребляемая мощность плис. Эксперимент.

- •Практический эксперимент

- •Расчет потребляемого тока плис. Xilinx Power Estimator (xpe)

- •Xilinx xPower

- •Результат

- •Xilinx Documentation Navigator

Блоки умножителей

Блок умножителя связан с соседним блоком памяти, может выполнять функцию умножения двух 18-разрядных чисел и оптимизирован на выполнение операции с содержимым одного порта блока ОЗУ. Умножитель 18x18 может использоваться и независимо от блочной памяти. Несколько блоков могут каскадироваться и выполнять умножение чисел большей разрядности.

Наличие блоков умножения позволяет эффективно реализовывать на ПЛИС семейства Spartan-3 операции считывания/умножения/суммирования и цифровой фильтрации.

Цифровые блоки управления синхронизацией

Во всех кристаллах семейства Spartan-3, кроме XC3S50, имеется 4 блока цифрового управления сигналами синхронизации - DCM. DCM может использоваться для подстройки фронтов внутренних или внешних тактирующих сигналов, а также для сдвига фазы тактовых частот на 90, 180 и 270 градусов. Дискретный сдвиг фазы реализует точную подстройку с шагом дискретизации, равным 1/256 тактового периода. Гибкий синтез частоты обеспечивает на выходе тактовую частоту, равную отношению М/D к входной тактовой частоте, где М - целое число в диапазоне от 2 до 32, D - целое число в диапазоне от 1 до 32.

В микросхемах существует 8 глобальных тактовых входов, которые обеспечивают доступ к внутренней сети линий связи с малыми задержками.

Линии связи

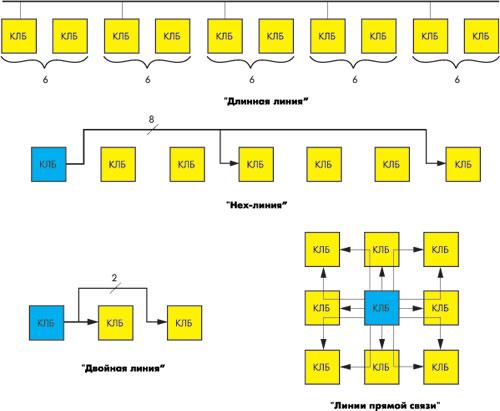

Линии связи осуществляют электрическое соединение различных функциональных элементов ПЛИС друг с другом. Существует 4 типа линий связи: "длинные линии", "hex-линии", "двойные линии" и "линии прямой связи". На рис. 5проиллюстрированы основные отличительные особенности каждого типа линий связи.

Конфигурирование в устройстве

ПЛИС семейства Spartan-3 конфигурируются путем загрузки конфигурационных данных во внутреннюю конфигурационную память, используя один из пяти режимов:

подчиненный последовательный режим (slave serial);

ведущий последовательный режим (master serial);

подчиненный параллельный режим (slave parallel);

ведущий параллельный режим (master parallel);

режим периферийного сканирования (IEEE-1532/IEEE1149.1).

Для хранения конфигурационной последовательности фирма Xilinx выпускает два семейства ПЗУ:

однократно программируемые ПЗУ семейства XC17V00;

перепрограммируемые в системе Flash ППЗУ семейства XC18V00.

В будущем планируется начать производство микросхем Flash-памяти серий XCF00S и XCF00P (табл. ).

Таблица . Микросхемы Flash-памяти серий XCF00S и XCF00P

|

ПЛИС |

Размер файла конфигурации, бит |

Xilinx Flash ПЗУ | |

|

Последовательная загрузка |

Параллельная загрузка | ||

|

XC3S50 |

326 784 |

XCF01S |

XCF08P |

|

XC3S200 |

1 047 616 |

XCF01S |

XCF08P |

|

XC3S400 |

1 699 136 |

XCF02S |

XCF08P |

|

XC3S1000 |

3 223 488 |

XCF04S |

XCF08P |

|

XC3S1500 |

5 214 784 |

XCF08P |

XCF08P |

|

XC3S2000 |

7 673 024 |

XCF08P |

XCF08P |

|

XC3S4000 |

11 316 864 |

XCF16P |

XCF16P |

|

XC3S5000 |

13 271 936 |

XCF16P |

XCF16P |

Подробная информация о ПЛИС семейства Spartan-3 представлена на Интернет-сайте компании Xilinx: www.xilinx.com.

|

SPARTAN-3 |

|

Семейство Spartan-3 — семейство ПЛИС выполненное по техпроцессу 90нм предназначенное для применения в устройствах массового потребления. Основной особенностью ПЛИС данного семейства является низкая цена при большой логической емкости и широких ресурсах ввода-вывода. Технические характеристики:

ПЛИС семейства Spartan-3 подходят для широкого спектра реализации приложений, таких как широкополосный доступ, домашние сети, средства визуализации (мониторы/проекторы) и цифровое телевизионное оборудование. |