- •Оглавление

- •Часть 1

- •Введение

- •Современные плис фирмы xilinx:серия virtex

- •Введение

- •Краткая классификация современных микросхем фирмы xilinx

- •Плис fpga

- •Отличительными системными особенностями являются:

- •Процесс конфигурации

- •Потребление энергии

- •Корпуса933

- •Серия Virtex

- •Серия virtex

- •Семейство Virtex-II

- •Семейство Virtex-II Pro

- •Семейство Virtex-4

- •Семейство Virtex-5

- •Серия Spartan

- •Семейство SpartanXl

- •Семейство Spartan-II

- •Семейство Spartan-iie

- •Семейство Spartan-3/3l

- •Плис фирмы Xilinx: семейство SpartanTm-3

- •Обзор архитектурных особенностей

- •Блоки ввода/вывода (бвв)

- •Конфигурируемые Логические Блоки (клб)

- •Блочная память

- •Блоки умножителей

- •Цифровые блоки управления синхронизацией

- •Линии связи

- •Конфигурирование в устройстве

- •Архитектура плис Spartan-6

- •Slice Spartan-6

- •Блочная память. (Block ram)

- •Потребляемая мощность плис. Эксперимент.

- •Практический эксперимент

- •Расчет потребляемого тока плис. Xilinx Power Estimator (xpe)

- •Xilinx xPower

- •Результат

- •Xilinx Documentation Navigator

Оглавление

Часть 1

Введение 2

Современные ПЛИС фирмы XILINX:серия VIRTEX 5

Введение 5

Краткая классификация современных микросхем фирмы XILINX 7

ПЛИС FPGA 7

Серия Virtex 10

Серия VIRTEX 13

Семейство Virtex-II 25

Семейство Virtex-II Pro 30

Семейство Virtex-4 33

Семейство Virtex-5 38

39

8. С учетом конфигурационного банка Bank 0. 40

Серия Spartan 41

ПЛИС серии Spartan (прежде всего семейств Spartan-II и Spartan-IIE) представляют собой альтернативу применению специализированных интегральных схем ASIC (applications specific integrated circuit). Кристаллы этой серии могут использоваться, например, для реализации проектов, включающих блоки устройств цифровой обработки сигналов, в том числе и DSP- процессоров, различных интерфейсов, включая PCI и USB. RISC- микропроцессоров, специализированных микроконтроллеров. 41

Семейство SpartanXL 42

Семейство Spartan-II 44

Семейство Spartan-IIE 46

Семейство Spartan-3/3L 48

ПЛИС фирмы Xilinx: семейство SpartanTM-3 50

SPARTAN-3 62

Архитектура ПЛИС Spartan-6 63

Slice Spartan-6 81

Блочная память. (Block RAM) 83

Аппаратные блоки умножения 83

Контроллер памяти (Memory Controller Block) 83

PCI Express Core 83

Гигабитные приемопередатчики. (Gigabit Transceiver) 84

Блоки ввода-вывода. 84

MicroBlaze для Spartan 84

Потребляемая мощность ПЛИС. Эксперимент. 85

Практический эксперимент 86

Расчет потребляемого тока ПЛИС. Xilinx Power Estimator (XPE) 88

Xilinx xPower 89

Результат 89

Xilinx Documentation Navigator 92

Введение

Программируемые логические интегральные схемы (ПЛИС) появились полтора десятилетия назад как альтернатива программируемым логическим матрицам (ПЛМ). От последних ПЛИС отличаются как по архитектуре, так и по технологии изготовления.

ПЛМ представляет собой матрицу многовходовых (несколько десятков входов) логических элементов с триггерами, в которых перемычками программируются конституенты единиц дизъюнктивных нормальных форм функций этих элементов. Вначале перемычки выполнялись в виде пережигаемых тонких проводников. Теперь перемычки выполняются в виде МОП-транзистора с плавающим затвором, как в электрически перепрограммируемом ПЗУ, т.е. ПЛМ изготовляются по технологии флэш-памяти. Большие ПЛМ (CPLD) отличаются только тем, что несколько ПЛМ собраны на одном кристалле и объединены программируемым полем связей.

ПЛИС представляет собой матрицу маловходовых (от двух до пяти входов) логических элементов, триггеров, отрезков линий связи, соединяемых перемычками из полевых транзисторов. Судя по английскому названию - Field Programmable Gate Array (FPGA) - ПЛИС программируются изменением уровня электрического поля (field) в затворах этих транзисторов. В отличие, например, от LPGA - Laser Programmable Gate Array. Затворы всех "программирующих" полевых транзисторов подключены к выходам триггеров одного длинного сдвигового регистра, который заполняется при программировании ПЛИС. Некоторые из участков этого регистра могут также выполнять роль ячеек ПЗУ.

Прошивка обычно хранится в ПЗУ, стоящем рядом с ПЛИС и после включения питания или по сигналу сброса она автоматически переписывается в программирующий сдвиговый регистр ПЛИС. Этот процесс называется конфигурированием ПЛИС. Так как основу ПЛИС составляют триггеры, хранящие прошивку, то ПЛИС изготавливаются по технологии микросхем статического ОЗУ.

По сравнению с CPLD, ПЛИС выигрывают:

во-первых, в неограниченном количестве перепрограммирований,

во-вторых, в логической емкости, в том числе в удельной емкости вентилей на цент,

в-третьих, в малом энергопотреблении.

Как правило, ПЛИС имеют на два - три порядка большую емкость в числе эквивалентных логических вентилей, чем CPLD и также как статическое ОЗУ, почти не потребляют энергии при отсутствии переключений. Кроме того, у ПЛИС на порядок выше надежность (ниже интенсивность отказов), чем у CPLD.

К недостаткам относят необходимость внешнего ПЗУ прошивки, генератора синхросерии. Но 8-выводовое ПЗУ занимает на XC18V00 значительно меньше места, чем сама ПЛИС со многими сотнями выводов. То же касается генератора синхросерии.

Много сомнений у пользователей возникает с защитой проекта от копирования. Действительно, прошивка ПЛИС хранится во внешнем ПЗУ, содержимое которого просто копируется. Но изменить или расшифровать прошивку, например, для скрытия авторства или восстановления схемы, практически невозможно, так как семантика битов в файле прошивки - секрет фирмы, а неосторожное изменение ее может вывести ПЛИС из строя. Если требуется защита, то загрузку программы выполняют с помощью внешней CPLD, автомат в которой обеспечивает защиту проекта. В ПЛИС новых поколений предусматривается шифрование прошивки, например, с помощью встроенного шифрователя DES с обеспечением сохранения ключа с помощью батарейки.

Фирма Xilinx, являясь ведущим мировым производителем ПЛИС, предоставляет разработчикам широкий спектр кристаллов с различной технологией производства, степенью интеграции, архитектурой, быстродействием, потребляемой мощностью и напряжением питания, выпускаемых в различных типах корпусов и в нескольких вариантах исполнения, включая промышленное, военное и радиационно-стойкое. Кристаллы, выпускаемые фирмойXilinx, в полной мере реализуют преимущества ПЛИС по сравнению с «жесткой логикой»:

- высокое быстродействие;

- возможность перепрограммирования непосредственно в системе;

- высокая степень интеграции, позволяющая разместить цифровое устройство на одном кристалле и тем самым снизить время и затраты на трассировку и производство печатных плат;

- сокращение времени цикла разработки и производства устройства;

- наличие мощных инструментов САПР, позволяющих устранить возможные ошибки в процессе проектирования устройства;

- сравнительно низкая стоимость (в пересчете на один логический вентиль).

В настоящее время каталог продукции фирмы Xilinxвключает в себя пять серий

ПЛИС с архитектурой FPGA, две серии кристалловCPLDи две серии ПЗУ/ППЗУ, предназначенных для хранения конфигурационных данных.

В кристаллах CPLDконфигурационные данные хранятся во внутренней энергонезависимой памяти. Соответствующая информация заносится в процессе программирования ПЛИС, которое может осуществляться непосредственно в системе с помощью загрузочного кабеля, подключаемого вJTAG-потру. В состав этого сегмента ПЛИС, выпускаемого фирмойXilinx, входят следующие серии кристалловCPLD:

XC9500, представленная семействамиXC9500,XC9500XL,XC9500XV;

CoolRunner, содержащая семействаCoolRunnerXPLA3 иCoolRunner–II.

ПЛИС серий FPGAвыполнены на основе статического ОЗУ. Так как информация о конфигурации кристалла записывается во внутреннее «теневое» ОЗУ, то при выключении источника питания эти данные не сохраняются. Для хранения конфигурационных последовательностей используются внешние элементы ПЗУ и ППЗУ, данные из которых заносятся в «теневое» ОЗУ в процессе инициализации ПЛИС, выполняемой при включении напряжения питания или подаче специального сигнала. Линейка выпускаемых кристалловFPGAпредставлена следующими сериями:

- Spartan, включающая семействаSpartan,SpartanXL,Spartan-IIиSpartan-IIE;

- Virtex, состоящая из семействVirtex,Virtex-E,Virtex-II,Virtex-IIPro;

- XC4000, содержащая семействаXC4000E,XC4000EX,XC4000XL,XC4000XLA,XC4000XV;

- XC5200;

-XC3000, включающая семействаXC3000A,XC3000L,XC3100A,XC3100L.

Для хранения конфигурационных данных кристаллов серий FPGAфирмаXilinxпредоставляет следующие разновидности ПЗУ:

- серию однократно программируемых ПЗУ XC1700;

- серию перепрограммируемых в системе ППЗУ XC18V00.

В настоящее время ПЛИС используются для реализации различных приложений (например, квадролет).

ПЛИС: сбор, обработка информации, выдача управляющих воздействий.

Пример:

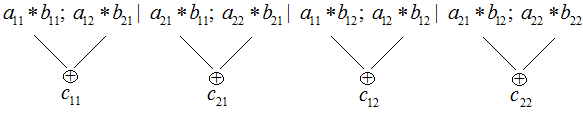

Умножение матриц размера

:

:

Получим ускорение

:

:

(для размера

матриц

(для размера

матриц )

)

(для размера

матриц

(для размера

матриц и случая

и случая )

)