- •Preface

- •Intended Audience

- •What This Document Contains

- •Typographical Conventions

- •Contents

- •1 Product Description

- •1.1 Overview

- •1.1.1 Feature Summary

- •1.1.2 Manufacturing Options

- •1.1.3 Board Layout

- •1.2 Block Diagram

- •1.3 Online Support

- •1.4 Operating System Support

- •1.5 Design Specifications

- •1.6 Processor

- •1.7 System Memory

- •1.8 Intel® 845E Chipset

- •1.8.3 IDE Interfaces

- •1.9 I/O Controller

- •1.9.1 Serial Ports

- •1.9.2 Parallel Port

- •1.9.3 Diskette Drive Controller

- •1.9.4 Keyboard and Mouse Interface

- •1.10 Audio Subsystem

- •1.10.1 Audio Connectors

- •1.10.2 Audio Subsystem Software

- •1.11 LAN Subsystem (Optional)

- •1.11.3 LAN Subsystem Software

- •1.12 Hardware Management Subsystem (Optional)

- •1.12.1 Hardware Monitoring and Fan Control ASIC

- •1.12.2 Fan Monitoring

- •1.12.3 Chassis Intrusion and Detection

- •1.13 Power Management

- •1.13.1 ACPI

- •1.13.2 Hardware Support

- •2 Technical Reference

- •2.1 Introduction

- •2.2 Memory Map

- •2.3 Fixed I/O Map

- •2.4 DMA Channels

- •2.5 PCI Configuration Space Map

- •2.6 Interrupts

- •2.7 PCI Interrupt Routing Map

- •2.8 Connectors

- •2.8.1 Back Panel Connectors

- •2.8.2 Internal I/O Connectors

- •2.8.3 External I/O Connectors

- •2.9 Jumper Blocks

- •2.9.1 Front Panel Audio Connector/Jumper Block

- •2.9.2 BIOS Setup Configuration Jumper Block

- •2.10 Mechanical Considerations

- •2.10.1 I/O Shield

- •2.11 Electrical Considerations

- •2.11.1 DC Loading

- •2.11.3 Fan Connector Current Capability

- •2.11.4 Power Supply Considerations

- •2.12 Thermal Considerations

- •2.13 Reliability

- •2.14 Environmental

- •2.15 Regulatory Compliance

- •2.15.1 Safety Regulations

- •2.15.2 EMC Regulations

- •2.15.3 European Union Declaration of Conformity Statement

- •2.15.4 Product Ecology Statements

- •2.15.5 Product Certification Markings (Board Level)

- •3 Overview of BIOS Features

- •3.1 Introduction

- •3.2 BIOS Flash Memory Organization

- •3.3 Resource Configuration

- •3.3.1 PCI Autoconfiguration

- •3.3.2 PCI IDE Support

- •3.4 System Management BIOS (SMBIOS)

- •3.5 Legacy USB Support

- •3.6 BIOS Updates

- •3.6.1 Language Support

- •3.6.2 Custom Splash Screen

- •3.7 Recovering BIOS Data

- •3.8 Boot Options

- •3.8.2 Network Boot

- •3.8.3 Booting Without Attached Devices

- •3.8.4 Changing the Default Boot Device During POST

- •3.9 Fast Booting Systems with Intel® Rapid BIOS Boot

- •3.9.1 Peripheral Selection and Configuration

- •3.9.2 Intel Rapid BIOS Boot

- •3.10 BIOS Security Features

- •4 BIOS Setup Program

- •4.1 Introduction

- •4.2 Maintenance Menu

- •4.3 Main Menu

- •4.4 Advanced Menu

- •4.4.1 PCI Configuration Submenu

- •4.4.2 Boot Configuration Submenu

- •4.4.3 Peripheral Configuration Submenu

- •4.4.4 IDE Configuration Submenu

- •4.4.5 Diskette Configuration Submenu

- •4.4.6 Event Log Configuration Submenu

- •4.4.7 Video Configuration Submenu

- •4.4.8 USB Configuration Submenu

- •4.4.9 Chipset Configuration Submenu

- •4.5 Security Menu

- •4.6 Power Menu

- •4.6.1 ACPI Submenu

- •4.7 Boot Menu

- •4.7.1 Boot Device Priority Submenu

- •4.7.2 Hard Disk Drives Submenu

- •4.7.3 Removable Devices Submenu

- •4.8 Exit Menu

- •5 Error Messages and Beep Codes

- •5.1 BIOS Error Messages

- •5.2 Port 80h POST Codes

- •5.3 Bus Initialization Checkpoints

- •5.4 Speaker

- •5.5 BIOS Beep Codes

Error Messages and Beep Codes

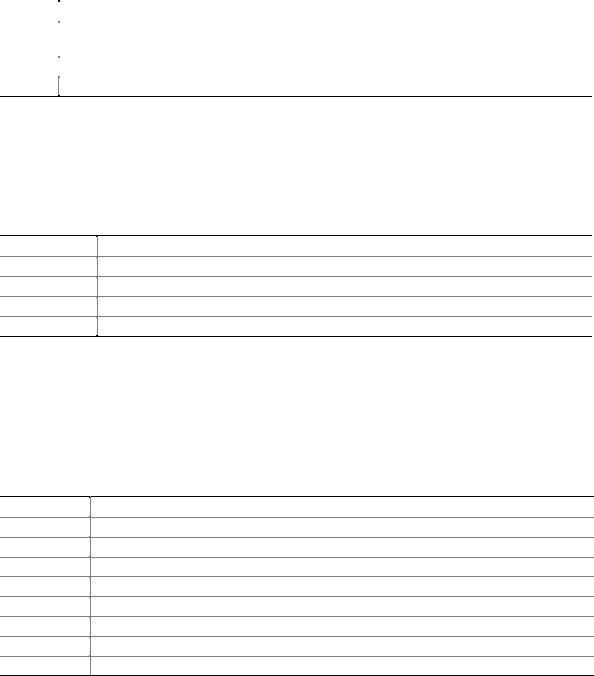

Table 68. Runtime Code Uncompressed in F000 Shadow RAM (continued)

Code |

Description of POST Operation |

AE |

Uncompress SMBIOS module and init SMBIOS code and form the runtime SMBIOS image in |

|

shadow. |

B1 |

Going to copy any code to specific area. |

00Copying of code to specific area done. Going to give control to INT-19 boot loader.

5.3Bus Initialization Checkpoints

The system BIOS gives control to the different buses at several checkpoints to do various tasks. Table 69 describes the bus initialization checkpoints.

Table 69. Bus Initialization Checkpoints

Checkpoint

2A

38

39

95

Description

Different buses init (system, static, and output devices) to start if present.

Different buses init (input, IPL, and general devices) to start if present.

Display different buses initialization error messages.

Init of different buses optional ROMs from C800 to start.

While control is inside the different bus routines, additional checkpoints are output to port 80h as WORD to identify the routines under execution. In these WORD checkpoints, the low byte of the checkpoint is the system BIOS checkpoint from which the control is passed to the different bus routines. The high byte of the checkpoint is the indication of which routine is being executed in the different buses. Table 70 describes the upper nibble of the high byte and indicates the function that is being executed.

Table 70. Upper Nibble High Byte Functions

Value

0

1

2

3

4

5

6

7

Description

func#0, disable all devices on the bus concerned.

func#1, static devices init on the bus concerned.

func#2, output device init on the bus concerned.

func#3, input device init on the bus concerned.

func#4, IPL device init on the bus concerned.

func#5, general device init on the bus concerned.

func#6, error reporting for the bus concerned.

func#7, add-on ROM init for all buses.

103

Intel Desktop Board D845EPI Technical Product Specification

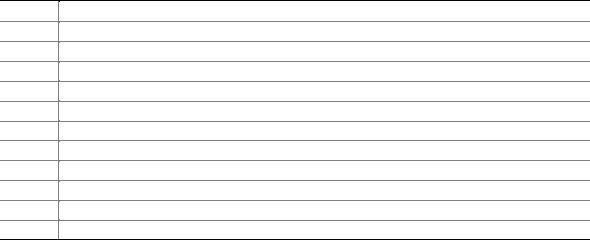

Table 71 describes the lower nibble of the high byte and indicates the bus on which the routines are being executed.

Table 71. Lower Nibble High Byte Functions

Value

0

1

2

3

4

5

Description

Generic DIM (Device Initialization Manager)

On-board System devices

ISA devices

EISA devices

ISA PnP devices

PCI devices

5.4 Speaker

A 47 Ω inductive speaker provides audible error code (beep code) information during POST.

For information about |

Refer to |

The location of the onboard speaker on the Desktop Board D845EPI |

Figure 1, on page 14 |

|

|

5.5 BIOS Beep Codes

Whenever a recoverable error occurs during POST, the BIOS displays an error message describing the problem (see Table 72). The BIOS also issues a beep code (one long tone followed by two short tones) during POST if the video configuration fails (a faulty video card or no card installed) or if an external ROM module does not properly checksum to zero.

An external ROM module (for example, a video BIOS) can also issue audible errors, usually consisting of one long tone followed by a series of short tones. For more information on the beep codes issued, check the documentation for that external device.

There are several POST routines that issue a POST terminal error and shut down the system if they fail. Before shutting down the system, the terminal-error handler issues a beep code signifying the test point error, writes the error to I/O port 80h, attempts to initialize the video and writes the error in the upper left corner of the screen (using both monochrome and color adapters).

104

Error Messages and Beep Codes

If POST completes normally, the BIOS issues one short beep before passing control to the operating system.

Table 72. Beep Codes

Beep Description

1Refresh failure

2Parity cannot be reset

3First 64 KB memory failure

4Timer not operational

5Not used

68042 GateA20 cannot be toggled

7Exception interrupt error

8Display memory R/W error

9Not used

10CMOS Shutdown register test error

11Invalid BIOS (e.g. POST module not found, etc.)

105

Intel Desktop Board D845EPI Technical Product Specification

106