1225

.pdf

Для линейной интерполяции

X W X dt 1 t отр

n |

1 |

n |

|

|

X t , y |

|

y t |

||

|

|

|||

tотр i 1 |

||||

i 1 |

|

|||

9.4. РЕАЛИЗАЦИЯ ИНТЕГРИРОВАНИЯ В СЧПУ

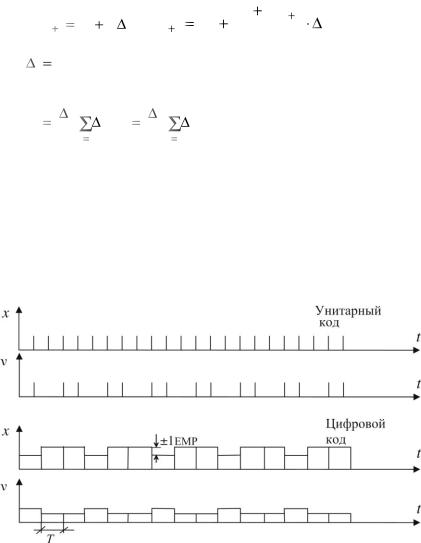

Интеграторы в СЧПУ всегда работают в дискретном виде, используя импульсную последовательность (унитарный код) или цифровой код. Это связано с требованиями точности, так как именно интеграторы обеспечивают необходимую точность формообразования детали.

При выполнении интеграторов в аппаратном виде (аппаратное моделирование) используются преобразователи кода в частоту. При этом выход интегратора – унитарный код (последовательность импульсов, общее количество которых задает перемещение, частота поступления – скорость по оси). Квант перемещения здесь постоянен – один импульс частоты, т.е. для линейной интерполяции x = y = ,

|

|

|

n |

|

n |

x |

|

|

tx , y |

|

ty . |

tотр i |

|

||||

|

1 |

tотр i 1 |

|||

Временной интервал между импульсами переменен и зависит от осевой скорости Vx , Vy , Vz . Это и является одним из недостатков

данного способа интегрирования, когда максимальная частота выдачи импульсов, а значит, и максимальная скорость перемещения ограничены возможностью СЧПУ (обычно Vk max 5 м/с).

При выполнении интеграторов программным путем на ЭВМ происходит прямое решение дифференциальных уравнений (обычно простейшим способом – методом Эйлера). Квант по времени постоянен и зависит от возможностей ЭВМ и от полосы пропускания непрерывной части. Величина приращения по координате за квант по времени зависит от максимально возможных скорости перемещения и ускорения на данном станке с данными приводами.

131

Уравнения интегрирования по i-й координате на j+1 шаге:

Vij |

Vi, j 1 |

|

|

Vi, j 1 Vij ai t , Si, j 1 Sij |

|

|

t , |

|

2 |

||

|

|

|

|

где t const .

Для линейной интерполяции при Vk = const

|

t |

n |

t |

n |

|||

x |

|

|

x , y |

|

|

y . |

|

tотр i |

tотр i |

||||||

|

1 |

1 |

|||||

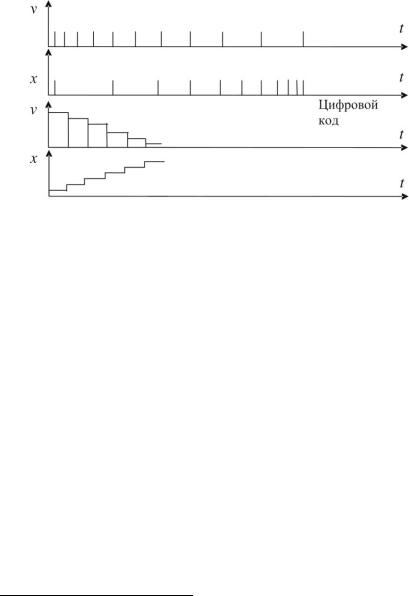

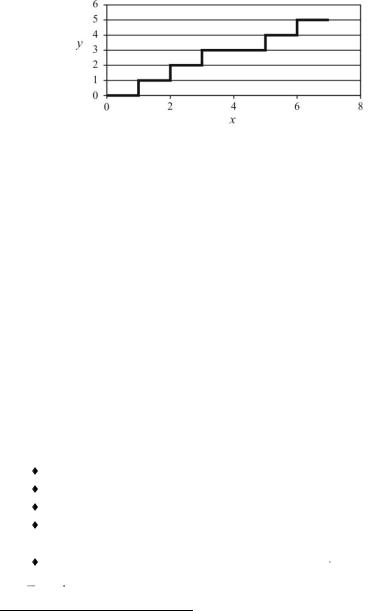

При этом операции умножения заменяются операциями сложения и сдвига (деления пополам). На рис. 9.6, 9.7 приведены графики, демонстрирующие выходной код на приводы после интерполяции: круговой или линейной, при постоянном кванте перемещений (унитарный код) или постоянном кванте времени (цифровой код, где ±1ЕМР – вес единицы младшего разряда).

Рис. 9.6. Характер выходных сигналов интерполятора при линейной интерполяции для аппаратных и микропроцессорных СЧПУ

132

Рис. 9.7. Характер выходных сигналов интерполятора при круговой интерполяции для аппаратных и микропроцессорных СЧПУ

Конкретные системы УЧПУ с аппаратной реализацией интерполятора рассмотрены ниже.

9.5. СЧПУ «КОНТУР-2ПТ»*

Интегратор выполнен на ПКЧ (преобразователь код – частота) последовательного преобразования, называемый здесь «умножителем частоты», работает в двоично-десятичном коде только для линейной интерполяции. Умножители частоты называют также интегратором последовательного переноса или ПКЧ последовательного действия.

9.6. СЧПУ «Н22»**

Интегратор выполнен на ПКЧ для двух координат в двоичном коде для линейной и круговой интерполяции при использовании ал-

горитма оценочной функции.

*Программное управление станками / под ред. В.Л. Сосонкина. 1981. С. 197–208.

**Программное управление станками / под ред. В.Л. Сосонкина. 1981. С. 208–227.

133

В этом случае на каждом шаге решается алгебраическое уравнение траектории.

Для линейной интерполяции:

y |

y |

x – в непрерывной форме, где y, x принимаем поло- |

|

x |

|||

|

|

жительными (1-й квадрант).

y |

y |

x |

– в дискретной форме в i-м такте интегрирования. |

|

|||

i |

x |

i |

|

|

|

|

|

yi |

x |

xi |

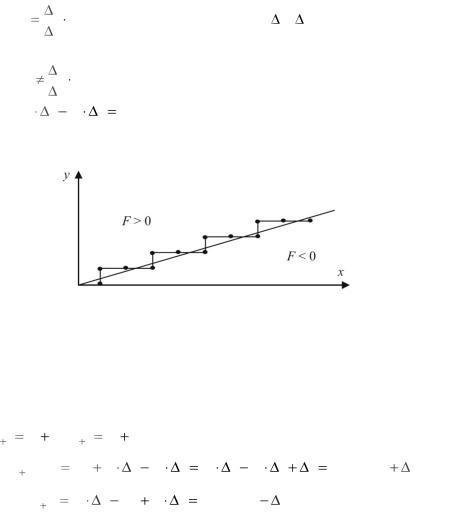

y F – оценочная функция, т.е ошибка между не- |

прерывной величиной и ее дискретной формой. Движение в очередном такте зависит от знака оценочной функции (рис. 9.8).

Рис. 9.8. Интерполяция в функции знака оценочной функции

Если F > 0, то в следующем такте надо делать перемещение по x, если F < 0, то по y.

Определим оценочную функцию в следующем такте, если сделали перемещение (один импульс по y или по x). Учитывая, что

xi 1 xi 1, |

yi 1 |

yi |

1 , имеем |

|

|

|

F yi 1, xi |

yi |

1 |

x xi |

y yi x xi |

y x F yi , xi |

x; |

F yi , xi 1 |

yi |

x xi 1 |

y F yi , xi |

y. |

|

|

Таким образом, на каждом шаге интегрирования надо рассчитывать оценочную функцию. На практике, если имеет место перемеще-

134

ние по меньшей координате, производят перемещение и по большей координате.

Пример:

Пусть y = 5, x = 7. (Нужно сделать 12 шагов.)

F (Y0,, X0) = 0

1 шаг по большей координате (по Х).

F (Y0, X1) = F (Y0, X0) – y = 0 – 5 = –5.

2 шаг так как F (Y0, X1) < 0, делаем следующий шаг по Y. F (Y1, X1) = F (Y0, X1) +7 = –5+7 = 2.

3 шаг так как F (Y1, X1) > 0, делаем следующий шаг по Х.

F (Y1, X2) = F (Y1, X1) –5 = 2–5 = –3. 4 шаг по Y.

F (Y2, X2) = –3+7 = 4. 5 шаг по Х.

F (Y2, X3) = 4–5 = –1.

6 шаг по Y.

F (Y3, X3) = –1+7 = 6.

7 шаг по Х.

F (Y3, X4) = 6–5 = 1. 8 шаг по Х.

F (Y3, X5) = 1–5 = –4.

9 шаг по Y.

F (Y4, X5) = –4+7 = 3.

10 шаг по Х.

F (Y4, X6) = 3–5 = –2. 11 шаг по Y.

F (Y5, X6) = –2+7.

12 шаг по Х.

F (Y5, X7) = 5–5 = 0.

Диаграмма движения представлена на рис. 9.9.

135

Рис. 9.9. Диаграмма движения при интерполяции по оценочной функции

9.7. СЧПУ «Н33»*

Интегратор выполнен на ПКЧ параллельного действия, работающем в двоичном коде. Способ интегрирования называется цифровым дифференциальным анализатором. Это наиболее совершенная аппаратная стойка ЧПУ. Вначале она реализовывалась на простых микросхемах, затем на БИС.

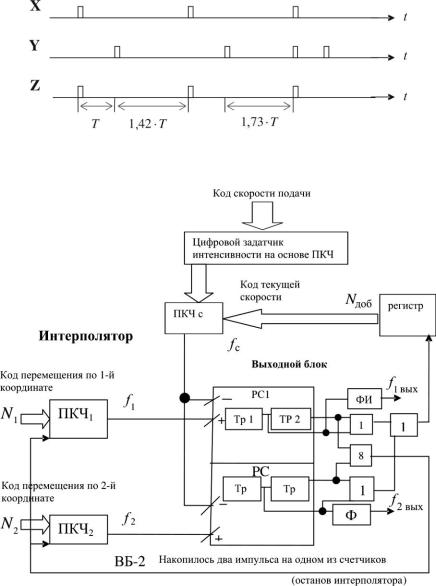

9.8. БЛОК ЗАДАНИЯ СКОРОСТИ (БЗС) АППАРАТНОЙ СТОЙКИ ЧПУ

На примере СЧПУ Н33 рассмотрим структуру блока задания скорости (рис. 9.10), его связи с интерполятором и выходным блоком

(рис. 9.12).

Функции БЗС:

отработка перемещений с заданной скоростью подачи; разгон в начале отработки кадра; торможение на стыке кадров при смене скорости подачи;

автоматическое поддерживание постоянной контурной скорости при мгновенных включениях в работу одной, двух, трех координат; ручное управление оператором с шагом 0,1 Vконт в пределах

0,1 1, 2 Vконт .

* Программное управление станками / под ред. В.Л. Сосонкина. 1981. С. 227–249.

136

Структура БЗС (см. рис. 9.10)

С перфоленты код скорости подачи записывается в буферный регистр ввода информации. В рабочем регистре находится выполняемый кадр управляющей программы. Наличие двух регистров позволяет заблаговременно записать и подготовить очередной кадр с перфоленты во время исполнения записанного кадра в рабочем регистре.

Схема сравнения по коду задания скорости подачи и коду с выхода цифрового задатчика интенсивности вырабатывает сигнал разрешения на разгон или торможение (интегрирование в цифровом задатчике интенсивности).

V – цифровой код ускорения или замедления.

Работа интеграторов на базе ПКЧ параллельного действия описана в главе 6.

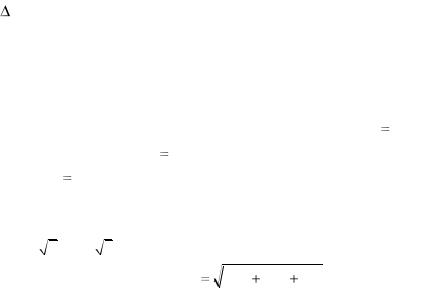

Дополнительный сумматор в преобразователе код – частота предназначен для того, чтобы обеспечить постоянство контурной скорости. Если в выходном блоке накопилось три импульса на выход по трем координатам (регистры X, Y, Z, см. рис. 9.12), то Nдоб 0 .

Если два импульса, то Nдоб 42 % N сумматора. Если один импульс, то Nдоб 73 % N сумматора.

Импульсы с выходного блока по осям выдаются, как показано на рис. 9.11. Добавляя Nдоб , ускоряем выдачу импульсов с выходно-

го блока в

2 или

2 или

3 раз, чтобы оставить общую контурную пода-

3 раз, чтобы оставить общую контурную пода-

|

|

|

|

|

|

чу в данном такте неизменной (V |

V 2 |

V 2 |

V 2 |

). |

|

конт |

|

X |

Y |

Z |

|

На структуре БЗС (см. рис. 9.10) указан модуль торможения, который определяет момент начала торможения в конце кадра. Для этого используется несколько информационных сигналов. В регистре КОК (конец отработки кадра) в начале кадра записывается максимальное перемещение, которое задано по одной из координат X, Y, Z. По мере выдачи импульсов по этой координате из регистра

137

Рис. 9.10. Структура блока задания скорости

138

Рис. 9.11. Характер выдачи импульсов перемещения выходным блоком при обеспечении постоянства контурной скорости

Рис. 9.12. Структура совместной работы интерполятора, блока задания скорости и выходного блока аппаратной стойки ЧПУ

139

КОК вычитаются единицы. После выдачи всех импульсов регистр выдает сигнал КОК для начала перехода к выполнению следующего кадра. Информация в регистре КОК есть код оставшегося пути до конца кадра.

В модуле торможения формируется код величины тормозного пути, необходимого для остановки с заданной скоростью подачи. Принято фиксированное время торможения. Поэтому код заданной скорости подачи однозначно определяет и необходимый тормозной путь.

Если оператор вручную изменил скорость подачи, то это учитывается в коде необходимого тормозного пути. Как только код необходимого тормозного пути сравняется с кодом оставшегося пути перемещения, в кадре (регистр КОК) вырабатывается сигнал на начало торможения.

Заметим, что сами интеграторы интерполятора выполнены так же, как преобразователи «код – частота» параллельного действия. В целом, структура взаимодействия интерполятора, блока задания скорости, выходного блока имеет вид, показанный на рис. 9.12.

Реверсивные счетчики X, Y, Z имеют по два триггера и накапливают до 2 импульсов с интеграторов. Если хотя бы в одном счетчике окажутся накопленными два импульса, то дешифратор вырабатывает сигнал ВБ-2, которым останавливает работу интерполятора. Как только поступит очередной импульс с блока задания скорости, так сразу же с счетчиков X, Y, Z выдаются импульсы на координаты (если они были в регистрах X, Y, Z), интерполятор снова запускается до нового переполнения одного из счетчиков X, Y, Z (появления «1» во втором разряде).

Контрольные вопросы

1. Как работают интеграторы интерполятора при их аппаратной или программной реализации?

140