Элементы систем автоматики

..pdfтельном коде на тактовую шину С регистра необходимо подать столько тактовых импульсов, сколько символов содержит цифровой сигнал. При этом символы записанного сигнала последовательно смещаются вправо к выходу Q триггера старшего разряда, а триггеры младших разрядов при этом последовательно обнуляются. В результате считывания цифровых сигналов в последовательном коде информация в последовательном регистре теряется.

Считывание цифровых сигналов в параллельном коде из последовательных регистров производится так же, как и в параллельном регистре, через систему логических ключей И. При этом виде считывание может быть многократным без потери информации в регистре.

В последовательном регистре может быть предусмотрена система записи цифровых сигналов в параллельном коде, которая устроена и работает по тому же принципу, что и в параллельном регистре. Отличие состоит лишь в том, что импульс на шине управления записью выдерживается в единичном состоянии в течение всего периода тактового импульса, одновременно подаваемого на все входы С триггеров регистра. Записанный в параллельном коде цифровой сигнал может в дальнейшем считываться в последовательном коде по вышеописанной схеме.

3.4. Двоичные счетчики

Для подсчета количества последовательно следующих «прямоугольных» импульсов используют двоичные счетчики. Структура двоичного счетчика показана на рис. 33. Основой такого счетчика является триггер, работающий в счетном (в переключающем Т) режиме. Такой режим можно получить на триггере типа JK, если на его входы J и K одновременно подать единичный сигнал. При этом, за каждый полный тактовый импульс он будет менять свое состояние на противоположное, только тогда, когда на его входе С тактовый импульс будет меняться с 0 на 1. Количество триггеров в счет- чике определяет максимальное число импульсов, которое он может зафиксировать. Этот показатель называется модулем счета.

На рис. 33 изображен двоичный счетчик, выполненный на основе трех JK-триггеров. На вход С первого триггера (триггера младшего разряда) последовательно подаются тактовые импульсы,

51

количество которых необходимо подсчитать. Выход Q каждого предыдущего триггера соединен с входом С последующего триггера. Принцип работы этого счетчика можно проследить по записи логического состояния его триггеров, отраженной в табл. 5.

Рис. 33. Структура двоичного счетчика

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Ò à á ë è ö à |

5 |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Òàêò |

|

1 |

|

2 |

3 |

|

|

4 |

|

5 |

|

6 |

|

7 |

|

8 |

|

9 |

|

|||||||||

Ñ |

1 |

|

0 |

1 |

|

0 |

1 |

|

0 |

1 |

|

0 |

1 |

|

0 |

1 |

|

0 |

1 |

|

0 |

1 |

|

0 |

1 |

|

0 |

1 |

Q1 |

0 |

|

1 |

1 |

|

0 |

0 |

|

1 |

1 |

|

0 |

0 |

|

1 |

1 |

|

0 |

0 |

|

1 |

1 |

|

0 |

0 |

|

1 |

1 |

Q2 |

0 |

|

0 |

0 |

|

1 |

1 |

|

1 |

1 |

|

0 |

0 |

|

0 |

0 |

|

1 |

1 |

|

1 |

1 |

|

0 |

0 |

|

0 |

0 |

Q3 |

0 |

|

0 |

0 |

|

0 |

0 |

|

0 |

0 |

|

1 |

1 |

|

1 |

1 |

|

1 |

1 |

|

1 |

1 |

|

0 |

0 |

|

0 |

0 |

3 5. Шифраторы

Шифраторы применяются для поучения числового двоичного кода номера однобитового канала, по которому передается единич- ный символ. Необходимость такого кодирования часто возникает в цифровых системах автоматики. На рис. 34 даны логические схемы некоторых типов шифраторов.

Шифраторы выполняются на основе логических элементов ИЛИ, соединенных по определенной схеме. Принцип работы простейшего из них пояснен вариантами логических состояний его входов и выходов, представленных в табл. 6.

Непременным условием работы шифратора является то, что единичный сигнал не должен появляться более чем на одном канале входа.

52

Рис. 34. Структура шифратора. на три входа (а), на семь входов (б)

Если на всех каналах ввода |

|

|

|

Ò à á ë è ö à 6 |

||

присутствует только нулевой |

|

|

|

|

|

|

Номер входа канала |

|

Код канала |

||||

сигнал, это значит, что все вхо- |

|

|||||

3 |

2 |

1 |

|

|

|

|

ды логических элементов ИЛИ |

|

|

|

|||

обнулены, поэтому их выходы |

0 |

0 |

0 |

|

0 |

0 |

формируют нулевой код. В слу- |

0 |

0 |

1 |

|

0 |

1 |

чае появления единичного сиг- |

0 |

1 |

0 |

|

1 |

0 |

нала на первом канале ввода ле- |

|

|

|

|

|

|

1 |

0 |

0 |

|

1 |

1 |

|

вый элемент ИЛИ формирует на |

|

|||||

|

|

|

|

|

|

|

выходе 0, а правый 1, поэтому |

|

|

|

|

|

|

на выходе шифратора будет двоичное число 01. При появлении единичного сигнала на третьем канале ввода оба элемента ИЛИ формируют на своих выходах двоичное число 11, которое соответствует номеру канала 3 в десятичном исчислении. Аналогично работает шифратор на семь входов, однако, у него более сложная комбинация логических связей на входах трех элементов ИЛИ. Принцип работы этого шифратора можно проследить по данным его логического состояния, представленных в табл. 7.

Ò à á ë è ö à 7

|

|

Номер входа канала |

|

|

|

Код канала |

|

Номер канала |

||||

1 |

2 |

|

3 |

4 |

|

5 |

6 |

7 |

– |

– |

– |

|

0 |

0 |

|

0 |

0 |

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

|

0 |

0 |

|

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

|

0 |

0 |

|

0 |

0 |

0 |

0 |

1 |

0 |

2 |

0 |

0 |

|

1 |

0 |

|

0 |

0 |

0 |

0 |

1 |

1 |

3 |

0 |

0 |

|

0 |

1 |

|

0 |

0 |

0 |

1 |

0 |

0 |

4 |

0 |

0 |

|

0 |

0 |

|

1 |

0 |

0 |

1 |

0 |

1 |

5 |

53

Î ê î í ÷ à í è å ò à á ë . 7

|

|

Номер входа канала |

|

|

|

Код канала |

|

Номер канала |

||||

0 |

0 |

|

0 |

0 |

|

0 |

1 |

0 |

1 |

1 |

0 |

6 |

0 |

0 |

|

0 |

0 |

|

0 |

0 |

1 |

1 |

1 |

1 |

7 |

При последовательной подаче единичных сигналов на вход шифратора на его выходе также последовательно появляются дво- ичные числа от 001 до 111, что соответствует номеру активного канала в десятичном исчислении от 1 до 7.

3.6. Дешифраторы

Дешифраторы в системах автоматики выполняют функцию, обратную шифраторам, т. е. по двоичному коду, поданному на их вход, они активизируют один из своих выходных каналов. Если входной сигнал будет нулевым, то на выходе дешифратора всегда будет активизирован нулевой канал. Выходной сигнал активного канала может быть представлен в прямом (единичном) и инверсном (нулевом) коде. В состав дешифратора входят логические элементы И и НЕ, объединенные соответствующими логическими связями. Логическая структура дешифратора показана на рис. 35.

Рис. 35. Структура дешифратора

Логическое состояние каналов выхода в зависимости от значе- ния кода входного сигнала приведено в табл. 8. Если входы А и В

54

одновременно обнулены (код |

|

|

|

Ò à á ë è ö à 8 |

||

входного сигнала 00), то оба |

|

|

|

|

|

|

Код выхода |

|

Номер канала |

|

|||

вводных инвертора одновре- |

|

|

||||

|

|

|

|

|

|

|

менно подают единичные сигна- |

B |

A |

0 |

1 |

2 |

3 |

лы только на элемент И с номе- |

0 |

0 |

1 |

0 |

0 |

0 |

ром выхода 0 (нулевой выход- |

0 |

1 |

0 |

1 |

0 |

0 |

ной канал). Поэтому только на |

1 |

0 |

0 |

0 |

1 |

0 |

этом канале появится единич- |

1 |

1 |

0 |

0 |

0 |

1 |

|

||||||

ный сигнал, а все остальные выходные каналы будут обнулены,

т. к. на входах их элементов И будет присутствовать хотя бы по одному нулевому входному сигналу (с символом 0).

Для активизации канала 1 второго логического элемента И необходимо непосредственно подать на его вход единичный сигнал с клеммы А и одновременно подать на его второй вход единичный сигнал через инвертор с клеммы В, которая в это время обнулена. Аналогично активизируются все остальные выходы дешифратора.

Дешифраторы широко используются в цифровых системах автоматики при переключении каналов и логических устройств в процессе их информационного обмена.

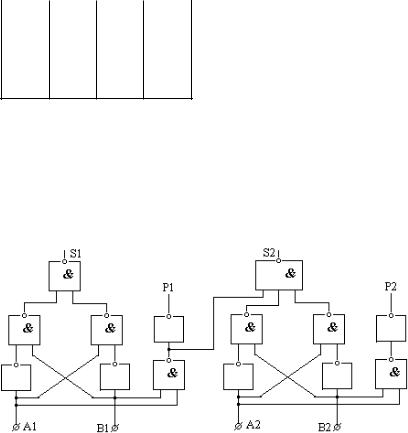

3.7.Мультиплексоры

Âцифровых системах автоматики мультиплексоры применяют для подключения к общему каналу передачи цифровой информации одного из нескольких логических устройств, формирующих параллельные информационные потоки. Логическая схема мультиплексора представлена на рис. 36. Выход элемента ИЛИ образует общий информационный канал, на который через логические ключи (элементы И) подается однобитовая информация с нескольких параллельных каналов (D0, D1, D2, D3). Каждый из этих каналов подает одновременно сигнал на один из входов своего логического ключа

È.На другой вход этих ключей поступают сигналы с дешифратора, а третий их вход одновременно подключен к шине управления.

Принцип работы мультиплексора. При подаче на вход дешифратора двоичного кода номера канала, информацию которого необходимо подключить на общий выходной канал, и при одновременной активизации шины управления к выходному каналу мультиплексора

55

Рис. 36. Структура мультиплексора

через элемент ИЛИ подключается именно тот информационный входной канал, двоичный код которого введен в встроенный дешифратор. Таким образом, мультиплексоры могут подключать к общему выходному каналу входные каналы в любой последовательности

âзависимости от алгоритма этого ввода.

3.8.Распределители

Âотличие от дешифраторов распределители при каждом тактовом импульсе последовательно активизируют свои выходы. Логи- ческая схема распределителя представлена на рис. 37. Основу распределителя составляет регистр последовательного сдвига, прямые выходы Q которого подключены на вход элемента ИЛИ-НЕ, а выход этого элемента подключен к входу D триггера младшего разряда этого регистра.

Принцип работы распределителя. Первоначально все выходы Q регистра последовательного сдвига обнулены, поэтому обнулены все входы логического элемента ИЛИ-НЕ, при этом на вход D триггера младшего разряда этого регистра подается единичный, выходной сигнал. Этот единичный сигнал появляется только при полном обнулении регистра сдвига. В результате появления единичного сигнала на входе D триггера младшего разряда регистра этот триггер перейдет в единичное состояние после первого тактового им-

56

Рис. 37. Структура распределителя

пульса. Как только это произойдет, элемент ИЛИ-НЕ переходит в нулевое состояние, которое будет сохраняться до тех пор, пока регистр сдвига не обнулится снова.

Последующие тактовые импульсы будут смещать единичный выход в строну триггеров старших разрядов регистра, в то время как триггеры младших разрядов будут обнуляться. Как только все триггеры регистра вновь окажутся «нулевыми», на входе D его триггера младшего разряда опять появится единица, которая снова будет последовательно смещаться по разрядам регистра сдвига при каждом тактовом импульсе.

3.9.Сумматоры

Âцифровых системах автоматики сумматоры применяют для выполнения любых арифметических действий над двоичными числами (цифровыми сигналами). Использование правил арифметиче- ского сложения целых чисел в сочетании с операциями логических сдвигов (вправо или влево) позволяет вычислительным устройствам систем цифровой автоматики выполнять любые алгебраиче- ские операции над двоичными числами (цифровыми сигналами). Поэтому сумматоры являются частью арифметическо-логических устройств (АЛУ) этих систем. Сумматоры работают по правилам сложения двоичных чисел, изложенных в табл. 9.

По этим правилам происходит поразрядное сложение двух дво- ичных чисел с учетом значения единицы переноса в младшем (пре-

57

дыдущем) разряде сумматора. Логическая структура двухразрядного сумматора представлена на рис. 38.

|

|

|

|

В этой таблице: |

|

|

|

Ò à á ë è ö à 9 |

А — первое слагаемое; |

||

|

|

|

|

В — второе слагаемое; |

|

A |

B |

S |

P |

||

S — результат суммы; |

|||||

0 |

0 |

0 |

0 |

||

Р — единица переноса в стар- |

|||||

1 |

0 |

1 |

0 |

ший разряд. |

|

0 |

1 |

1 |

0 |

Принцип работы каждого |

|

1 |

1 |

0 |

1 |

разряда сумматора определен со- |

|

отношением значений слагаемых, построчно представленных в табл. 9. Так, если оба слагаемых в младшем разряде одновременно

нулевые (т. е. А1 = В1 = 0), то результат суммы слагаемых в этом разряде тоже нулевой (т. е. S1 = 0), как нулевой остается единица переноса (Р = 0). При единичном значении одного из слагаемых (А1 = 1 или В1 = 1) результат суммы слагаемых в этом разряде становится единичным (S1 = 1), а единица переноса остается нулевой (Р = 0).

Рис. 38. Структура двухразрядного сумматора

Только в случае сложения двух единичных слагаемых (А1 = 1 и В1 = 1) их сумма в текущем разряде сложения становится нулевой (S1 = 0), а параметр переноса равен единице (Р = 1). Этот параметр переносится в следующий старший разряд и становится третьим слагаемым суммы S2, кроме слагаемых А2 и В2.

58

3.10. Аналого-цифровой преобразователь

Большинство технических устройств получения информации формируют аналоговый сигнал, в то время как для цифровых систем эти сигналы должны быть поданы в цифровом виде. Для преобразования аналоговых сигналов в цифровую форму применяют специальные устройства, которые называются аналого-цифровыми преобразователями, или сокращенно АЦП. Принцип преобразования аналогового сигнала в цифровой код состоит из нескольких этапов. Так как цифровой сигнал всегда дискретен, то на первом этапе преобразования происходит превращение непрерывного аналогового сигнала в дискретный сигнал постоянного уровня. Для этого, как показано на рис. 39, а, непрерывно меняющийся во времени аналоговый сигнал разбивают (квантуют) на равные временные участки t, в течение которых затем выдерживают этот сигнал на постоянном уровне. Только после этого такой сигнал преобразуют в цифровой код.

Рис. 39. Структура и принцип работы АЦП

Структура аналого-цифрового преобразователя показана на рис. 39, г. Основой такого преобразователя является пороговый элемент, на вход которого подаются два сигнала: постоянный по уровню (в течение времени преобразования t) аналоговый сигнал и сту-

59

пенчатый по уровню опорный сигнал. Опорный сигнал является инструментом измерения уровня аналогового сигнала. Ступени опорного сигнала формируются следующим образом. Произвольно, исходя из конкретных параметров АЦП, выбирается наименьшая ступень опорного сигнала, численно равная одной двоичной единице. Следующая ступень опорного сигнала берется вдвое больше первой и в ней содержится уже две двоичные единицы. Следующая ступень также удваивается как по уровню, так и по числовому значению. Число ступеней опорного сигнала численно равно разрядности выходного сигнала АЦП, а ширина каждой ее ступени t1 определяется временем преобразования t, поделенным на число ступеней. Структура опорного сигнала показана на рис. 39, á.

Принцип работы АЦП. Первоначально на вход порогового элемента одновременно с постоянным уровнем аналогового сигнала подается наибольшая ступень опорного сигнала. Если уровень опорного сигнала будет выше уровня аналогового, то через время «t1» эта ступень отбрасывается, а на выходе порогового элемента

âстаршем разряде цифрового кода сигнала записывается нулевой символ. Если же уровень опорной ступени меньше уровня аналогового сигнала, то эта ступень фиксируется на входе порогового элемента, а на его выходе появляется единичный символ в соответствующем разряде цифрового кода. В следующий временной цикл t1 на вход порогового элемента подается последующая ступень опорного сигнала, в двое меньшая предыдущей, которая может уже складываться с фиксированной на входе одной из предыдущих ступеней. Выходной результат определяется вышеописанным образом. Последовательность формирования символов цифрового кода

âпроцессе преобразования аналогового сигнала с уровнем Y показана на рис. 39, в.

Схема принципиального устройства одного из вариантов АЦП приведена на рис. 40.

Âкачестве порогового элемента в этом устройстве взят компаратор К, который как пороговый элемент формирует на выходе один из сигналов высокого уровня (1) или низкого уровня (0). Аналоговый сигнал постоянного уровня после временного квантования подается на его отрицательный вход, а на положительный вход компаратора через распределитель и транзисторные ключи (Т1, Т2, Т3, Т4) последовательно подаются ступени опорного напряжения, уровень кото-

60