Отчеты / ЛАБ2

.1.pdfМинистерство образования и науки Российской Федерации Федеральное государственное бюджетное образовательное учреждение высшего профессионального образования

«ТОМСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ СИСТЕМ УПРАВЛЕНИЯ И РАДИОЭЛЕКТРОНИКИ» (ТУСУР)

Кафедра комплексной информационной безопасности электронно-

вычислительных систем (КИБЭВС)

ШИФРАТОРЫ И ДЕШИФРАТОРЫ Отчет по лабораторной работе №2

по дисциплине «Электроника и схемотехника 2»

Вариант №5

Выполнил:

Студент гр. 710-2

_______ _____Кузьмина А.А.

__.05.2022

Принял: преподаватель каф. КИБЭВС

_______ А.С. Семенов

__.05.2022

Томск - 2022

2

1 Введение

Цель работы: научиться создавать шифраторы и дешифраторы на разных базисах и решать задачу увеличения их размерности.

Задания для лабораторной работы:

1. Составить таблицу истинности для схем, заданных согласно варианту. Написать формулы для всех выходов в СДНФ или СКНФ и привести формулы к требуемому базису согласно варианту;

2.Собрать схему на холстах .bdf согласно полученным формулам и создать символ для полученного блока;

3.Создать схему устройства согласно варианту большей размерности на основе созданного ранее символа;

4. Промоделировать работу всех схем в двух режимах;

5. Повторить пп. 2-4, только для описания устройств вместо схем на холстах .bdf использовать заданный вариантом HDL.

Задание по варианту:

1.Шифратор CD: 8-3; И-НЕ ; 16-4;

2.Дешифратор DC: 2-4; И, ИЛИ, НЕ; 3-8;

3.HPRI: 10-4; ИЛИ-НЕ; -;

4.HDL – SystemVerilog.

3

2 Ход работы

2.1 Шифратор 8 – 3

Таблица 1 истинности для шифратора 8 – 3 представлена ниже.

Таблица 1 – Таблица истинности шифратора 8-3.

|

|

|

|

Входы |

|

|

|

|

|

Выходы |

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Е |

x7 |

x6 |

x5 |

|

x4 |

|

x3 |

x2 |

x1 |

x0 |

а0 |

a1 |

а2 |

G |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

x |

x |

x |

|

x |

|

x |

x |

x |

x |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

0 |

0 |

|

0 |

|

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

1 |

0 |

|

0 |

|

0 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

1 |

|

0 |

|

0 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

0 |

|

1 |

|

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

0 |

|

0 |

|

1 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

0 |

|

0 |

|

0 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

0 |

|

0 |

|

0 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

0 |

|

0 |

|

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

0 |

|

0 |

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Составим формулы для базиса И-НЕ:

̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅

0 = ∩ 7 ∩ ( 0 ∩ 1 ∩ 2 ∩ 3 ∩ 4 ∩ 5 ∩ 6) ∩

̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅

∩ 6 ∩ ( 0 ∩ 1 ∩ 2 ∩ 3 ∩ 4 ∩ 5 ∩ 7) ∩

̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅

∩ 5 ∩ ( 0 ∩ 1 ∩ 2 ∩ 3 ∩ 4 ∩ 6 ∩ 7) ∩

4

̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅

∩ 4 ∩ ( 0 ∩ 1 ∩ 2 ∩ 3 ∩ 5 ∩ 6 ∩ 7);

̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅

1 = ∩ 7 ∩ ( 0 ∩ 1 ∩ 2 ∩ 3 ∩ 4 ∩ 5 ∩ 6) ∩

̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅

∩ 6 ∩ ( 0 ∩ 1 ∩ 2 ∩ 3 ∩ 4 ∩ 5 ∩ 7) ∩

̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅

∩ 3 ∩ ( 0 ∩ 1 ∩ 2 ∩ 4 ∩ 5 ∩ 6 ∩ 7) ∩

̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅

∩ 2 ∩ ( 0 ∩ 1 ∩ 3 ∩ 4 ∩ 5 ∩ 6 ∩ 7);

̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅

2 = ∩ 7 ∩ ( 0 ∩ 1 ∩ 2 ∩ 3 ∩ 4 ∩ 5 ∩ 6) ∩

̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅

∩ 5 ∩ ( 0 ∩ 1 ∩ 2 ∩ 3 ∩ 4 ∩ 6 ∩ 7) ∩

̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅

∩ 3 ∩ ( 0 ∩ 1 ∩ 2 ∩ 4 ∩ 5 ∩ 6 ∩ 7) ∩

̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅

∩ 1 ∩ ( 0 ∩ 2 ∩ 3 ∩ 4 ∩ 5 ∩ 6 ∩ 7);

̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅

= ∩ 7 ( 6 ∩ 5 ∩ 4 ∩ 3 ∩ 2 ∩ 1 ∩ 0 ) ∩ 6

̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅

( 7 ∩ 5 ∩ 4 ∩ 3 ∩ 2 ∩ 1 ∩ 0 ) ∩ 5

(̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅)

7 ∩ 6 ∩ 4 ∩ 3 ∩ 2 ∩ 1 ∩ 0 ∩ 4

̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅

( 7 ∩ 6 ∩ 5 ∩ 3 ∩ 2 ∩ 1 ∩ 0 ) ∩ 3

̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅

( 7 ∩ 6 ∩ 5 ∩ 4 ∩ 2 ∩ 1 ∩ 0 ) ∩ 2

̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅

( 7 ∩ 6 ∩ 5 ∩ 4 ∩ 3 ∩ 1 ∩ 0 ) ∩ 1

̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅

( 7 ∩ 6 ∩ 5 ∩ 4 ∩ 3 ∩ 2 ∩ 0 ) ∩ 0

̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅

( 7 ∩ 6 ∩ 5 ∩ 4 ∩ 3 ∩ 2 ∩ 1 ).

5

Была построена схема для шифратора 8-3. Схема представлена ниже на рисунке 1.

Рисунок 1 – Схема шифратора 8-3.

После построения схемы было проведено моделирование в двух режимах timing и functional. Результаты моделирования представлены на рисунках 2 и 3.

Рисунок 2 – Результат моделирования в режиме timing.

6

Рисунок 3 – Результат моделирования в режиме function.

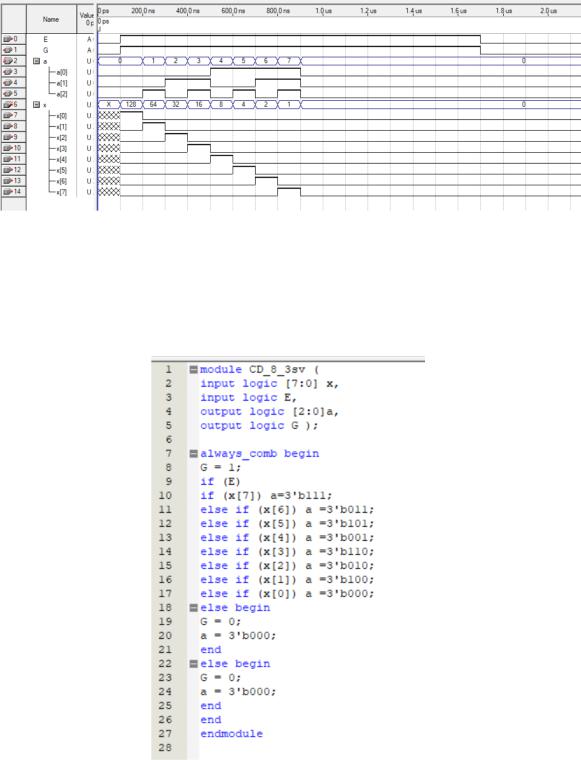

Был написан код для шифратора 8-3 на System Verilog. Код представлен ниже на рисунке 4.

Рисунок 4 – Код на System Verilog для шифратора 8-3.

После компиляции кода было проведено моделирование в двух режимах timing и functional. На рисунках 5 и 6 представлено моделирование в двух режимах.

7

Рисунок 5 – Результат моделирования кода в режиме timing.

Рисунок 6 - Результат моделирования кода в режиме function.

Ниже на рисунке 7 представлена схема из RTL viewer для HDL кода.

Рисунок 7 – Схема RTL.

8

2.2 Наращивание шифратора 8-3

Была построена таблица истинности для шифратора 16-4.

Таблица 2 – Таблица истинности для шифратора 16-4.

|

|

|

|

|

|

Входы |

|

|

|

|

|

|

|

|

|

Выходы |

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Е |

x15 |

x14 |

x13 |

x12 |

x11 |

x10 |

x9 |

x8 |

x7 |

x6 |

x5 |

x4 |

x3 |

x2 |

x1 |

x0 |

а0 |

a1 |

а2 |

а3 |

G |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

0 |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

9

Продолжение таблицы 2 - Таблица истинности для шифратора 16-4.

|

|

|

|

|

|

Входы |

|

|

|

|

|

|

|

|

|

Выходы |

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Е |

x15 |

x14 |

x13 |

x12 |

x11 |

x10 |

x9 |

x8 |

x7 |

x6 |

x5 |

x4 |

x3 |

x2 |

x1 |

x0 |

а0 |

a1 |

а2 |

а3 |

G |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Так же была построена схема наращенного шифратора 16-4. На рисунке

8 представлена схема.

Рисунок 8 – Схема шифратора 16-4

После компиляции схемы было проведено моделирование в двух режимах timing и functional. На рисунках 9 и 10 представлено моделирование в двух режимах.

Рисунок 9 – Моделирование шифратора 16-4 в режиме timing.

10

Рисунок 10 - Моделирование шифратора 16-4 в режиме functional.

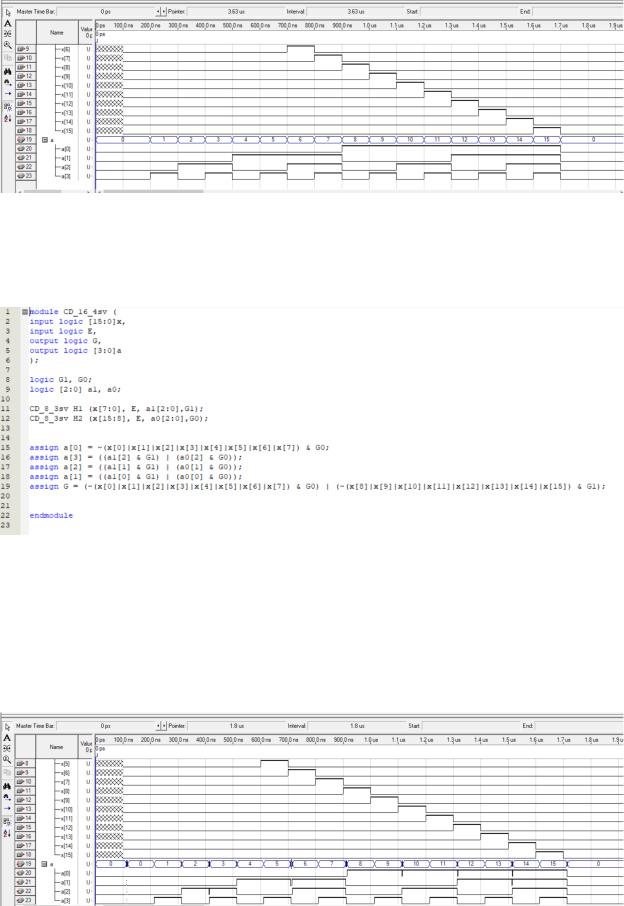

Был написан кода на System Verilog. Код представлен на рисунке 11.

Рисунок 11 - Код на System Verilog для шифратора 16-4.

После компиляции кода было проведено моделирование в двух режимах timing и functional. На рисунках 12 и 13 представлено моделирование в двух режимах.

Рисунок 12 – Моделирование кода шифратора 16-4 в режиме timing.