Отчеты / ЛАБ2

.1.pdf

11

Рисунок 13 - Моделирование кода шифратора 16-4 режиме function.

2.3Дешифратор 4-2

Втаблице 3 показана таблица истинности для дешифратора Таблица 3 – Таблица истинности для дешифратора 4-2

|

|

Выходы |

|

|

Входы |

|

|

|

|

|

|

|

|

|

|

х3 |

х2 |

|

х1 |

х0 |

а1 |

а0 |

Е |

|

|

|

|

|

|

|

|

х |

х |

|

х |

х |

х |

х |

0 |

|

|

|

|

|

|

|

|

0 |

0 |

|

0 |

1 |

0 |

0 |

1 |

|

|

|

|

|

|

|

|

0 |

0 |

|

1 |

0 |

0 |

1 |

1 |

|

|

|

|

|

|

|

|

0 |

1 |

|

0 |

0 |

1 |

0 |

1 |

|

|

|

|

|

|

|

|

1 |

0 |

|

0 |

0 |

1 |

1 |

1 |

|

|

|

|

|

|

|

|

Были построены формулы для базиса И, ИЛИ, НЕ:

̅̅̅̅̅̅; х0 = Е ∩ а1 ∩ а0

̅̅̅;

х1 = Е ∩ а1 ∩ а0

̅̅̅; х2 = Е ∩ а1 ∩ а0

х3 = Е ∩ а1 ∩ а0.

12

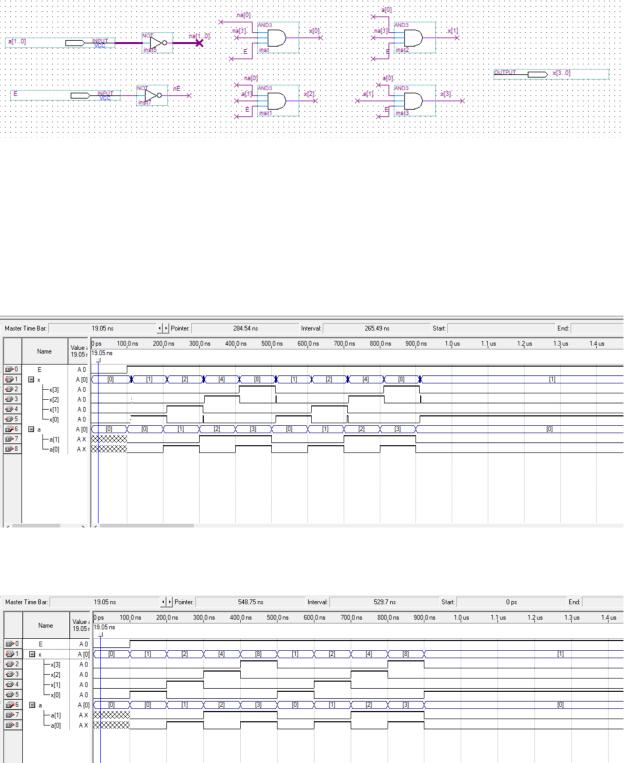

Для дешифратора 4-2 была построена схема. На рисунке 14

представлена схема.

Рисунок 14 – Схема дешифратора 4-2.

После компиляции схемы было проведено моделирование в двух режимах timing и functional. На рисунках 15 и 16 представлено моделирование в двух режимах.

Рисунок 15 – Моделирование схемы в режиме timing.

Рисунок 16 – Моделирование схемы в режиме functional.

13

После моделирования был написан кода для дешифратора 4-2 на System Verilog. Код представлен на рисунке 17.

Рисунок 17 - Код на System Verilog для дешифратора 4-2.

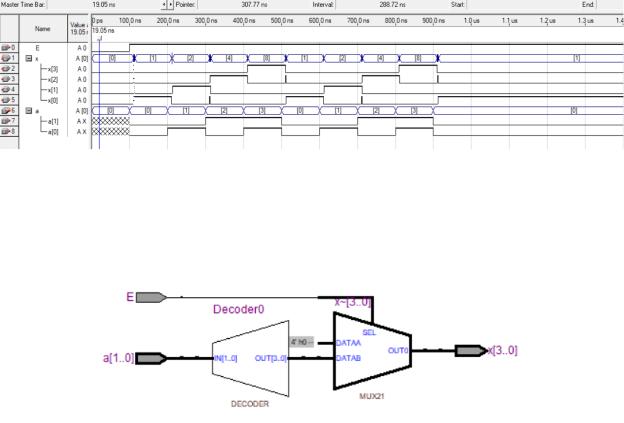

После компиляции кода было проведено моделирование в двух режимах timing и functional. На рисунках 18 и 19 представлено моделирование в двух режимах.

Рисунок 18 – Результат моделирования в режиме timing.

14

Рисунок 19 – Результат моделирования в режиме function.

Ниже на рисунке 20 представлена схема из RTL viewer для HDL кода.

Рисунок 20 – Схема TRL.

15

2.4 Наращивание дешифратора 4-2

Была построена таблица истинности для дешифратора 8-3

Таблица 4 – таблица истинности для дешифратора 8-3

|

|

|

Выходы |

|

|

|

|

Входы |

|

||

|

|

|

|

|

|

|

|

|

|

|

|

х7 |

х6 |

х4 |

х4 |

х3 |

х2 |

х1 |

х0 |

а2 |

а1 |

а0 |

Е |

|

|

|

|

|

|

|

|

|

|

|

|

х |

х |

х |

х |

х |

х |

х |

х |

х |

х |

х |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

Была построена схема для дешифратора 8-3. На рисунке 21 представлена

схема.

16

Рисунок 21 – Схема наращенного дешифратора 8-3.

После компиляции схемы было проведено моделирование в двух режимах timing и functional. На рисунках 22 и 23 представлено моделирование в двух режимах.

Рисунок 22 – Моделирование схемы в режиме timing.

Рисунок 23 – Моделирование схемы в режиме function.

17

Был написан код на System Verilog для дешифратора 8-3. Код представлен на рисунке 24.

Рисунок 24 - Код на System Verilog для дешифратора 8-3.

После компиляции кода было проведено моделирование в двух режимах timing и functional. На рисунках 25 и 26 представлено моделирование в двух режимах.

Рисунок 25 – Моделирование схемы в режиме timing.

Рисунок 26 – Моделирование схемы в режиме function.

18

2.5 Приоритетный шифратор 10-4

Была построена таблица истинности для приоритетного шифратора 10-4.

Таблица 5 – Таблица истинности для приоритетного шифратора

|

|

|

|

|

Входы |

|

|

|

|

|

|

|

|

Выходы |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

E |

x9 |

x8 |

x7 |

x6 |

x5 |

|

x4 |

x3 |

x2 |

x1 |

x0 |

3 |

2 |

1 |

|

0 |

G |

E0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

x |

x |

x |

x |

x |

|

x |

x |

x |

x |

x |

0 |

0 |

0 |

|

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

x |

x |

x |

x |

|

x |

x |

x |

x |

x |

1 |

0 |

0 |

|

1 |

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

1 |

x |

x |

x |

|

x |

x |

x |

x |

x |

1 |

0 |

0 |

|

0 |

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

1 |

x |

x |

|

x |

x |

x |

x |

x |

0 |

1 |

1 |

|

1 |

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

0 |

1 |

x |

|

x |

x |

x |

x |

x |

0 |

1 |

1 |

|

0 |

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

0 |

0 |

1 |

|

x |

x |

x |

x |

x |

0 |

1 |

0 |

|

1 |

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

0 |

0 |

0 |

|

1 |

x |

x |

x |

x |

0 |

1 |

0 |

|

0 |

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

0 |

0 |

0 |

|

0 |

1 |

x |

x |

x |

0 |

0 |

1 |

|

1 |

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

1 |

x |

x |

0 |

0 |

1 |

|

0 |

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

0 |

1 |

x |

0 |

0 |

0 |

|

1 |

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

|

0 |

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Были построены формулы для базиса ИЛИ-НЕ:

G̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅;

=E (x9 x8 x7 x6 x5 x4 x3 x2 x1 x0)

̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅ |

|

|

E0= E x9 x8 x7 x6 x5 x4 x3 x2 x1 x0; |

|

|

̅̅̅̅̅̅̅̅̅̅ |

̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅ |

|

a0=E (x9 7 8 9 |

5 6 7 8 9 3 |

|

̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅ |

̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅ |

; |

4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 |

||

|

|

|

19 |

|

a1=E (x7 |

̅̅̅̅̅̅̅̅̅̅ |

̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅ |

3 |

|

8 |

9 |

6 7 8 9 |

||

̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅ |

2 |

̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅ |

||

5 6 7 8 |

9 |

3 4 5 6 |

7 8 9); |

|

̅̅̅̅̅̅̅̅̅̅ |

̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅ |

̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅ |

|

a2 =E (x7 8 9 |

6 7 8 9 |

5 6 7 8 9 |

̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅ ;4 5 6 7 8 9)

a3= ̅̅̅ .

E ( 9 9 8)

Была построена схема приоритетного шифратора 10-4. Схема показана на рисунке 27.

Рисунок 27 – Схема приоритетного шифратора 10-4.

После компиляции схемы было проведено моделирование в двух режимах timing и functional. На рисунках 28 и 29 представлено моделирование в двух режимах.

Рисунок 28 – Моделирование схемы в режиме timing.

20

Рисунок 29 – Моделирование схемы в режиме functional.

Был написан код на System Verilog для приоритетного шифратора 10-4.

Код представлен ниже на рисунке 30.

Рисунок 30 Код на System Verilog для приоритетного шифратора 10-4.