Отчеты / ЛАБ7

.1.pdfМинистерство образования и науки Российской Федерации Федеральное государственное бюджетное образовательное учреждение высшего профессионального образования

«ТОМСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ СИСТЕМ УПРАВЛЕНИЯ И РАДИОЭЛЕКТРОНИКИ» (ТУСУР)

Кафедра комплексной информационной безопасности электронно-

вычислительных систем (КИБЭВС)

ПРИМЕНЕНИЕ РЕГИСТРОВ И СЧЕТЧИКОВ Отчет по лабораторной работе №7

по дисциплине «Электроника и схемотехника 2»

Вариант №5

Выполнил:

Студент гр. 710-2

_______ _____Кузьмина А.А.

__.05.2022

Принял: преподаватель каф. КИБЭВС

_______ А.С. Семенов

__.05.2022

Томск - 2022

2

1 Введение

Цель работы: получение навыков совместно применять регистры и

счётчики.

Задание:

1.Составить таблицы истинности для всех 4-х функций и обозначить в таблице порядок разрядов (старший и младший). Порядок разрядов во всех таблицах должен совпадать.

2.Для выполнения 4-х параллельных операций над полубайтом организовать приём и выдачу данных согласно варианту из таблицы. Собрать необходимую схему, используя встроенные блоки регистров (lpm_dff,

lpm_shiftreg).

3. Создать схемы, которые с помощью регистров обеспечат «чистый» выходной сигнал для асинхронного и синхронного счётчиков своего варианта из ЛБ5.

4.Промоделировать работу схем в двух режимах. Провести анализ результатов моделирования разных режимов.

5.Сверить результаты моделирования с составленными таблицами истинности.

6.Повторить п. 2-5, только для описания устройств вместо схем на холстах .bdf использовать заданный вариантом HDL.

Задание по варианту:

1.Прием: E +, L L, R s;

2.Выдача: E -, U P, RD 1;

3.HDL: VHDL.

3

2 Ход работы

2.1 Вычислитель функций Составим таблицу истинности для следующих функций:

F(1) = x y * z v w;

F(2) = x y * (̅̅̅̅̅̅̅);

F(3) = ̅̅̅̅̅̅̅;

F(4) = ̅̅̅̅̅̅̅ .

Таблица истинности для функций представлена ниже.

Таблица 1 – Таблица истинности функций.

|

Вход |

|

|

|

Выход |

|

||

|

|

|

|

|

|

|

|

|

W(d3) |

X(d2) |

Y(d1) |

Z(d0) |

F1 |

F2 |

|

F3 |

F4 |

|

|

|

|

|

|

|

|

|

0 |

0 |

0 |

0 |

0 |

0 |

|

1 |

1 |

|

|

|

|

|

|

|

|

|

0 |

0 |

0 |

1 |

0 |

0 |

|

0 |

1 |

|

|

|

|

|

|

|

|

|

0 |

0 |

1 |

0 |

0 |

1 |

|

1 |

1 |

|

|

|

|

|

|

|

|

|

0 |

0 |

1 |

1 |

1 |

0 |

|

0 |

1 |

|

|

|

|

|

|

|

|

|

0 |

1 |

0 |

0 |

1 |

1 |

|

1 |

1 |

|

|

|

|

|

|

|

|

|

0 |

1 |

0 |

1 |

1 |

1 |

|

0 |

1 |

|

|

|

|

|

|

|

|

|

0 |

1 |

1 |

0 |

1 |

0 |

|

1 |

0 |

|

|

|

|

|

|

|

|

|

0 |

1 |

1 |

1 |

0 |

1 |

|

1 |

0 |

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

0 |

1 |

0 |

|

0 |

1 |

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

1 |

1 |

0 |

|

0 |

1 |

|

|

|

|

|

|

|

|

|

4

Таблица 1 – Продолжение таблицы истинности функций.

|

Вход |

|

|

|

Выход |

|

||

|

|

|

|

|

|

|

|

|

W(d3) |

X(d2) |

Y(d1) |

Z(d0) |

F1 |

F2 |

|

F3 |

F4 |

|

|

|

|

|

|

|

|

|

1 |

0 |

1 |

0 |

1 |

0 |

|

0 |

1 |

|

|

|

|

|

|

|

|

|

1 |

0 |

1 |

1 |

1 |

0 |

|

0 |

1 |

|

|

|

|

|

|

|

|

|

1 |

1 |

0 |

0 |

1 |

1 |

|

0 |

1 |

|

|

|

|

|

|

|

|

|

1 |

1 |

0 |

1 |

1 |

1 |

|

0 |

1 |

|

|

|

|

|

|

|

|

|

1 |

1 |

1 |

0 |

1 |

1 |

|

1 |

0 |

|

|

|

|

|

|

|

|

|

1 |

1 |

1 |

1 |

1 |

1 |

|

1 |

1 |

|

|

|

|

|

|

|

|

|

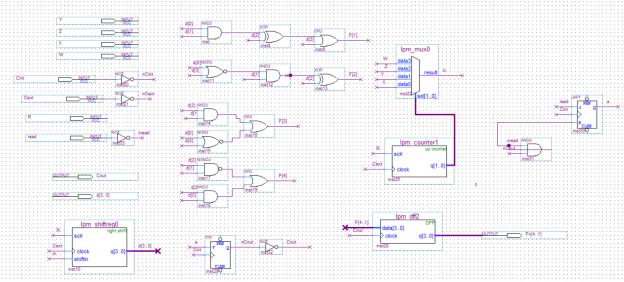

Схема для вычислителя функции представлена на рисунке 1.

Рисунок 1 – Схема вычислителя функции.

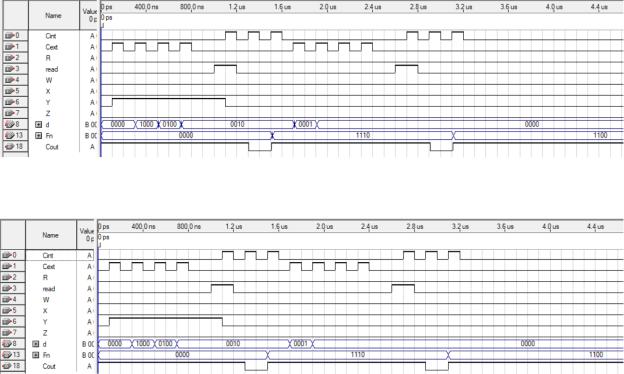

После построения схемы было проведено моделирование в двух режимах timing и functional. Результаты моделирования представлены на рисунках 2 и 3.

5

Рисунок 2 – Результат моделирования в режиме timing.

Рисунок 3 – Результат моделирования в режиме function.

Для вычислителя функции был написан код на VHDL. Код представлен

ниже:

library ieee;

use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; use ieee.numeric_std.all;

entity FuncRegvh is port (

Cext, Cint, x, y, z, w, R, RD: in std_logic;

Cout: out std_logic;

Fn: out std_logic_vector (4 downto 1) );

end;

architecture synth of FuncRegvh is

6 signal d: std_logic_vector (3 downto 0); signal F: std_logic_vector (4 downto 1); type statetype is (S0, S1, S2, S3); signal state: statetype;

signal K, L, nL, T, E, I, U: std_logic; begin

process(Cext) begin

if rising_edge(Cext) then

if (R = '1') then d <= "0000"; else

case (state) is when S0 => d(0) <= X;

E <= X; state <= S1; when S1 => d(1) <= E; d(0) <= Y; I <= Y; state <= S2; when S2 => d(2) <= E; d(1) <= I; d(0) <= Z; U <= Z;

7

state <= S3; when S3 => d(3) <= E; d(2) <= I; d(1) <= U; d(0) <= W; state <= S0;

when others => d <= "0000"; end case;

end if; end if;

end process; Cout <= nL; nL <= not L;

T <= L and (not (RD));

F(1) <= d(3) xor ((d(2) and d(1)) or d(0));

F(2) <= ((d(0) nor d(3)) and d(1)) xor d(2);

F(3) <= (d(2) and d(1)) or (d(0) nor d(3));

F(4) <= (d(2) nand d(1)) or (d(3) and d(0)); process (Cint) begin

if rising_edge (Cint) then

if ((RD = '1') and (T = '1')) then K <= not K; elsif (RD = '1') then K <= '1';

elsif (T = '1') then K <= '0'; end if;

8

if (K = '1') then L <= not(L);

end if;

end if;

end process;

process (nL) begin

if rising_edge (nL) then Fn <= (F(1)& F(2)& F(3)& F(4));

end if;

end process;

end;

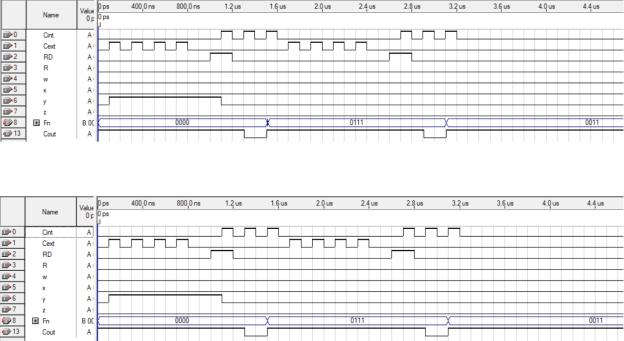

После компиляции кода было проведено моделирование в двух режимах timing и functional. На рисунках 4 и 5 представлено моделирование в двух режимах.

Рисунок 4 – Результат моделирования кода в режиме timing.

Рисунок 5 – Результат моделирования кода в режиме function.

9

2.2 Асинхронный счетчик с выходным буфером

Для асинхронного счетчика с выходным буфером была построена таблица истинности. Таблица представлена ниже.

Таблица 2 – Таблица истинности для асинхронного счётчика с выходным буфером.

№ сигнала |

Q4 |

Q3 |

Q2 |

Q1 |

Q0 |

|

|

|

|

|

|

0 |

0 |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

1 |

1 |

1 |

0 |

0 |

0 |

|

|

|

|

|

|

2 |

1 |

0 |

1 |

1 |

1 |

|

|

|

|

|

|

3 |

1 |

0 |

1 |

1 |

0 |

|

|

|

|

|

|

4 |

1 |

0 |

1 |

0 |

1 |

|

|

|

|

|

|

5 |

1 |

0 |

1 |

0 |

0 |

|

|

|

|

|

|

6 |

1 |

0 |

0 |

1 |

1 |

|

|

|

|

|

|

7 |

1 |

0 |

0 |

1 |

0 |

|

|

|

|

|

|

8 |

1 |

0 |

0 |

0 |

1 |

|

|

|

|

|

|

9 |

1 |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

10 |

0 |

1 |

1 |

1 |

1 |

|

|

|

|

|

|

11 |

0 |

1 |

1 |

1 |

0 |

|

|

|

|

|

|

12 |

0 |

1 |

1 |

0 |

1 |

|

|

|

|

|

|

13 |

0 |

1 |

1 |

0 |

0 |

|

|

|

|

|

|

14 |

0 |

1 |

0 |

1 |

1 |

|

|

|

|

|

|

15 |

0 |

1 |

0 |

1 |

0 |

|

|

|

|

|

|

10

Таблица 2 – Продолжение таблицы истинности для асинхронного счетчика с выходным буфером.

№ сигнала |

Q4 |

Q3 |

Q2 |

Q1 |

Q0 |

|

|

|

|

|

|

16 |

0 |

1 |

0 |

0 |

1 |

|

|

|

|

|

|

17 |

0 |

1 |

0 |

0 |

0 |

|

|

|

|

|

|

18 |

0 |

0 |

1 |

1 |

1 |

|

|

|

|

|

|

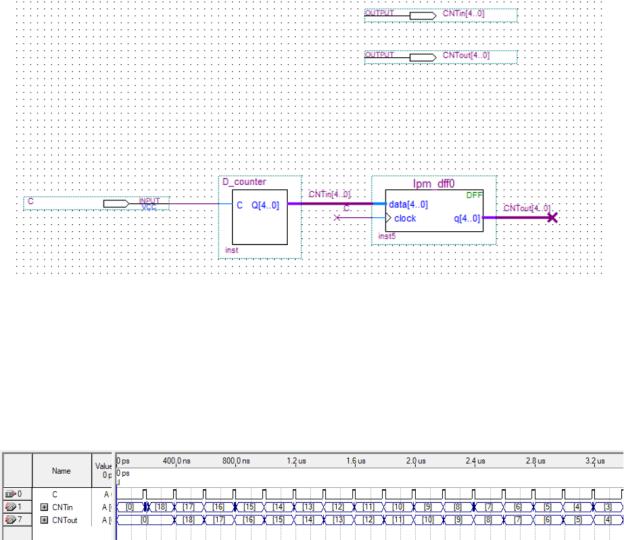

Схема для асинхронного счетчика представлена на рисунке 6.

Рисунок 6 – Схема асинхронного счётчика с выходным буфером

После построения схемы было проведено моделирование в двух режимах timing и functional. Результаты моделирования представлены на рисунках 7 и 8.

Рисунок 7 – Результат моделирования в режиме timing.