Отчеты / ЛАБ6

.1.pdfМинистерство образования и науки Российской Федерации Федеральное государственное бюджетное образовательное учреждение высшего профессионального образования

«ТОМСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ СИСТЕМ УПРАВЛЕНИЯ И РАДИОЭЛЕКТРОНИКИ» (ТУСУР)

Кафедра комплексной информационной безопасности электронно-

вычислительных систем (КИБЭВС)

ИЗУЧЕНИЕ РАБОТЫ РЕГИСТРОВ

Отчет по лабораторной работе №6

по дисциплине «Электроника и схемотехника 2»

Вариант №5

Выполнил:

Студент гр. 710-2

_______ _____Кузьмина А.А.

__.05.2022

Принял: преподаватель каф. КИБЭВС

_______ А.С. Семенов

__.05.2022

Томск - 2022

2

1 Введение

Цель работы: изучение регистров и изучение их принципов построения и работы.

Задание:

1.Составьте таблицы функционирования для схем из таблицы согласно варианту;

2.Соберите схемы заданных регистров согласно варианту;

3.Промоделируйте работу всех схем в двух режимах. Проведите анализ результатов моделирования разных режимов;

4.Сверьте результаты моделирования с составленными таблицами функционирования и расчётами;

5.Повторите п. 2-4, только для описания устройств вместо схем на холстах .bdf используйте заданный вариантом HDL.

Задание по варианту:

1.SISO: ↔ – L, L – a, R – s, S – 16;

2.Универсальный: in – P, out – S, ↔ – R, R – s, S – 8;

3.PIPO: L – s, R – a, S – 10;

4.HDL – SystemVerilog.

3

2 Ход работы

2.1 Регистр SISO

Таблица функционирования для SISO регистра представлена ниже.

Таблица 1 – Таблица функционирования для SISO.

|

|

Вход |

|

Выход |

№ Сигнала |

|

|

|

|

L |

R |

S |

Q |

|

|

|

|

|

|

0 |

0 |

0 |

b1 |

0 |

|

|

|

|

|

1 |

0 |

0 |

b2 |

0 |

|

|

|

|

|

2 |

0 |

0 |

b3 |

0 |

|

|

|

|

|

3 |

0 |

0 |

b4 |

0 |

|

|

|

|

|

4 |

0 |

0 |

b5 |

0 |

|

|

|

|

|

5 |

0 |

0 |

b6 |

0 |

|

|

|

|

|

6 |

0 |

0 |

b7 |

0 |

|

|

|

|

|

7 |

0 |

0 |

b8 |

0 |

|

|

|

|

|

8 |

0 |

0 |

b9 |

0 |

|

|

|

|

|

9 |

0 |

0 |

b10 |

0 |

|

|

|

|

|

10 |

0 |

0 |

b11 |

0 |

|

|

|

|

|

11 |

0 |

0 |

b12 |

0 |

|

|

|

|

|

12 |

0 |

0 |

b13 |

0 |

|

|

|

|

|

13 |

0 |

0 |

b14 |

0 |

|

|

|

|

|

14 |

0 |

0 |

b15 |

0 |

|

|

|

|

|

4

Таблица 1 – Продолжение таблицы функционирования для SISO.

|

Вход |

Выход |

|

Вход |

№ Сигнала |

|

|

№ Сигнала |

|

|

|

|

|

|

15 |

0 |

0 |

b16 |

b1 |

|

|

|

|

|

16 |

0 |

0 |

b17 |

b2 |

|

|

|

|

|

17 |

1 |

0 |

b18 |

b18 |

|

|

|

|

|

18 |

0 |

0 |

b19 |

b4 |

|

|

|

|

|

19 |

0 |

1 |

b20 |

0 |

|

|

|

|

|

20 |

0 |

0 |

b21 |

0 |

|

|

|

|

|

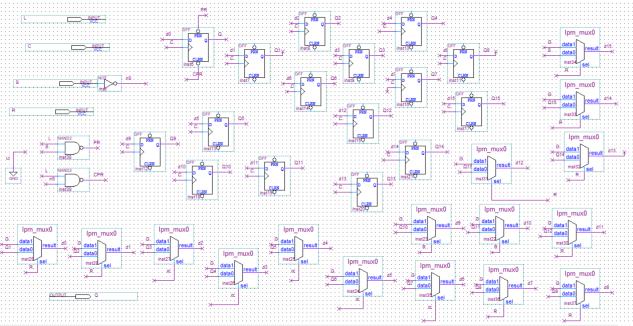

На рисунке 1 изображена схема регистра SISO.

Рисунок 1 – Схема регистра SISO.

5

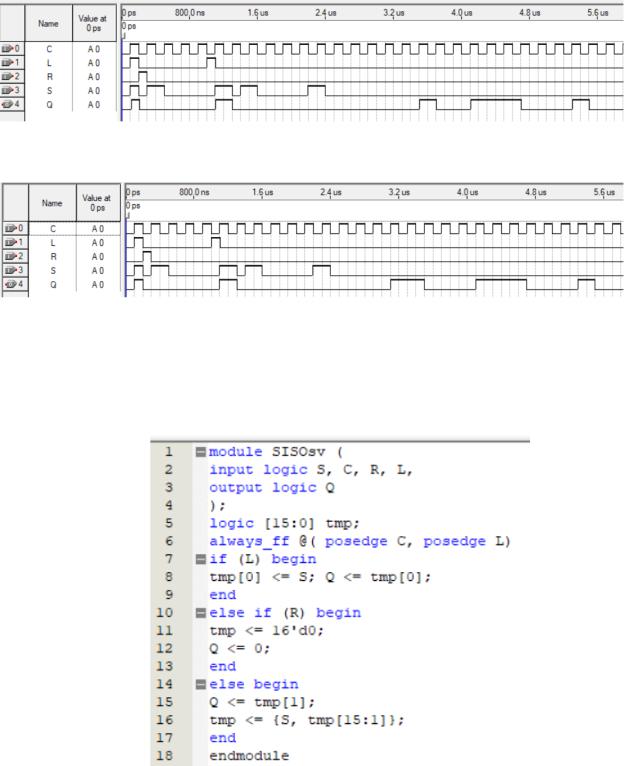

После построения схемы было проведено моделирование в двух режимах timing и functional. Результаты моделирования представлены на рисунках 2 и 3.

Рисунок 2 – Результат моделирования в режиме timing.

Рисунок 3 – Результат моделирования в режиме function.

Для регистра SISO был написан код на system Verilog. Код представлен ниже на рисунке 4.

Рисунок 4 – Код на system Verilog.

6

После компиляции кода было проведено моделирование в двух режимах timing и functional. На рисунках 5 и 6 представлено моделирование в двух режимах.

Рисунок 5 – Результат моделирования кода в режиме timing.

Рисунок 6 – Результат моделирования кода в режиме function.

7

2.2 Универсальный регистр

|

Таблица |

функционирования |

для |

универсального |

регистра |

|||||||

представлена ниже. |

|

|

|

|

|

|

|

|

|

|||

Таблица 2 – Таблица функционирования универсального регистра. |

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

№ |

|

|

|

|

|

Вход |

|

|

|

|

Q |

|

Сигнала |

|

|

|

|

|

|

|

|

|

|

|

|

R |

L |

d0 |

d1 |

d2 |

d3 |

d4 |

d5 |

d6 |

d7 |

|

||

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

|

0 |

1 |

b0 |

b1 |

b2 |

b3 |

b4 |

b5 |

b6 |

b7 |

b7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

0 |

0 |

x |

x |

x |

x |

x |

x |

x |

x |

b6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

2 |

|

0 |

0 |

x |

x |

x |

x |

x |

x |

x |

x |

b5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

3 |

|

0 |

0 |

x |

x |

x |

x |

x |

x |

x |

x |

b4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

4 |

|

0 |

0 |

x |

x |

x |

x |

x |

x |

x |

x |

b3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

5 |

|

0 |

0 |

x |

x |

x |

x |

x |

x |

x |

x |

b2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

6 |

|

0 |

0 |

x |

x |

x |

x |

x |

x |

x |

x |

b1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

7 |

|

1 |

0 |

x |

x |

x |

x |

x |

x |

x |

x |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

8 |

|

0 |

0 |

x |

x |

x |

x |

x |

x |

x |

x |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

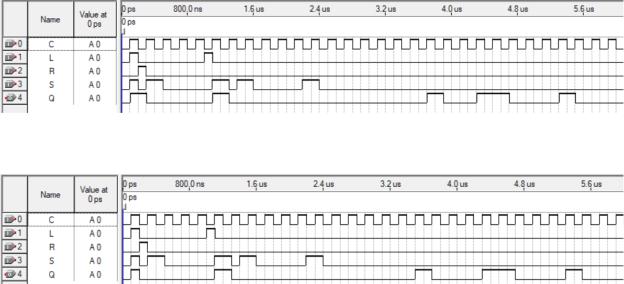

Ниже на рисунке 7 показана схема для универсального регистра.

8

Рисунок 7 – Схема регистра PISO.

После построения схемы было проведено моделирование в двух режимах timing и functional. Результаты моделирования представлены на рисунках 8 и 9.

Рисунок 8 – Результат моделирования в режиме timing.

Рисунок 9 – Результат моделирования в режиме function.

9

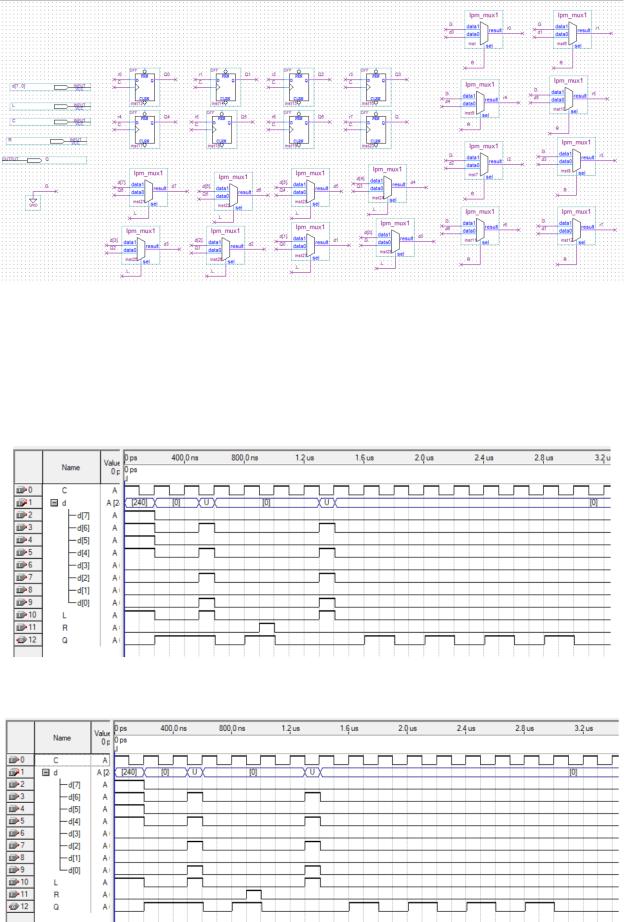

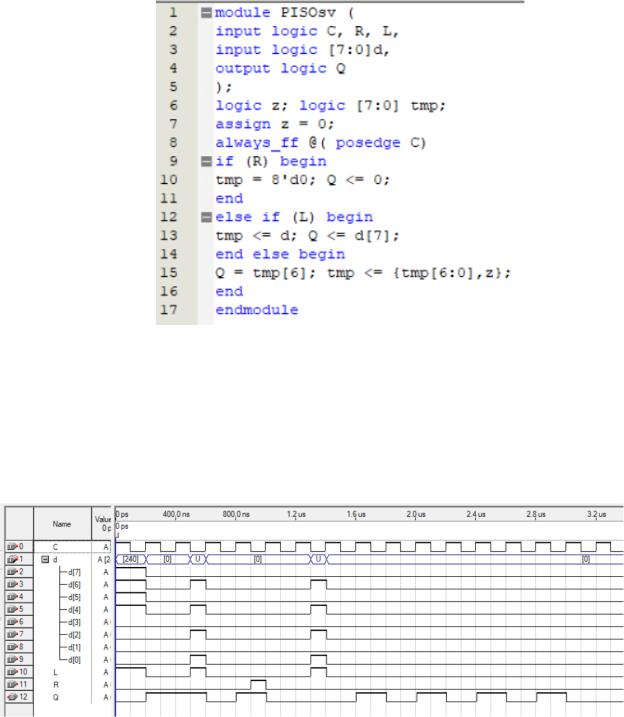

Для универсального регистра был написан код на system Verilog. Код представлен ниже на рисунке 10.

Рисунок 10 – Код на system Verilog.

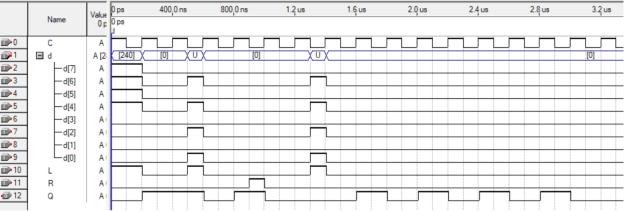

После компиляции кода было проведено моделирование в двух режимах timing и functional. На рисунках 11 и 12 представлено моделирование в двух режимах.

Рисунок 11 – Результат моделирования кода в режиме timing.

10

Рисунок 12 – Результат моделирования кода в режиме function.