- •Введение

- •1. Физическая верификация. Характеризация топологии. Цели и задачи. Этапы верификации (drc, lvs, rcx). Моделирование с учетом паразитных элементов

- •2. Паразитные элементы. Механизмы возникновения паразитных элементов, их типы. Паразитные эффекты в топологии аналоговых устройств, их физическая сущность

- •3. Обзор программ верификации. Программы верификации Diva, Assura, Calibre

- •4. Программа верификации Diva. Основы работы. Проверка проектных норм (drc). Проверка на соответствие топологии электрической схеме (lvs). Экстракция паразитных параметров (rcx)

- •5. Программа верификации Assura. Основы работы. Проверка проектных норм (drc). Проверка на соответствие топологии электрической схеме (lvs). Экстракция паразитных параметров (rcx)

- •6. Программа верификации Calibre. Основы работы. Проверка проектных норм (drc). Проверка на соответствие топологии электрической схеме (lvs). Экстракция паразитных параметров

- •7. Моделирование с учетом паразитных элементов. Создание файла конфигураций моделирования и его настройка. Моделирование

- •8. Подготовка к производству. Правила передачи топологии. Понятие gds файла. Подготовка управляющего файла в формате gdsii

- •Заключение

- •Библиографический список

- •Оглавление

- •394026 Воронеж, Московский просп., 14

ФГБОУ ВПО

«Воронежский государственный технический университет»

Ю.С. Балашов Д.В. Шеховцов

Физическая и функциональная верификация

топологии аналоговых устройств сверхбольших интегральных схем

Утверждено редакционно-издательским советом

университета в качестве учебного пособия

Воронеж 2011

УДК 621.396.6

Балашов Ю.С. Физическая и функциональная верификация топологии аналоговых устройств сверхбольших интегральных схем: учеб. пособие / Ю.С. Балашов, Д.В. Шеховцов. Воронеж: ФГБОУ ВПО «Воронежский государственный технический университет», 2011. 83 с.

В учебном пособии рассматриваются механизм возникновения паразитных элементов и паразитных эффектов, особенностей их проявления, а также способы защиты топологии от этих явлений, которые необходимо учитывать при разработке аналоговых блоков с использованием субмикронной технологии 90 нм.

Издание соответствует требованиям Федерального государственного образовательного стандарта высшего профессионального образования по направлению 211000 «Конструирование и технология электронных средств», магистерской программе 211000.68 «Информационные технологии проектирования электронных средств, выполненных по субмикронной технологии»), дисциплине «Физическая и функциональная верификация топологии аналоговых устройств сверхбольших интегральных схем». Учебное пособие также предназначено для слушателей профессиональной переподготовки специалистов (программа «Схемотехническое проектирование аналоговых устройств сверхбольших интегральных схем (СБИС) с топологическими нормами 90 нм»).

Издание предназначено для студентов очной формы обучения.

Учебное пособие подготовлено в электронном виде в текстовом редакторе MS Word XP и содежится в файле Шеховцов Уч.пособ.doc

Ил. 36. Библиогр.: 5 назв.

Рецензенты: ОАО «Концерн Созвездие» (директор Центра

системного проектирования В.И. Конопкин);

канд. техн. наук, доц. Е.Д. Алперин

© Балашов Ю.С., Шеховцов Д.В., 2011

© Оформление. ФГБОУ ВПО «Воронежский

государственный технический университет», 2011

Введение

Использование субмикронной технологии 90 нм для разработки аналоговых блоков является невозможным без наличия знаний о формировании в топологии приборов, в том числе паразитных элементов, возникающих в топологических структурах и влияющих на работоспособность и электрические характеристики схемы. Поэтому важным этапом в освоении дисциплины является изучение механизма возникновения паразитных элементов и паразитных эффектов, особенностей их проявления, а также способов защиты топологии от указанных паразитных явлений.

Для выполнения комплекса физической верификации необходимо иметь соответствующие знания о средствах верификации САПР. Обзор основных используемых программ верификации дает общее представление о назначении, принципах выполнения верификации в данных программах, здесь раскрываются положительные и отрицательные моменты их функционирования, схожесть и различие. Успешное освоение программ верификации требует детального знания правил выполнения верификации и особенностей работы в каждой из них, поэтому большая часть лекционного материала посвящена раскрытию вопроса работы в приложениях верификации Diva, Assura и Calibre.

Работоспособность разработанной топологии должна подтверждаться с помощью моделирования с учетом паразитных элементов. Это требует изучения способов экстракции электрических схем с паразитными приборами и правил конфигурирования среды симуляции, а также процесса моделирования для оценки работоспособности экстрактированной схемы.

Проектирование аналоговых устройств и блоков завершается этапом формирования управляющей информации и передачей ее производителю, что требует соответствующих знаний о формировании управляющей информации в индустриальном формате GDSII и правил ее формирования.

Все поставленные задачи в полном объеме раскрываются в представленном конспекте лекций по дисциплине.

1. Физическая верификация. Характеризация топологии. Цели и задачи. Этапы верификации (drc, lvs, rcx). Моделирование с учетом паразитных элементов

Проектирование топологии завершается этапом физической верификации и экстракции паразитных параметров. Этап физической верификации является неотъемлемой частью проектирования аналоговых блоков по технологии 90 нм. Субмикронные КМОП-технологии с топологическими нормами 90 нм требуют крайне тщательного подхода к проектированию, а следовательно, и верификации топологии, последующему анализу работы блока, т.к. любая неучтенная ошибка способна существенно повлиять как на электрические характеристики, так и на общую работоспособность разрабатываемых аналоговых блоков.

Физическая верификация включает в себя:

- проверку топологии на соответствие правилам и нормам проектирования (КТТ – конструкторско-технологические требования) технологического процесса;

- извлечение из топологии электрической схемы и последующую верификацию полученной схемы и электрической схемы проекта.

Следующей важной частью разработки является экстракция электрической схемы с паразитными элементами из проверенной топологии. После завершения этапа физической верификации производится моделирование экстрактированной схемы с паразитными элементами и трансляция топологии в управляющую информацию в формате GDSII для изготовления фотошаблонов либо оформление разработанного модуля в виде сложно-функционального блока (СФ-блока).

Основными целями физической верификации являются:

- подтверждение соответствия разработанной топологии КТТ;

- подтверждение соответствия разработанной топологии и электрической схемы.

Основные задачи физической верификации и ее этапы:

1. Проверка топологии на соответствие нормам КТТ, устранение допущенных ошибок.

2. Извлечение электрической схемы из топологии и верификация экстрактированной из топологии электрической схемы и принципиальной электрической схемы, исправление ошибок.

3. Извлечение из топологии списка соединений и устройств с паразитными элементами для последующего моделирования в виде электрической схемы или нетлиста в требуемом формате.

Современные средства САПР, используемые для разработки аналогового блока, позволяют осуществить полный комплекс физической верификации и экстракции электрической схемы с паразитными параметрами. Приложения, используемые для физической верификации проектов, выполненных по технологии 90 нм, должны обладать высоким быстродействием. Таковыми являются приложения Diva, Assura и Calibre, позволяющие осуществлять требуемые проверки DRC и LVS и экстракцию паразитных элементов RCX.

Проверка правил проектирования (DRC). Топология проектируемого блока представляет собой пересечение и наложение слоев. Для каждой отдельно взятой технологии существуют конструкторско-технологические правила расположения данных слоев. Эти правила называются конструкторско-технологическими требованиями (КТТ) и представляют собой набор проектных норм, таких как всевозможные зазоры, как между слоями, так и внутри слоя, минимальные/максимальные размеры геометрических фигур, правила пересечения и наложения слоев.

На этапе проверки правил проектирования проверяются геометрические соотношения слоев на соответствие конструкторско-технологическим нормам технологического процесса (DRC – Design Rule Checking). Все нормы КТТ определены в управляющем файле проверки DRC. Данный файл поставляется в составе библиотеки заводом-изготовителем либо разрабатывается самостоятельно при условии знания технологического процесса и требований КТТ.

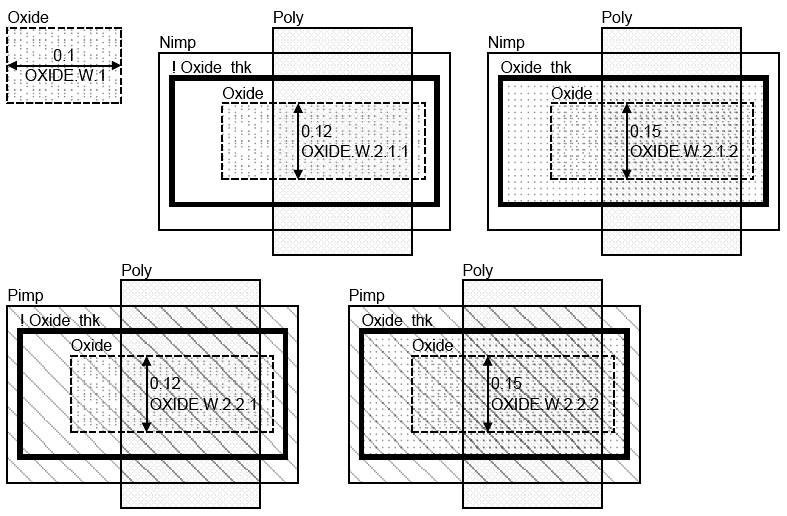

Правила конфигурации и размеров определяются как для каждого отдельно взятого слоя, так и для комбинации определенного слоя с другими топологическими слоями. На рисунке в качестве примера представлены правила формирования активных областей (oxide).

Правила проектирования активных областей

Размеры областей, указываемых в правилах обычно являются минимально/максимально допустимыми. Управляющий файл проверки разрабатывается в соответствии с форматом программы-верификатора и имеет определенную структуру, в состав которой входят:

- определение используемых базовых топологических слоев;

- переназначение базовых слоев в требуемые слои;

- определение проводящих слоев;

- правила формирования дополнительных слоев и фигур;

- правила определения геометрических размеров сформированных полигонов, их зазоров, пересечений и наложений;

- правила определения и вывода ошибок при нарушении требований КТТ.

Определение используемых базовых топологических слоев. Все структуры строятся на основе базовых топологических слоев, которые в последующем используются программой-верификатором для определения всех приборов топологии и, соответственно, проверки соблюдения правил проектирования этих приборов.

Переназначение базовых слоев. Данный прием довольно часто используется при проверке правил проектирования для построения полигонов с помощью различных геометрических операций (сложение, вычитание, исключение и т.д.) в случае, если один и тот же слой используется для формирования требуемых структур по различным алгоритмам.

Определение проводящих слоев. Проводящие слои используются для формирования межслойных контактов и должны быть определены в качестве контактирующих сразу после формирования необходимых дополнительных слоев.

Правила формирования требуемых слоев и фигур. Для формирования любых дополнительных слоев и фигур используется набор операндов-команд управления слоями, таких как Or, And, Not, AndNot, Straddle, Size и др. Дополнительные слои могут формироваться как на основе базовых, так и на основе уже сформированных дополнительных слоев и их всевозможных комбинаций

Правила определения геометрических размеров полигонов, их зазоров, пересечений и наложений. В требуемых случаях при определении размеров, зазоров и других величин сформированных слоев могут быть использованы упреждения – увеличение или уменьшение полного или частичного размера сформированных полигонов.

Правила определения и вывода ошибок при нарушении требований КТТ. Программа-верификатор определяет нарушения правил проектирования, руководствуясь командами-указаниями требуемых проверок. Основные команды:

- width – проверка ширины полигона;

- space – зазор между полигонами одного слоя;

- notch – внутренний зазор фигуры слоя.

Для каждой команды указывается минимальное или максимальное расстояние\зазор, при нарушении которого будет выведено сообщение об ошибке, включающее тип ошибки, требование нарушенной нормы и текущий ошибочный размер.

После завершения проверки правил проектирования выводится отчет о проверке. Найденные ошибки можно просмотреть с помощью пользовательского интерфейса программы-верификатора.

Экстракция электрической схемы и устройств из топологии (EXT). Извлечение списка соединений и устройств из топологии является необходимым важным подготовительным этапом последующей верификации. На этом этапе из структурных топологических слоев формируются все базовые устройства, такие как транзисторы, резисторы, диоды и др. и описываются их связи друг с другом. Так же производится измерение размеров построенных устройств и расчет их номинальных электрических параметров (сопротивления, емкости).

Для экстракции схемы используется управляющий файл экстракции, в состав которого входят:

- определение используемых базовых топологических слоев;

- переназначение базовых слоев в требуемые слои;

- определение проводящих слоев;

- правила формирования требуемых слоев, фигур и приборов;

- правила определения размеров и электрических номиналов приборов.

Определение используемых базовых топологических слоев, переназначение базовых слоев, определение проводящих слоев подобны используемым в управляющем файле проверки норм проектирования drc.rul.

Правила формирования приборов. Для формирования приборов используются команды формирования extractDevice. В команде указывается тип прибора, определяются его имя (из библиотеки, например npn, respol, cap) и терминалы.

После правил формирования следует список внешних контактирующих слоев, в который входят все терминальные слои приборов.

Правила определения размеров и электрических номиналов приборов. После определения каждого прибора топологии следуют правила расчета его номинала по его длине, ширине и площади. Для расчета номинала указывается формула, расчет производится на основе определенных геометрических параметров и имеющихся данных об удельных характеристиках слоя, таких как емкость, сопротивление и т.д.

Результатом экстракции является электрическая схема, обычно наложенная на топологическое представление разрабатываемого устройства с рассчитанными размерами и номиналами определенных приборов.

Верификация экстрактированной из топологии схемы с электрической принципиальной схемой (LVS). Верификация электрических схем является заключительным этапом проектирования топологии устройства. Для проведения верификации используется управляющий файл верификации, в структуру которого входят:

- процедуры компарации геометрических размеров сопоставленных приборов;

- процедуры сравнения номиналов электрических параметров сопоставленных приборов;

- процедуры объединения и компарации параллельных и последовательных структур, правила упрощения структур;

- правила верификации симметричных схем, таких как, например, логические схемы 2и, 3или и др., или многовходовые симметричные аналоговые схемы.

В правилах и процедурах компарации указывается коэффициент максимального рассогласования размеров и номиналов приборов. При превышении размеров и номиналов одного из сопоставленных приборов больше максимально допустимого будет выведено сообщение об ошибке, содержащее тип нарушения и размеры сопоставленных приборов.

После запуска верификации из указанных электрических схем формируются нетлисты (списки электрических соединений приборов), размеры и номиналы приборов в составе нетлиста. Программа верификатор, пользуясь расставленными терминалами, находит соответствие между узлами схем, цепями и приборами, ошибки подключения приборов и узлов, ошибки размеров и номиналов приборов, между которыми найдено соответствие. После верификации выводится отчет о выполненной проверке. Ошибки, возникшие в ходе проектирования и выявленные верификатором, позволяет отследить графический пользовательский интерфейс программы-верификатора. Основные ошибки, выводимые определенные верификатором:

- отсутствие соответствия между сетями и приборами;

- несоответствие сопоставленных сетей из-за разного количества подключенных приборов к сети в топологии и электрической схеме;

- несоответствие размеров сопоставленных приборов;

- неверное подключение сетей к выводам прибора, например, перепутаны местами входные сети прибора;

- отсутствует подключение терминала прибора к требуемой сети или подключение выполнено к другой сети;

- разорвана сеть, требуется объединить две сети в одну, при этом интерфейс выводит подсказку, какие сети необходимо объединить.

Моделирование с учетом паразитных элементов. Моделирование обычной электрической схемы, извлеченной из топологии в процессе экстракции даже при подтверждении полного ее соответствия электрической принципиальной схеме не гарантирует работоспособность проектируемого устройства. При анализе аналоговых блоков, разработанных с использованием технологий глубокого субмикронного диапазона, например 90 нм КМОП-технологии, требуется обязательный учет так называемых паразитных элементов. Паразитные элементы представляют собой неучтенные моделями приборов дополнительно присутствующие в топологии побочные компоненты, такие как сопротивление переходных контактов и проводников, межслойные емкости, индуктивности длинных проводников и др.

Для осуществления моделирования с учетов паразитных элементов требуется извлечение списка связей и устройств с паразитными элементами. Паразитные элементы экстрактируются с помощью управляющего файла экстракции, встраиваются в электрическую схему и могут существенно повлиять не только на расчетные параметры, вызвав их отклонение, но и на общую работоспособность устройства.

Электрическая схема, экстрактированная с паразитными элементами, имеет в своем составе огромный массив паразитных элементов, и общий объем элементов, многократно превышающий общее количество начальных структурных приборов схемы. Поэтому моделирование таких схем осуществляется на высокопроизводительных рабочих станциях, как правило, с использованием распределенных вычислительных мощностей, либо в многопроцессорном режиме.

Моделирование схемы с паразитными элементами может осуществляться в таких программах-симуляторах, как Spectre, UltraSim, Spice и др.