Учебное пособие 800343

.pdf

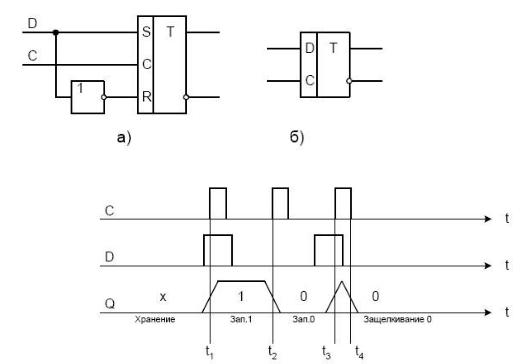

Рис. 2.10. Схема D-триггера

Рис. 2.11. Временная диаграмма синхронного статического D-триггера

Из временной диаграммы просматривается одна особенность синхронного статического D-триггера: на временном интервале t3 – t4 в триггер записывается последнее значение информационного сигнала, соответствующее моменту завершения синхроимпульса. Такой процесс называют «защелкиванием», а синхронный D-триггер со статическим управлением называют так же «триггерзащелка». Данные триггеры часто используют для реализации цифровых линий задержки, поскольку выходная информация (выход Q) задерживается относительно входной (вход D) на период синхроимпульса.

2.4.2 Синхронные триггеры с динамическим управлением

Синхронный двухступенчатый RS-триггер реализуется по принципу «ведущий - ведомый». При этом входная информация вначале записывается в ведущий триггер, а затем переносится в ведомый триггер, представляющий вторую ступень схемы.

Рассмотрим более простой способ построения такого триггера – на базе двух синхронных статических RS-триггеров с объединением тактовых входов через инвертор. Функциональная схема и условно-графическое обозначение двухступенчатого RS-триггера приведены на рис. 2.12 а, б. Функционирование триггера задается таблицей 2.5.

21

Рис. 2.12. Функциональная схема и условно-графическое обозначение двухступенчатого RS-триггера

Символы «↑» и «↓» в таблицах функционирования триггеров с динамическим управлением означают, что изменение состояния происходит по положительному или отрицательному перепаду тактового импульса. Символ «х» означает произвольное состояние входных сигналов.

Таблица 2.5

S |

R |

C |

Q n |

Режим |

х |

х |

0 |

Q n-1 |

Хранение |

0 |

0 |

х |

Q n-1 |

Хранение |

1 |

0 |

↓ |

1 |

Запись 1 |

0 |

1 |

↓ |

0 |

Запись 0 |

1 |

1 |

↓ |

з |

Запрещенный |

На базе синхронного RS-триггера с динамическим управлением легко реализуются все другие триггеры с динамическим управлением: Т-триггер, D- триггер и JK-триггер.

Схема синхронного двухступенчатого T-триггера и его условнографическое обозначение приведены на рис. 2.13 а, б. Функционирование триггера задается таблицей 2.6.

Рис. 2.13. Схема синхронного двухступенчатого T-триггера и его условнографическое обозначение

22

Таблица 2.6

T |

|

Q n |

Режим |

|

0 |

Q n-1 |

Хранение |

||

↓ |

|

|

|

Переключение |

|

Qn 1 |

|||

Схема синхронного двухступенчатого D-триггера и его условнографическое обозначение приведены на рис. 2.14 а, б. Функционирование триггера задается таблицей 2.7.

Рис. 2.14. Схема синхронного двухступенчатого D-триггера и его условнографическое обозначение

Таблица 2.7

D |

C |

Q |

Режим |

n |

|||

х |

0 |

Q |

Хранение |

n-1 |

|||

1 |

↓ |

1 |

Запись 1 |

0 |

↓ |

0 |

Запись 0 |

Функционирование синхронного двухступенчатого JK-триггера задается таблицей 2.8. Работа JK-триггера аналогична RS-триггеру за исключением запрещенных состояний.

Построим функциональную схему JK-триггера на базе двухступенчатого RS-триггера (рис. 2.12,б). Для управления его входами разработаем комбинационное устройство.

|

|

|

|

|

|

Таблица 2.8 |

|

J |

K |

C |

Q n |

Режим |

|

||

х |

х |

0 |

Q n-1 |

Хранение |

|

||

0 |

0 |

х |

Q n-1 |

Хранение |

|

||

1 |

0 |

↓ |

1 |

|

Запись 1 |

|

|

0 |

1 |

↓ |

0 |

|

Запись 0 |

|

|

1 |

1 |

↓ |

|

|

|

Переключение |

|

Qn 1 |

|

||||||

Входными сигналами комбинационного устройства служат сигналы J, K (входные сигналы JK-триггера) и предыдущее состояние триггера Q n-1. Выходными сигналами являются S, R (входные сигналы RS-триггера).

По таблице 2.8 составим таблицу переключений 2.9 для функций S, R, исключив режимы хранения, поскольку они не изменяют состояние триггера.

23

|

|

|

|

|

Таблица 2.9 |

|

J |

K |

Q n-1 |

S |

R |

Режим |

|

1 |

0 |

0 |

1 |

0 |

Запись 1 |

|

0 |

1 |

1 |

0 |

1 |

Запись 0 |

|

1 |

1 |

0 |

1 |

0 |

Переключение 0 → 1 |

|

1 |

1 |

1 |

0 |

1 |

Переключение 1 → 0 |

|

Составим алгебраические уравнения в СДНФ для единичных значений функций S и R.

S J K Qn 1 J K Qn 1 J Qn 1 K K J Qn 1 ;

R J K Qn 1 J K Qn 1 K Qn 1 J J K Qn 1.

Функциональная схема триггера и его условно-графическое обозначение приведены на рис. 2.15 а, б.

Рис. 2.15. Функциональная схема JK-триггера и его условно-графическое обозначение

Синхронные JK-триггеры с динамическим управлением являются универсальными. Они широко используются в цифровой схемотехнике при реализации автоматов с памятью. Поэтому указанные триггеры наиболее полно представлены в различных сериях интегральных микросхем [1, 2].

В основе схемотехнических решений, используемых в микроэлектронной технике, заложена функциональная схема синхронного двухступенчатого JKтриггера. Но при разработке конкретных схем JK-триггеров использовались эвристические (интуитивные) методы оптимизации, направленные на повышение быстродействия и сокращение количества используемых компонентов. Кроме того, для расширения функциональных возможностей схемы JK-триггеров дополнены одним или двумя асинхронными входами S и R.

Для примера рассмотрим схему JK-триггера в интегральном исполнении[1]. Схема триггера 155ТВ1 и его условно-графическое обозначение приведены на рис.2.16а,б. Изменение состояний триггера задается таблицей

функционирования (табл. 2.10).

24

а) |

б) |

Рис. 2.16. Функциональная схема (а) и условно-графическое обозначение (б) JK-триггера 155ТВ1

Триггер JK является универсальным элементом при построении различных последовательностных устройств. В частности на его основе легко реализовать D- и T-триггеры. Функциональные схемы этих триггеров приведены на рис. 2.17.

Рис. 2.17. Функциональная схема T - и D –триггеров

Таблица 2.10

|

|

|

|

|

|

J |

K |

C |

Q n |

Режим |

||

|

S |

|

R |

|||||||||

|

0 |

|

1 |

х |

х |

х |

1 |

|

Асинхронная |

|||

|

|

|

запись 1 |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

0 |

х |

х |

х |

0 |

|

Асинхронная |

|||

|

|

|

запись 0 |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

|

0 |

х |

х |

х |

* |

|

Запрещенный |

|||

|

1 |

|

1 |

х |

х |

0 |

Q n-1 |

Хранение |

||||

|

1 |

|

1 |

0 |

0 |

х |

Q n-1 |

Хранение |

||||

|

1 |

|

1 |

1 |

0 |

↓ |

1 |

|

Запись 1 |

|||

|

1 |

|

1 |

0 |

1 |

↓ |

0 |

|

Запись 0 |

|||

|

1 |

|

1 |

1 |

1 |

↓ |

|

|

|

Переключение |

||

|

|

Qn 1 |

||||||||||

25

3. ФУНКЦИОНАЛЬНЫЕ УЗЛЫ ЦИФРОВЫХ УСТРОЙСТВ ПОСЛЕДОВАТЕЛЬНОСТНОГО ТИПА

3.1. Основы проектирования последовательностных функциональных

узлов

Как и автомат с памятью функциональный узел характеризуется вектором выходных сигналов (переменных) Y = {y1,.., yM} и вектором (совокупностью) состояний всех элементов памяти S = {s1,.., sK}. Значения этих величин на очередном (n-ом) интервале времени определяются функциональными зависимостями:

Yn = F(Sn-1, Xn); Sn = Ψ(Sn-1, Xn), |

(3.1) |

где n = 0,..,∞ – номер временного интервала; Sn-1 – вектор состояний элементов памяти на предыдущем временном интервале; Xn = {x1,.., xL} – вектор входных сигналов текущем временном интервале.

Переходы функционального узла из одного состояния в другое начинаются с исходного состояния S0, которое также характеризует данный автомат с памятью. Обобщенная структурная схема автомата с памятью приведена на рис. 3.1 [1].

Автоматы с памятью, в том числе функциональные узлы последовательностного типа, содержат элементы памяти и комбинационные схемы (цепи). Эти цепи формируют сигналы управления элементами памяти (b сигналов для одного элемента), обеспечивающие их переход в очередное состояние. Комбинационные схемы используются также для формирования выходных сигналов Y. Они реализуются на логических элементах, комбинационных функциональных узлах (мультиплексорах, дешифраторах и других), программируемых логических матрицах.

Рис. 3.1. Структурная схема цифровых автоматов

В зависимости от типов применяемых элементов памяти последовательностные функциональные узлы подразделяются на синхронные и асинхронные. Асинхронные узлы содержат меньше логических элементов, но обладают в среднем меньшим быстродействием по сравнению с синхронными последовательностными узлами. При проектировании асинхронных автоматов требуется учитывать время нахождения их в промежуточных состояниях в

26

процессе перехода в очередное устойчивое состояние. Асинхронные схемы используются в простейших функциональных узлах последовательностного типа.

В синхронных автоматах элементами памяти служат синхронные триггеры. Изменение состояния элементов памяти начинается одновременно по синхроимпульсу и завершается в течение одного такта. При этом каждое состояние автомата является устойчивым и переходные временные состояния не возникают. Синхронные схемы значительно проще в проектировании, и поэтому находят применение в функциональных узлах и последовательностных устройствах любой сложности.

Проектирование последовательностных устройств состоит из следующих процедур:

1.исходное описание функционирования в словесной и в формализованной форме в виде таблиц, формул, диаграмм состояний (графов переходов) и временных диаграмм;

2.кодирование состояний устройства;

3.разработка комбинационных устройств с использованием таблиц переходов, карт Карно и алгебраических преобразований;

4.составление функциональной схемы;

5.проверка работоспособности последовательностного устройства путем моделирования и (или) макетирования.

3.2. Счетчики и делители частоты

К счетчикам относятся последовательностные устройства, выполняющие функцию счета числа поступающих на его вход импульсов и фиксацию результата счета на N выходах. Процедуру счета следует рассматривать как переход счетчика из одного состояния в другое. Операциями счета может быть суммирование или вычитание, что соответствует изменению состояний счетчика в прямом направлении (от s1 до sK) или в обратном направлении (от sK до s1).

Счетчики принадлежат классу автоматов «Мура» (Рис. 1). В таких устройствах сигналы Y или отсутствуют и выходными служат сигналы состояния памяти, или сигналы Y не зависят от входных сигналов X (рис. 3.1). Функциональные выражения (1) приобретают вид:

Yn = F(Sn-1); Sn = Ψ(Sn-1, Xn). |

(3.2) |

Основной статической характеристикой счетчика является модуль или коэффициент счета КСЧ, равный числу состояний счетчика. Следует отметить, что соотношения между коэффициентом счета КСЧ, числом состояний S элементов памяти K и количеством элементов памяти N зависят от способа кодирования состояний S. Так при двоичном кодировании (для двоичных счетчиков) без запретных состояний выполняются соотношения:

КСЧ = K = 2N. |

(3.3) |

27

режим работы счетчика характеризуется двумя параметрами – временем установления очередного состояния Tуст и максимальной частотой входных счетных импульсов fmax.

Время Tуст определяется как интервал между моментом поступления активного уровня (активного изменения уровня) счетного импульса до момента завершения перехода всех элементов памяти в очередное состояние. Практически эта величина измеряется на уровне 0,1 от установившегося напряжения на выходе триггера с наибольшей задержкой.

Максимальная частота переключения определяется соотношением fmax = 1/2 Tуст.

Делители частоты выполняют функцию уменьшения частоты входных импульсов в целое число раз. Любой счетчик – суммирующий или вычитающий, может выполнять функцию деления частоты с коэффициентом деления, равным модулю счета КСЧ. В отличие от счетчиков в делителях частоты используется только один выход. Таким образом, делитель частоты можно рассматривать как один из способов использования счетчика. Поэтому в данном разделе будут рассматриваться только счетчики.

По способу изменения состояний элементов памяти (триггеров) счетчики подразделяются на синхронные и асинхронные.

По способу кодирования состояний различают двоичные, двоичнодесятичные счетчики, двоичные счетчики с заданными весовыми коэффициентами разрядов, счетчики с кодом «1 из N» и др.

По направлению счета различают суммирующие (прямого счета), вычитающие (обратного счета) и реверсивные счетчики.

В счетчиках, как и в любом автомате, элементами памяти могут служить триггеры любого типа. Но более простые схемы реализуются на базе синхронных JK- и T-триггеров с динамическим управлением.

3.2.1. Асинхронные счетчики

Асинхронные схемы используются для реализации более простых счетчиков.

Построим функциональную схему двоичного асинхронного счетчика без запрещенных состояний с КСЧ = K = 2N.

Для описания работы счетчика составим таблицу его состояний (табл. 3.1). Для определенности зададим число элементов памяти (количество разрядов) счетчика N = 4.

В первом столбце таблицы указан номер тактового импульса в десятичном коде, который соответствует номеру временного интервала n. В следующих четырех столбцах отображается последовательность двоичных кодов состояний счетчика для текущего временного интервала – Sn. Этот код определяется состоянием разрядов (элементов памяти) счетчика Q4,.., Q1. В последнем столбце приведены значения текущих состояний счетчика в десятичной системе счисления

k 4 |

2k 1 . |

(3.4) |

Sn k 1Qn,k |

||

|

|

28 |

Анализируя изменение состояния младшего разряда Q1, делаем вывод, что он может быть реализован на T-триггере. На вход этого триггера поступают тактовые импульсы, и он изменяет свое состояние при поступлении очередного импульса.

|

|

|

|

|

|

Таблица 3.1 |

|

n(10) |

|

|

sn |

|

Sn(10) |

|

|

Q4 |

Q3 |

|

Q2 |

Q1 |

|

||

|

|

|

|

||||

0 |

0 |

0 |

|

0 |

0 |

0 |

|

1 |

0 |

0 |

|

0 |

1 |

1 |

|

2 |

0 |

0 |

|

1 |

0 |

2 |

|

3 |

0 |

0 |

|

1 |

1 |

3 |

|

4 |

0 |

1 |

|

0 |

0 |

4 |

|

5 |

0 |

1 |

|

0 |

1 |

5 |

|

6 |

0 |

1 |

|

1 |

0 |

6 |

|

7 |

0 |

1 |

|

1 |

1 |

7 |

|

8 |

1 |

0 |

|

0 |

0 |

8 |

|

9 |

1 |

0 |

|

0 |

1 |

9 |

|

10 |

1 |

0 |

|

1 |

0 |

10 |

|

11 |

1 |

0 |

|

1 |

1 |

11 |

|

12 |

1 |

1 |

|

0 |

0 |

12 |

|

13 |

1 |

1 |

|

0 |

1 |

13 |

|

14 |

1 |

1 |

|

1 |

0 |

14 |

|

15 |

1 |

1 |

|

1 |

1 |

15 |

|

16 |

0 |

0 |

|

0 |

0 |

0 |

|

Изменения состояния разрядов Q2,.., Q4 в возрастающей синхронно последовательности состояний Sn происходит всякий раз при переходе предыдущих разрядов Q1,.., Q3 из 1 в 0. Отсюда следует, что все следующие за Q1 разряды могут быть выполнены на T-триггерах с динамическим управлением по отрицательному перепаду входного сигнала. При этом входным сигналом k-го разряда служит выходной сигнал Qk-1 предыдущего разряда. Применяя метод экстраполяции, получим функциональную схему суммирующего N-разрядного асинхронного счетчика (рис.3.2).

Рис. 3.2. Суммирующий счетчик

Изменения состояния разрядов Q2,.., Q4 в убывающей последовательности состояний sn происходит всякий раз при переходе предыдущих разрядов Q1,.., Q3 из 0 в 1. Отсюда следует, что все следующие за Q1 разряды могут быть

29

выполнены на T-триггерах с динамическим управлением по положительному перепаду входного сигнала. При этом входным сигналом k-го разряда служит выходной сигнал Qk-1 предыдущего разряда. Применяя метод экстраполяции, получим функциональную схему вычитающего N-разрядного асинхронного счетчика (рис. 3.3).

Рис. 3.3. Вычитающий счетчик

Построим функциональную схему двоичного асинхронного реверсивного счетчика с КСЧ = K = 2N. С целью упрощения комбинационной схемы управления будем использовать однотипные триггеры, например T-триггер с динамическим управлением по положительному перепаду входного сигнала.

Составим таблицу состояний счетчика (табл. 3.2), где состояния sn представлены инверсным (обратным) кодом состояний триггеров. Ограничимся значением N = 3.

Таблица 3.2

n(10) |

|

S’n |

|

Sn(10) |

|

Q’3 |

Q’2 |

Q’1 |

|||

|

|

||||

0 |

1 |

1 |

1 |

0 |

|

1 |

1 |

1 |

0 |

1 |

|

2 |

1 |

0 |

1 |

2 |

|

3 |

1 |

0 |

0 |

3 |

|

4 |

0 |

1 |

1 |

4 |

|

5 |

0 |

1 |

0 |

5 |

|

6 |

0 |

0 |

1 |

6 |

|

7 |

0 |

0 |

0 |

7 |

|

8 |

1 |

1 |

1 |

0 |

Изменения состояния разрядов Q2, Q3 в возрастающей последовательности состояний Sn происходит всякий раз при переходе предыдущих разрядов Q1,.., Q3 из 0 в 1. Отсюда следует, что все следующие за Q1 разряды могут быть выполнены на T-триггерах с динамическим управлением по положительному перепаду входного сигнала. При этом входным сигналом k-го разряда служит сигнал Q’k-1 с инверсного выхода предыдущего разряда. Применяя метод экстраполяции, получим функциональную схему суммирующего N-разрядного асинхронного счетчика (рис. 3.4).

Из сравнения рисунков 3, 4 можно легко построить функциональную схему реверсивного N-разрядного асинхронного счетчика (рис. 3.5), где комбинационная схема управления выполняет переключение прямых и инверсных выходов предыдущего триггера на вход последующего триггера.

30