- •Введение

- •1. Программа курса «Проектирование аналоговых устройств для 3d изделий»

- •1.1. Паспорт программы курса «Проектирование аналоговых устройств для 3d изделий»

- •1.2. Структура и примерное содержание учебного курса

- •1.3. Условия реализации программы курса

- •1.4. Контроль и оценка результатов освоения курса

- •Лекция № 2. Принципы аналогового схемотехнического моделирования

- •Лекция № 3. Параметры аналоговых устройств

- •Лекция № 4. Каскады на моп-транзисторах

- •Лекция № 5. Понятие топологии. Цели и задачи топологического проектирования

- •Лекция № 6. Библиотеки топологических элементов. Резисторы и конденсаторы

- •Лекция № 7. Моп-транзисторы. Биполярные транзисторы

- •Лекция № 8. Проектирование топологии аналоговых схем

- •3. Методические указания для проведения практических работ

- •3.1. Материалы для дистанционной формы обучения

- •Практическая работа № 1. Среда проектирования аналоговых устройств Cadence

- •Практическая работа № 2. Схемотехническое моделирование в симуляторе Spectre и UltraSim

- •Практическая работа № 3. Схемотехническое проектирование операционных усилителей

- •Практическая работа № 4. Топологическое проектирование аналогового устройства на примере операционного усилителя

- •4. Методические указания преподавателям, ведущим занятия по дисциплине

- •5. Методические указания по самостоятельной работе слушателей

- •6. Методические указания слушателям по изучению дисциплины

- •7. Цифровые образовательные ресурсы

- •8. Вопросы самопроверки

- •Заключение

- •Библиографический список

- •Оглавление

- •394026 Воронеж, Московский просп., 14

Лекция № 5. Понятие топологии. Цели и задачи топологического проектирования

Нормы проектирования

С усложнением процессов требовать от разработчика понимания всех деталей процесса изготовления и умения интерпретировать взаимосвязи между различными масками — это верный путь к неприятностям. Целью задания набора норм проектирования является обеспечение возможности легкого перевода концепции схемы на язык фактических геометрических структур в кремнии. Нормы проектирования выступают в роли интерфейса или даже контракта между разработчиком схемы и технологом.

Разработчики микросхем, как правило, стремятся к получению более плотноупакованной, меньшей по размеру разработки, поскольку это даст более высокое быстродействие и более высокую плотность интеграции. Технологи, напротив, хотят иметь воспроизводимый процесс с высоким значением процента выхода годных кристаллов. Следовательно, нормы проектирования представляют собой попытку добиться компромисса.

Нормы проектирования обеспечивают набор указаний для следования при проектировании различных масок, необходимых в процессах формирования рисунка. Они включают в себя ограничения и требования к минимальному размеру и минимальному расстоянию между объектами в пределах одного или в разных слоях.

Основной единицей в определении норм проектирования является минимальная ширина линии. Этот термин означает минимальный размер на фотошаблоне, который может быть надежно перенесен на полупроводниковый материал. В общем случае величина минимальной ширины линии определяется разрешающей способностью процесса формирования рисунка, который чаще всего основан на оптической литографии. В более совершенных подходах используются электронно-лучевые, рентгеновские источники и источники глубокого ультрафиолета, каждый из которых обеспечивает более высокое разрешение, но на текущий момент они менее привлекательны с экономической точки зрения.

Даже при одинаковом минимальном размере нормы проектирования обычно отличаются у различных компаний и процессов. Это превращает задачу переноса существующей разработки на другой процесс в весьма трудоемкую процедуру. Одним из подходов к решению этой проблемы является использование совершенных систем автоматизированного проектирования, которые позволяют осуществлять миграцию между совместимыми процессами. Другой подход заключается в использовании масштабируемых норм проектирования. Все нормы задаются в виде функции одного параметра, часто обозначаемого . Нормы выбираются таким образом, что разработка с легкостью переносится на весь срез промышленных процессов. Масштабирование минимального размера выполняется путем простого изменения значения параметра . Это приводит к линейному масштабированию всех размеров. Для данного процесса устанавливается конкретное значение , и все конструктивные размеры последовательно переводятся в абсолютные цифры. Обычно величина минимальной ширины линии для процесса устанавливается равной 2. Например, для 0,25-микронного процесса (т.е. для процесса с минимальной шириной линии 0,25 мкм) значение равно 0,125 мкм.

Данный подход, хотя и является привлекательным, имеет два недостатка.

1) Линейное масштабирование возможно только в ограниченном диапазоне размеров (например, в пределах от 0,25 до 0,18 мкм). При масштабировании в более широком диапазоне отношения между различными слоями обычно изменяются нелинейным образом, что не может быть адекватно отражено при линейном масштабировании норм.

2) Масштабируемые нормы проектирования консервативны: они отражают срез различных технологий и поэтому должны представлять нормы для наихудшего случая всего набора. Вследствие чего имеем завышение размеров и меньшую плотность интеграции разработки.

По этим и другим причинам в промышленности избегают пользоваться масштабируемыми нормами проектирования. Поскольку в промышленных разработках основной целью является плотность упаковки микросхемы, то большинство компаний, выпускающих полупроводниковые устройства, обычно используют нормы в микронах, когда нормы проектирования выражаются в абсолютных размерах и поэтому позволяют использовать особенности конкретного процесса в максимальной степени. Масштабирование и перенос разработки с одной технологии на другую при использовании подобных норм представляет собой более сложную задачу и должны выполняться либо вручную, либо с использованием развитых САПР.

Полный набор норм проектирования включает в себя следующие составляющие: набор слоев, отношения между объектами, принадлежащими одному слою, и отношения между объектами в различных слоях. Каждая из них будет рассмотрена по очереди.

Послойное представление

Концепция слоев позволяет перевести неудобоваримый язык комплекта фотошаблонов, использующихся в современном КМОП-процессе, на язык набора концептуальных уровней топологии, которые для разработчика схем значительно нагляднее. С точки зрения разработчика, все КМОП-схемы имеют в основе следующие элементы:

- Подложка и/или карманы, которые могут быть р-типа (для n-МОП-приборов) и n-типа (для р-МОП)

- Диффузионные, области (n+ и р+), которые задают области, где могут быть сформированы транзисторы. Эти области часто называют активными областями. Для создания контактов к карманам или к подложке необходима диффузия примесей разного типа. Такие области называются выборочными

- Один или несколько слоев поликремния, которые используются для создания электродов затворов транзисторов (но используются также и в качестве слоев системы межсоединений)

- Ряд слоев металла, которые используются для межсоединений

- Слои контактов и сквозных отверстий, которые обеспечивают соединение между слоями.

Топология представляет собой комбинацию многоугольников, каждый из которых относится к определенному слою. Функциональность схемы определяется выбором слоев и взаимодействием объектов, принадлежащих различным слоям. Например, МОП-транзистор образуется поперечным сечением диффузионного слоя и слоя поликремния. Межсоединение между двумя слоями металла формируется поперечным сечением двух слоев металла и дополнительным слоем контактов. Чтобы сделать эти связи более наглядными, каждому слою назначается стандартный цвет (или тип штриховки при черно-белом отображении).

Внутрислойные ограничения

Первый набор норм задает минимальные размеры объектов в каждом слое, а также минимальные расстояния между объектами в пределах одного слоя. Все расстояния выражаются в микронах.

Межслойные ограничения

Межслойные нормы обычно более сложные. Поскольку тут участвует несколько слоев, то представить их смысл и функциональное значение в наглядной форме труднее. Чтение топологии требует умения переводить двухмерную картину топологического чертежа в трехмерную структуру реального прибора. Это требует некоторой практики.

Приведем эти нормы в виде набора из трех отдельных групп.

1) Нормы проектирования транзистора. Транзистор формируется перекрытием слоя активных областей и слоя поликремния. Дополнительные нормы включают расстояние между активной областью и границей кармана, перекрытие затвором активной области и перекрытие активной областью затвора.

2) Нормы проектирования контактов и сквозных отверстий. Контакт (который обеспечивает межсоединение между металлом и активной областью или поликремнием) или сквозное отверстие (которое обеспечивает контакт между двумя металлами) формируется путем перекрытия двух соединяемых слоев и обеспечения между ними контактного отверстия, заполняемого металлом. При трассировке следует избегать лишних переходов между слоями межсоединений.

3) Нормы проектирования контактов к карманам и подложке. Чтобы микросхема была устойчивой к ошибкам, очень важно, чтобы карманы и подложка имели хорошее соединение с источником питания. Если этого не сделать, то может образоваться резистивный путь между контактом к подложке транзистора и шиной питания, что, в свою очередь, может привести к проявлению разрушительных паразитных эффектов, например эффекта защелки. Поэтому рекомендуется делать множество контактов к подложке (карману), которые были бы распределены по всей площади области. Для получения омического контакта между шиной питания, реализуемой в слое металла, и материалом р-типа необходимо сформировать диффузионную область р+-типа. Делается это с помощью выборочного слоя, который изменяет тип диффузии.

Верификация топологии

Фундаментальным требованием к процессу проектирования является обеспечение соблюдения всех без исключения норм проектирования. Если этого не делается, то практически всегда результатом будет нефункционирующая разработка. Но и выполнение этого требования для сложной микросхемы, которая может содержать миллионы транзисторов, - задача не из простых, особенно если принять во внимание сложность некоторых наборов норм проектирования. В прошлом целые коллективы разработчиков тратили часы, разглядывая чертежи топологии размером с комнату. Теперь большую часть этой работы выполняют компьютеры. На сегодня этап компьютерной проверки соблюдения норм проектирования является неотъемлемой частью цикла проектирования каждого передаваемого в производство кристалла ИС. Ряд инструментальных средств при проектировании топологии даже обеспечивает интерактивную проверку соблюдения норм в фоновом режиме непосредственно в процессе разработки концепции.

Основные понятия и определения процесса проектирования топологии

Топология ИС - множество геометрических фигур, расположенных в различных топологических слоях. Топологические слои объединяют фигуры, которые будут перенесены на один фотошаблон. Некоторое множество фигур в одном или в нескольких топологических слоях объединяются в топологическую группу. Топологическая группа кроме геометрических фигур может содержать в себе ссылки на другие группы, формируя иерархическое описание топологии ИС. Топологическая группа может включать фигуры (примитивы) следующих типов: ортогональный прямоугольник, многоугольник, шина, текст, линия и т.д. Примитивы первых трёх типов имеют замкнутый контур и формируют рисунок на фотошаблоне. Привязки групп могут быть двух типов - ячейки и итерации. Ячейка описывает единичную ссылку на группу. Итерация обеспечивает множественное обращение к ссылаемой группе в виде матрицы с заданным шагом и количеством повторений по осям координат.

Топологический чертёж является связующим звеном между проектировщиком и изготовителем ИС.

Проектирование топологии - процесс преобразования электрической или логической схемы в описание послойной реализации схемных компонентов (транзисторов, диодов, резисторов) и связей между ними в многослойной интегральной структуре. Должен быть известен типовой технологический процесс и заданы конструкторско-технологические требования (КТТ).

Верификация топологии включает в себя контроль проектных норм, экстракцию (восстановление) электрической схемы из описания топологии, сравнение с исходной схемой и средства анализа найденных нарушений.

Для воплощения схемотехнического решения в кремний требуется редактор топологии, средства размещения и трассировки блоков, контроль геометрических (DRC) и электрических (ERC) проектных норм, сравнение топологической реализации схемы с её исходным описанием (LVS).

Топологический редактор позволяет либо непосредственно строить топологию, либо формировать её из стандартных ячеек, содержащихся в библиотеке. Используя базу данных, редактор позволяет редактировать топологию ячеек в соответствии с конкретными требованиями.

После разработки топологии отдельных фрагментов с помощью соответствующей программы в диалоговом режиме осуществляется их размещение и трассировка межсоединений. После ввода описания топологии осуществляется ее верификация. Программа контроля проектных норм работает непосредственно с топологией. Контроль осуществляется автоматически по значениям КТТ (DRC-контроль) для используемой технологии (проверочный файл предоставляется заводом-изготовителем). Любые нарушения ограничений помечаются непосредственно на изображении топологии, выводимом на экран дисплея.

После завершения DRC-контроля программа восстановления электрической схемы (LVS) преобразует описание топологии в описание электрической схемы в виде таблицы цепей. Эта таблица передаётся в блок верификации логических и электрических схем, где проводится перекрёстная проверка описанной схемы на логическом и топологическом уровнях, а также повторное моделирование и верификация временных параметров. Таблица передаётся в программу контроля электрических проектных норм (ERC-контроль). Эта программа дополнительно использует ещё и значения параметров транзисторов, полученные при восстановлении электрической схемы из топологии. В результате её работы идентифицируются все нераспознанные или неправильно соединённые элементы, а также все нарушения электрических проектных норм.

Конечная информация (топология кристалла) записывается в формате GDSII и передаётся на завод-изготовитель. Завод изготавливает набор физических шаблонов и воплощает изделие в кремнии на своём оборудовании. Ответственность за функциональные характеристики ИС полностью лежит на разработчике ИС, в то время как завод гарантирует качество технологического процесса.

Пример топологии инвертора, выполненного по КМОП-технологии

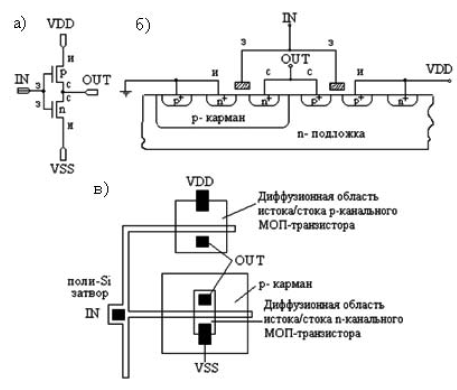

На рис. 2.22 представлены электрическая схема, структура и топология КМОП-инвертора.

Рис. 2.22. КМОП-инвертор: а) -принципиальная схема; б) -поперечное сечение; в) -топология инвертора с p-карманом; и - исток, з - затвор, с - сток, IN - вход, OUT – выход

Отличительной особенностью топологии КМОП-технологии от n-МОП технологии является наличие p-кармана. Эта область p-типа проводимости выступает в роли подложки для n-канального транзистора. Затворы n- и p-канального транзистора соединены между собой и представляют собой вход инвертора. Соединённые стоки обоих транзисторов являются выходом инвертора. Исток n-канального транзистора заводится на шину «земля», а исток p-канального транзистора на шину «питание».