- •Введение

- •1. Программа курса «Проектирование аналоговых устройств для 3d изделий»

- •1.1. Паспорт программы курса «Проектирование аналоговых устройств для 3d изделий»

- •1.2. Структура и примерное содержание учебного курса

- •1.3. Условия реализации программы курса

- •1.4. Контроль и оценка результатов освоения курса

- •Лекция № 2. Принципы аналогового схемотехнического моделирования

- •Лекция № 3. Параметры аналоговых устройств

- •Лекция № 4. Каскады на моп-транзисторах

- •Лекция № 5. Понятие топологии. Цели и задачи топологического проектирования

- •Лекция № 6. Библиотеки топологических элементов. Резисторы и конденсаторы

- •Лекция № 7. Моп-транзисторы. Биполярные транзисторы

- •Лекция № 8. Проектирование топологии аналоговых схем

- •3. Методические указания для проведения практических работ

- •3.1. Материалы для дистанционной формы обучения

- •Практическая работа № 1. Среда проектирования аналоговых устройств Cadence

- •Практическая работа № 2. Схемотехническое моделирование в симуляторе Spectre и UltraSim

- •Практическая работа № 3. Схемотехническое проектирование операционных усилителей

- •Практическая работа № 4. Топологическое проектирование аналогового устройства на примере операционного усилителя

- •4. Методические указания преподавателям, ведущим занятия по дисциплине

- •5. Методические указания по самостоятельной работе слушателей

- •6. Методические указания слушателям по изучению дисциплины

- •7. Цифровые образовательные ресурсы

- •8. Вопросы самопроверки

- •Заключение

- •Библиографический список

- •Оглавление

- •394026 Воронеж, Московский просп., 14

Практическая работа № 2. Схемотехническое моделирование в симуляторе Spectre и UltraSim

Цель работы: приобретение знаний по схемотехническому моделированию схем аналоговых устройств в САПР Cadence с применением симулятора Spectre и UltraSim. Научиться моделировать электрические схемы, используя симулятор Cadence® Virtuoso UltraSim и просматривать графические результаты в Cadence® SimVision, а также оценить скорость моделирования симулятора UltraSim и научиться определять наиболее эффективные средства моделирования для различных схем и задач.

Домашнее задание и методические указания по его выполнению

В последние годы интенсивно начали развиваться программы моделирования нового поколения, так называемые «быстрые симуляторы». Их применение дает качественный скачок в производительности. Появилась возможность моделировать БИС объемом в десятки и сотни миллионов узлов с точностью и требованиями к вычислительным ресурсам, близкими к традиционным программам моделирования (рис. 3.15).

Рис. 3.15. Возможности систем моделирования различных поколений

Решение, предлагаемое Cadence на данном сегменте рынка, - платформа Virtuoso и система FastSPICE Ultrasim. Наряду с известными системами моделирования Ultrasim интегрирован в общую среду разработки Virtuoso и дает возможность быстро получить решение с приемлемой точностью при возрастании сложности проекта на несколько порядков.

Технические требования к аналоговым, заказным цифровым, радиотехническим и смешанным проектам росли экспоненциально в последнее десятилетие (рис. 3.16). Экономические факторы и конкуренция на рынке электроники вынуждают разработчиков применять новые технологии и объединять прежде независимые блоки на одном кристалле (System-On-Chip, SOC). Многие производители переходят на современные технологии проектирования по нормам 0.13 мкм – 65 нм и совмещают аналоговое проектирование с нанометровыми цифровыми дизайнами. Более того, основой цифрового проектирования является использование библиотек стандартных и специализированных заказных блоков, разрабатываемых с применением средств аналогового моделирования.

Рис. 3.16. Взаимосвязь технологии, сложности и стоимости проекта

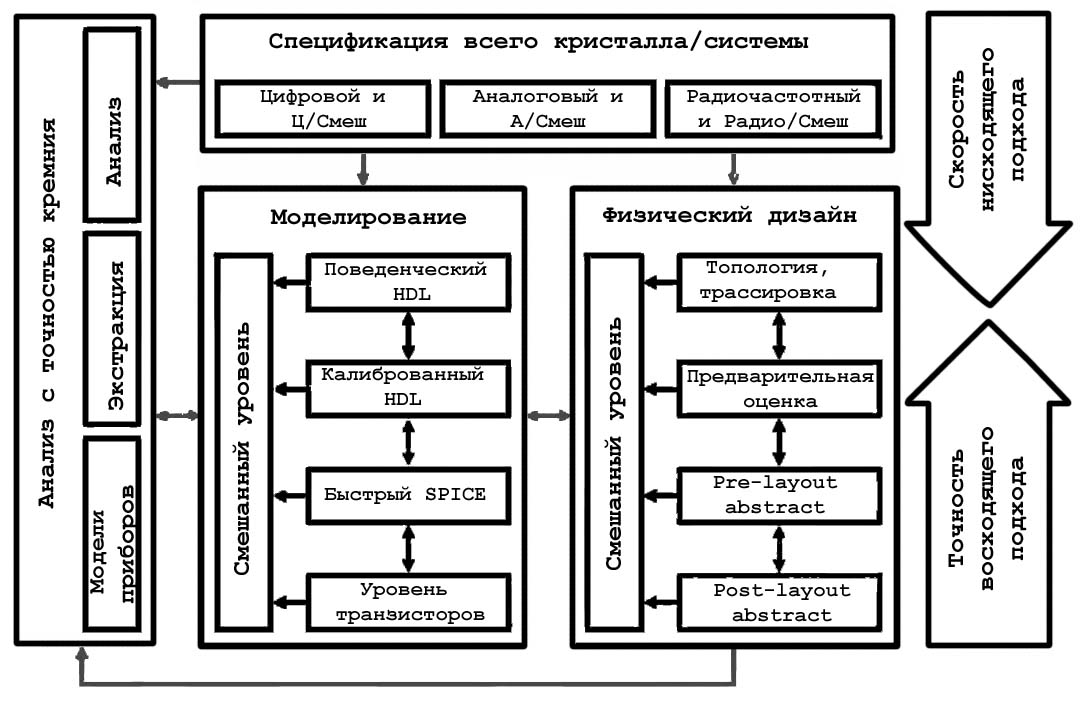

Сложность, объем современных проектов и новые физические эффекты требуют соответствующих технологий заказного проектирования, объединяющих возможности быстрого нисходящего (top-down) проектирования с точностью восходящего (bottom-up) проектирования, идущего от кремниевой реализации. Meet-in-the-middle – современная методология, сочетающая в себе скорость и точность (рис. 3.17).

Наиболее передовые разработчики уже активно используют методологию Meet-in-the-middle. Однако ее эффективность сильно ограничена неадекватностью средств проектирования.

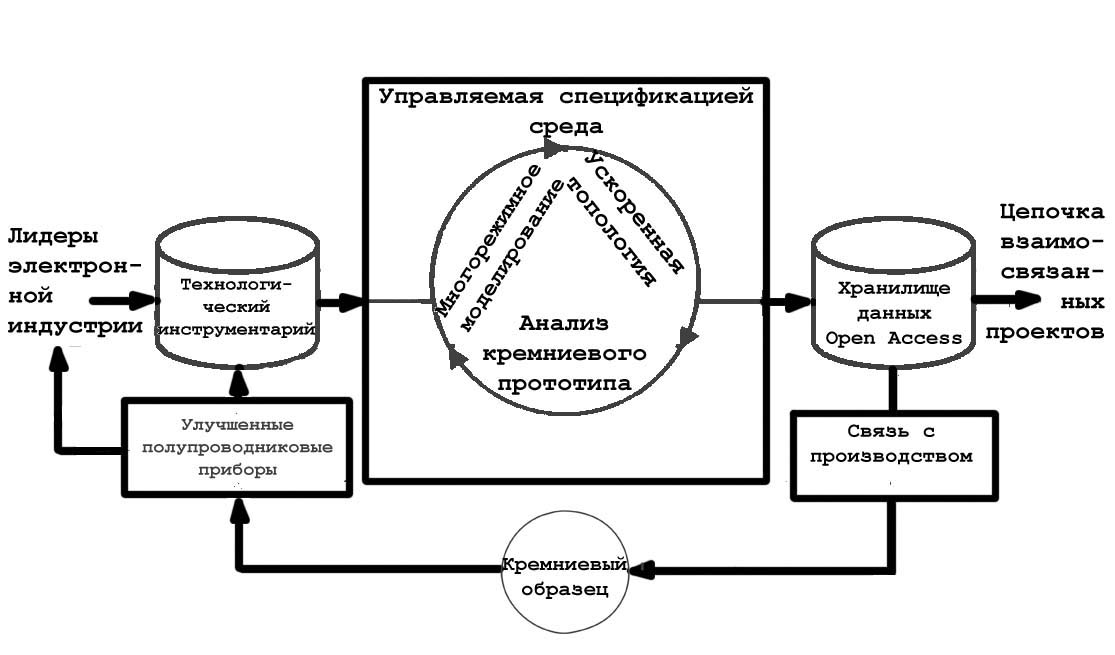

Платформа для заказного проектирования Virtuoso является понятной системой для быстрого и точного проектирования, оптимизированной для технологии meet-in-the-middle (рис. 3.18), например, Analog Custom Design (ACD).

Рис. 3.17. Метод проектирования Meet-in-the-middle

Рис. 3.18. Процесс проектирования с помощью платформы Vittuoso

В Virtuoso входит среда, определяемая спецификацией, многорежимное моделирование, имеющее общий синтаксис, модели и системы уравнений, значительно ускоренные слои и объединенная на уровне всего кристалла, а также среда смешанного моделирования.

Virtuoso поддерживает моделирование с использованием различных уровней абстракции моделей - от чисто поведенческого на верхнем системном уровне до точных, откалиброванных по экспериментальным данным на нижнем, наиболее детальном уровне. Уровни абстракции физического дизайна меняются от оценочных на ранних стадиях, до финальных трассировки и экстракции. Кремниевый анализ, основанный на расширенных моделях полупроводниковых приборов, прецизионной экстракции и средствах анализа, дает адекватную информацию в течение всего процесса проектирования.

В зависимости от сложности и объема решаемых задач Vittuoso ADE (Analog Design Environment) может интегрировать различные системы аналогового моделирования (Spice, Spectre, UltraSim, Multi-mode Simulation), обепечивать обратную аннотацию паразитных параметров, экстрагируемых с помощью Assura RC, поддерживать кросс-пробинг между схемным вводом (Virtuoso Schematic Editor), топологическим редактором (Virtuoso Layout Editor) и системой анализа результатов моделирования.

Платформа Virtuoso может работать с базой данных Cadence CDBA или с базой OpenAccess. С этой платформой возможно быстрое проектирование с высоким выходом годных для геометрий от 1 мкм до 90 нм и менее.

Система моделирования Virtuoso Spectre

Virtuoso® Spectre® - это современная система аналогового моделирования, использующая прямые методы моделирования на уровне дифференциальных уравнений. Функциональные возможности Spectre и SPICE во многом сходны. Spectre и SPICE в основе используют одни и те же базовые алгоритмы, – такие как неявные методы интегрирования, метод Ньютона или матричные методы решения систем уравнений, – но реализация алгоритмов в Spectre существенно отличается. Таким образом, Spectre имеет ряд преимуществ по сравнению со SPICE. Среди них:

- способность решать системы большей размерности вследствие более эффективного распределения памяти и более эффективных алгоритмов; более высокая точность как результат применения ряда продвинутых моделей полупроводниковых приборов, среди них – BSIM3v3, MOS0, MOS 9, EKV, BTA-HVMOS, BTA-SOI, VBIC95, TOM2, HBT и другие;

- модели сохранения заряда;

- улучшенный анализ Фурье;

- лучший метод контроля погрешности (ошибки округления lte и 1-й закон Кирхгофа);

- адаптивный алгоритм управления шагом интегрирования;

- методы анализа радиотехнических схем (PSS, PAC, PXF, Pnoise, Pdisto);

- смешанное аналого-цифровое моделирование совместно с Verilog-XL – легко моделируются десятки тысяч транзисторов в аналоговой части и десятки тысяч логических элементов в цифровой.

Система моделирования Virtuoso UltraSim

Virtuoso® UltraSim® - это современная высокоскоростная система, предназначенная для моделирования схем объемом в десятки и сотни миллионов узлов и позволяющая, в том числе, моделировать цифровые БИС на аналоговом уровне с учетом экстрагированных паразитных RC параметров.

Основные характеристики системы моделирования UltraSim:

- эффективные алгоритмы моделирования для технологии pre- и post-layout, для аналогового и смешанного моделирования, устройств памяти и цифровых схем с точностью, близкой к SPICE, со значительным ускорением по сравнению со SPICE и практически неограниченными объемами для иерархических проектов;

- поддерживаются форматы Spectre и HSPICE, язык Verilog-A, форматы postlayout - detailed standard parasitic format (DSPF), standard parasitic exchange format (SPEF), а также язык Verilog®;

- поддержка формата digital vector file, Verilog® форматы - value change dump (VCD) и extended VCD (EVCD);

- форматы SignalScan Turbo 2 (SST2), fast signal database (FSDB), parameter storage format (PSF) и семейство форматов для сохранения сигналов WDF;

- продвинутые алгоритмы RC-редукции для моделирования post-layout;

- поддержка всех основных моделей транзисторов Spectre и HSPICE, включая BSIM3, BSIM4, BSIMSOI, TFT, HVMOS, BJT, Mextram, Hicum, VBIC и модель ячеек памяти flash;

- проверки времени установления и удержания, времени нарастания и спада, а также ширины импульса;

- анализ мощности на уровне элемента, подсхемы и всего кристалла;

- проверки на уровнях проекта и приборов, в том числе проверка напряжений на приборе, высокоимпедансный анализ узлов, анализ утечек по постоянному току и подробные проверки токов;

- анализ шума, отслеживающий эффекты voltage overshoot (VO) и voltage undershoot (VU) в узлах;

- моделирование IR drop;

- быстрый анализ по огибающей для высокопроизводительного анализа переходных процессов в радиотехнических схемах;

- анализ надежности, в том числе hot carrier degradation (HCI), negative bias temperature instability (NBTI), моделирование старения, совместимость с командами Virtuoso RelXpert;

- С-интерфейс для макромоделирования UCI для реализации аналоговых или цифровых макромоделей, например PLL, блоков памяти, ADC/DAС;

- интерфейс для расчета надежности URI для реализации специфических моделей надежности;

- интерфейс UWI для разработки специальных форматов выходных данных.

Математический аппарат UltraSim используется со следующими инструментами Cadence:

- AMSUltra для Verilog/VHDL - совместного моделирования с NCSIM;

- UltraSimVerilog для смешанного аналого-цифрового моделирования с VerilogXL;

- аналоговая опция VoltageStorm (VAVO) для анализа цепей питания аналоговых и смешанных схем;

- аналоговая опция ElectronStorm (VAEO) для анализа электромиграции аналоговых и смешанных схем;

- VoltageStorm для анализа цепей питания цифровых схем и анализа всего дизайна.

В рамках платформы Virtuoso UltraSim тесно интегрируется с существующими системами. Цель интеграции - предоставление пользователю стандартных вычислительных блоков на выбор, в зависимости от характера схемы, ресурсов и требований.

Унификация интерфейсов Ultrasim и Spectre – CMI, UWI, SFE, ...

Общая тестовая регрессия – более 7000 тестов.

Общие модели полупроводниковых приборов, поддержка CMI. Новая версия, CMI 4.0.

Система UltraSim проходит тестирование на тех же тестах, поддерживает все режимы и последовательности среды проектирования Virtuoso.

С использованием современной FastSPICE технологии Virtuoso UltraSim система моделирования позволяет выполнять высокопроизводительное, аналоговое или смешанное моделирование всей системы. Поддержка многих языков описания объектов обеспечивает независимость языка и уровня абстракции в методологии проектирования. Обобщенная реализация полупроводниковых приборов в системах моделирования, входящих в платформу Virtuoso, гарантирует высокую точность результатов. С учетом RC-редукции с помощью UltraSim и Virtuoso стало возможным решение ранее недоступных задач полной и точной верификации проекта после фазы разработки топологии на нанометровых технологиях.

Контрольные вопросы к домашнему заданию

1. Что такое система на кристалле ?

2. В чем различие между нисходящим (top-down) и восходящим (bottom-up) проектированиями ?

3. В чем суть метода проектирования Meet-in-the-middle ?

4. Какие уровни абстракции моделей и уровни абстракции физического дизайна существуют ?

5. В чем различие между системами моделирования Virtuoso Spectre и Virtuoso UltraSim ? В каких случаях надо применять одну или другую систему моделирования ?

Лабораторно-практические задания и методические указания по их выполнению

Это учебное руководство предполагает, что Вы знакомы с форматом SPICE и основными командами UNIX, Ваша среда настроена так, чтобы было возможным выполнение моделирования в системе Virtuoso Spectre, Virtuoso UltraSim, и Вы имеете учетную запись на учебном компьютере.

Схемотехническое моделирование в симуляторе Spectre

Для подключения симулятора в САПР Cadence необходимо проделать следующие операции.

1) В окне Composer Schematic выбрать: меню Tools → Analog Environmen.

2) В окне ADE выбрать: меню Setup → Simulator/Directory/Host… В появившемся окне необходимо выбрать симулятор «spectre» (рис. 3.19).

Рис. 3.19. Выбор симулятора

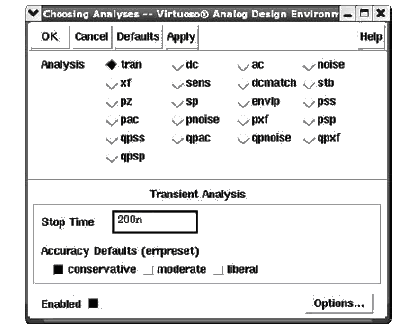

В окне ADE доступны различные опции моделирования. В этой лабораторной работе выполняется временное моделирование, для этого необходимо задать тип анализа tran (меню Analyses →Choose…) и все необходимые параметры и точность моделирования, переменные (меню Variables → Edit…), отображаемые на графике выводы (рис. 3.20).

Рис. 3.20. Окно установки типа анализа

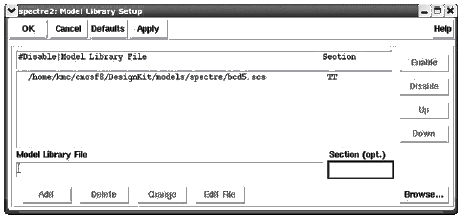

В меню Setup → Model Libraries… устанавливают файл моделей и используемые секции этого файла (рис. 3.21).

Рис. 3.21. Окно установки математических моделей

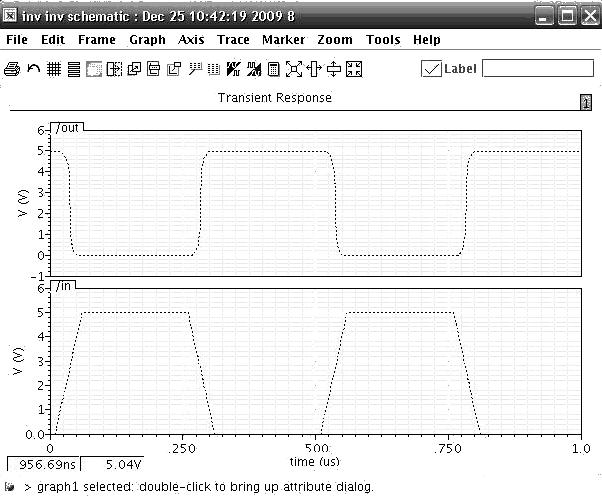

Запуск моделирования осуществляется через меню Simulation → Netlist and Run. После окончания моделирования появится окно с результатами (рис. 3.22).

Рис. 3.22. Окно с результатами моделирования

Схемотехническое моделирование в симуляторе UltraSim

Копирование файлов примера

1) Найдите корневой каталог Cadence, введя

cds_root ultrasim.

Система выведет на экран корневой каталог.

2) Определите местоположение учебного каталога, введя

ls cds_root_dir/tools/ultrasim/examples.

3) Скопируйте учебный каталог в свою домашнюю директорию.

4) Проверьте, что следующие подкаталоги находятся в текущем каталоге: inv_mea/, ultrasim_workshop/, usim_ade/, Usim_Verilog/.

Подкаталог ultrasim_workshop содержит mult16_vcd, mult16_vec, и sram16k. В данной лабораторной работе будут рассмотрены примеры из папок inv_mea и ultrasim_workshop, в которых работа с UltraSim ведется в консольном режиме из терминала UNIX. Рекомендуется самостоятельно изучить возможности Virtuoso UltraSim при работе с ADE (папка usim_ade), а также при работе с моделями, описанными на языке Verilog (папка Usim_Verilog).

Начало работы в Virtuoso UltraSim и SimVision.

Перейдите в каталог inv_mea. Откройте inv_mea.sp. more inv_mea.sp

Это моделирование нетлиста КМОП инвертора с .alter парметрами для различных входных длительностей фронта сигнала и емкостей выходной нагрузки.

Примечание: следующие SPICE-параметры используются во входном файле: .title, .options, .include, .param, .global, .subckt, .ends, .tran, .probe, .meas, .alter, и .end.

Выполните моделирование, используя средство моделирования Virtuoso UltraSim.

ultrasim inv_mea.sp

В терминале ведется журнал моделирования.

Примечание: журнал моделирования может быть сохранен в файле, используйте для этого inv_mea.out.

Следующие файлы были сгенерированы для этого нетлиста:

inv_mea.trn: графический файл в формате sst2;

inv_mea.1.trn: первый .alter графический файл в формате sst2;

inv_mea.2.trn: второй .alter графический файл в формате sst2;

inv_mea.meas0: подробный измерительный файл отчета;

inv_mea.meas1: первый .alter детализированный измерительный файл отчета;

inv_mea.meas2: второй .alter детализированный измерительный файл отчета;

inv_mea.mt0: упрощенный измерительный файл отчета;

inv_mea.mt1: первый .alter упрощенный измерительный файл отчета;

inv_mea.mt2: второй .alter упрощенный измерительный файл отчета;

Проверьте измеренные результаты.

more inv_mea.mt

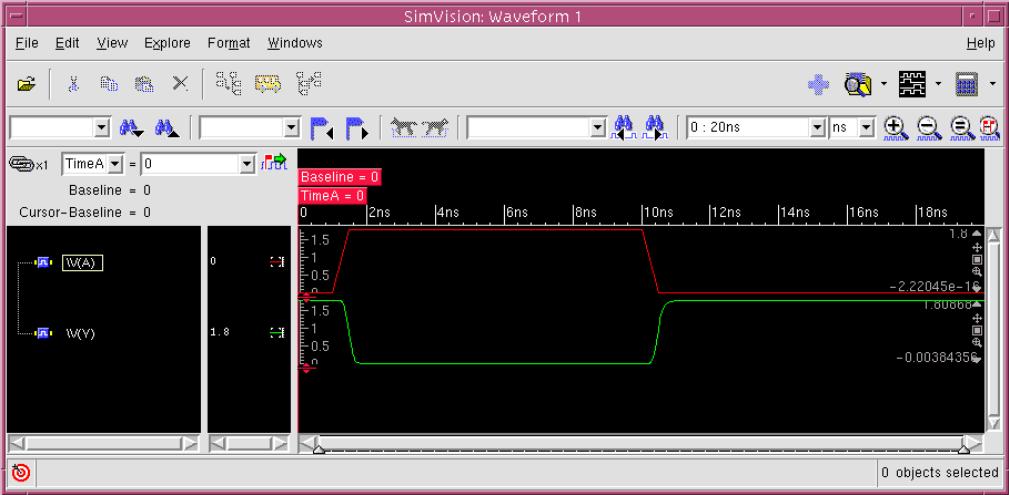

2. Проверка графических результатов в SimVision для файлов *.trn

Запустите средство просмотра графических файлов SimVision.

simvision&

Появится окно браузера проекта SimVision. Откройте базу данных графиков, выбирая File – Open Database. Появится открытое окно базы данных. Выберите inv_mea.trn. Кликните Open. Выберите сигналы из базы данных.

Появится окно вывода графических результатов, которое должно выглядеть подобно рис. 3.23.

Выйдете из SimVision, выбрав File – Exit. Появится диалоговое окно выхода из SimVision. Нажмите кнопку Yes.

Рис. 3.23. Окно результатов моделирования inv_mea.sp.

Использование цифрового векторного файла

Разработчик может определять входные векторы и будущие выходные векторы внутри цифрового векторного файла. Симулятор Virtuoso UltraSim преобразовывает входные векторы в PWL источника напряжения и проверяет результаты симуляции с выходными векторами.

Измените текущую директорию на mult16_vec в каталоге примера.

cd ~/ultrasim_tutorial/mult16_vec Откройте mult16.net.

more mult16.net

Умножитель состоит из двух входных регистров, массива умножителя и выходного регистра. Он имеет два 16-разрядных входа (A[15:0], B [15:0]), вход тактовой частоты (CLK) и 32-разрядный выход (P [31:0]).

Откройте mult16_vec.vec.

more mult16_vec.vec

Несколько первых строк определяют свойства векторных сигналов. Основание определяет число битов в векторном формате, io определяет направления (ввод или вывод) сигналов, vname определяет сигнальные имена. tunit представляет единицу измерения времени. trise и tfall – входные времена нарастания и спада. vih, vil, voh и vol определяют входное высокое напряжение, входное низкое напряжение, выходное высокое напряжение и выходное низкое напряжение соответственно.

Примечание: первые два выходных вектора ‘xxxxxxxx”. Результат умножения первых входных векторов – это третий выходной вектор.

Откройте mult16_vec.sp.

more mult16_vec.sp

Обратите внимание на .vec, .lprobe параметры и подстановочный знак (*), используемый в парметрах .lprobe. Векторный файл вызывают с .vec параметром. Логический зонд (.lprobe) используется, чтобы уменьшить размер графического файла.

Выполните моделирование, используя средство моделирования Virtuoso UltraSim.

ultrasim mult16_vec.sp > mult16_vec.out &

Ожидайте, пока идет моделирование.

Просмотрите вектор проверки результатов.

more mult16_vec.veclog

Все выводы (P <31> ~ P <0>) должны быть корректными.

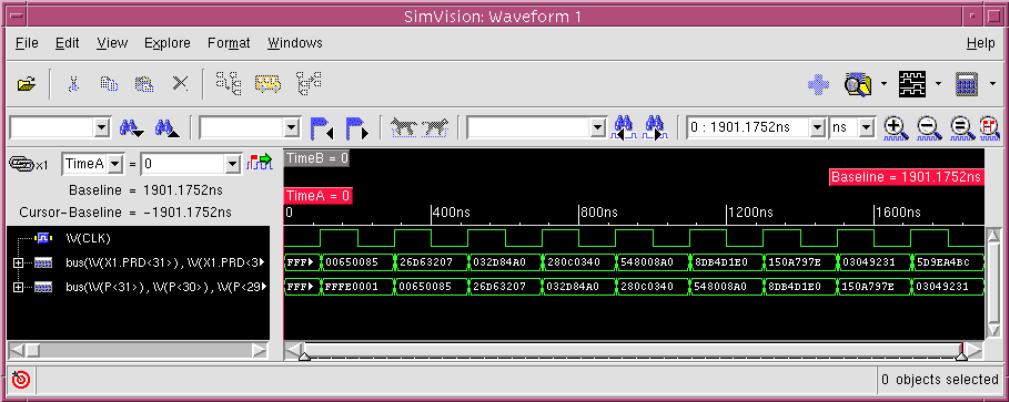

Проверка графиков в SimVision для файлов *.sv

Запустите средство просмотра графических результатов моделирования.

simvision&

Появляется окно браузера проектов SimVision.

Откройте базу данных графиков с ранее сохраненным сценарием команд, выберите File – Source Command Script.

В окне выбора командного файла SimVision выберите simvison.sv файл.

Кликните Open.

Появится окно графиков (рис. 3.24).

Рис. 3.24. Графики результатов моделирования файла mult16_vec.sp.

Выйдите из SimVision, выберите File – Exit.

Появится диалоговое окно выхода из SimVision.

Нажмите кнопку Yes.

Моделирование умножителя с более высокими тактовыми частотами

Увеличьте тактовую частоту в 10 раз и наблюдайте, как работает схема, для этого выполните следующие шаги.

Создайте новые входной и векторный файлы

cp mult16_vec.sp speed.sp

cp mult16_vec.vec speed.vec.

Сделайте следующие изменения в speed.sp, используя текстовый редактор:

From .vec ‘mult16_vec.vec’ to vec ‘speed.vec’

VCK CLK 0 PULSE (0 2.5 100n 1n 1n 99n 200n) to

VCK CLK 0 PULSE (0 2.5 10n 1n 1n 9n 20n)

.tran 10p 200n to .tran 10p 200n

Произведите следующее изменение в speed.vec с помощью текстового редактора:

tunit ns to tunit 0.1ns

Выполните моделирование, используя средство моделирования Virtuoso UltraSim.

ultrasim speed.sp > speed.out &

Ожидайте, пока идет моделирование.

Просмотрите вектор проверки результатов.

more speed.veclog

Использование файла дампа изменений значений

Средство моделирования Virtuoso UltraSim может взять файл дампа изменений значения (VCD) в качестве входных стимулов и ожидаемых выходов. Файл VCD обычно генерируется средством моделирования Verilog.

Примечание: средство моделирования также поддерживает улучшенный VCD (EVCD), цифровой ввод стимулов (обратитесь к секции “Verilog Value Change Dump Stimuli” в Virtuoso UltraSim Simulator User Guide для получения дополнительной информации).

Измените текущую директорию на mult16_vcd в каталоге примера.

cd ~/ultrasim_tutorial/mult16_vcd

Откройте mult16_vcd.vcd.

more mult16_vcd.vcd

Файл VCD был сгенерирован Verilog-XL. Отметьте, что шкала времени определена как 10 пс, это также единица измерения времени для файла информации о сигнале VCD.

Откройте vcd_info.

more vcd_info

Информационный файл VCD преобразовывает нотацию шины [] в файле VCD к <> в SPICE нетлисте. Таким образом, определяются контекст, вводы, выводы и сигнальные свойства.

Откройте mult16_vcd.sp.

more mult16_vcd.sp

Обратите внимание на строку в файле, содержащую .vcd параметр.

Выполните моделирование, используя средство моделирования Virtuoso UltraSim.

ultrasim mult16_vcd.sp > mult16_vcd.out &

Ожидайте, пока идет моделирование.

Просмотрите вектор проверки результатов.

more mult16_vcd.veclog

Все выводы (P <31> ~ P <0>) должны быть корректными.

Выполнение фонового моделирования для 16 K SRAM

Измените текущий каталог на sram16k.

cd ~/ultrasim_tutorial/sram16k

Откройте sram16k.net.

more sram16k.net

Схема SRAM имеет:

1024x16-бит ячейки памяти;

10-разрядный ввод адреса (A<9:0>);

16-разрядный ввод данных (DI <15:0>);

16-разрядный вывод данных (DO <15:0>);

вход пре-заряда (PRE) и управление записью-чтением (WR, 1 = запись, 0 = чтение).

Откройте sram16k.sp.

more sram16k.sp

Примечание: режим моделирования установлен в фоновый (hier = 0). Векторный файл sram16k.vec обеспечивает входные стимулы и ожидаемые выходные значения. В общей сложности 32 цикла записи и цикла чтения моделируются с временем окончания 3200 нс.

Выполните моделирование, используя средство моделирования Virtuoso UltraSim.

ultrasim sram16k.sp > sram16k.out &

Ожидайте, пока идет моделирование.

Просмотрите вектор проверки результатов.

more sram16k.veclog

Все выводы (DO <15> ~ DO <0>) должны быть корректными.

Проверьте процессорное время и использование памяти.

more sram16k.out

Полное процессорное время и использование памяти могут быть найдены в конце файла. Записаны следующие строки:

CPU time usage

Maximum memory usage

Выполнение иерархического моделирования для 16 K SRAM.

Создайте новый входной файл.

cp sram16k.sp sram16k_hier.sp

Чтобы переключиться из фонового режима в иерархический режим, произведите следующее изменение в sram16k_hier.sp, используя текстовый редактор.

From .usim_opt hier=0 to .usim_opt hier=1

Выполните моделирование, используя средство моделирования Virtuoso UltraSim.

ultrasim sram16k_hier.sp > sram16k_hier.out &

Ожидайте, пока идет моделирование.

Просмотрите вектор проверки результатов.

more sram16k_hier.veclog

Все выводы (DO <15> ~ DO <0>) должны быть корректными.

Проверьте полное процессорное время и использование памяти.

more sram16k_hier.out

Полное процессорное время и использование памяти могут быть найдены в конце файла. Записаны следующие строки:

CPU time usage;

Maximum memory usage.

Ответьте на следующие вопросы.

1. Насколько быстрее иерархический режим, чем фоновый режим ?

2. Насколько меньше памяти используется в иерархическом режиме ?